目录

1.算法仿真效果

2.算法涉及理论知识概要

2.1 PPM调制解调原理

2.2 基于FPGA的PPM系统实现

3.Verilog核心程序

4.完整算法代码文件获得

1.算法仿真效果

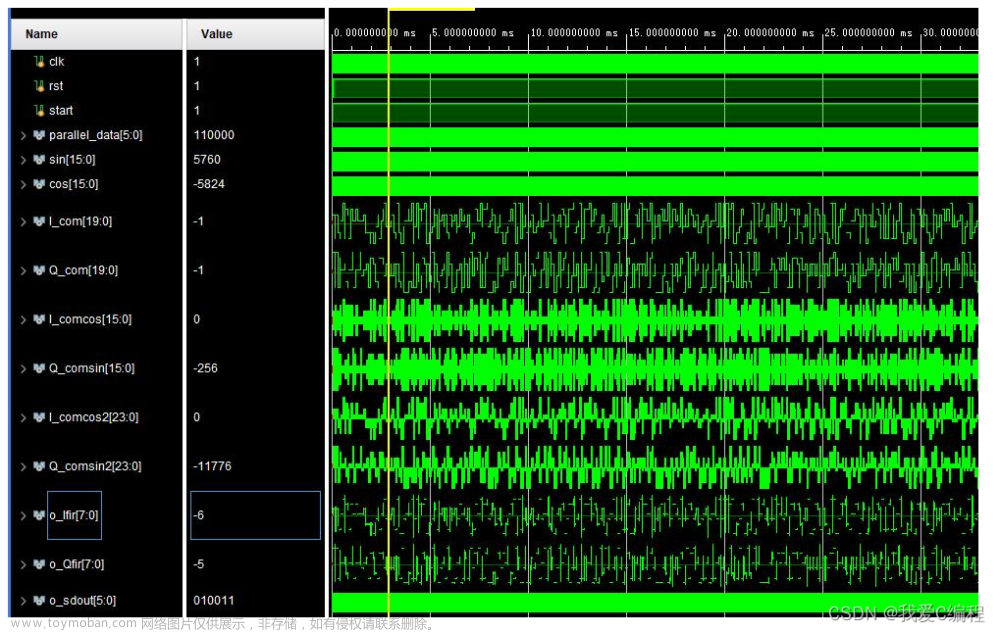

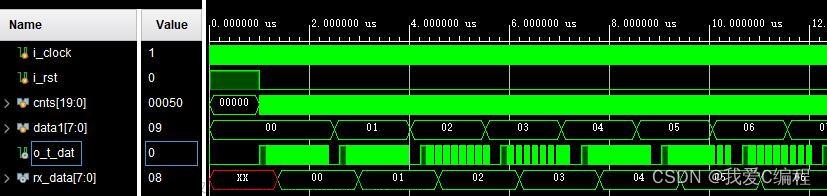

vivado2019.2仿真结果如下:

2.算法涉及理论知识概要

基于FPGA的PPM(脉冲位置调制)光学脉位调制解调系统是一个复杂的电子与光电子相结合的通信系统。

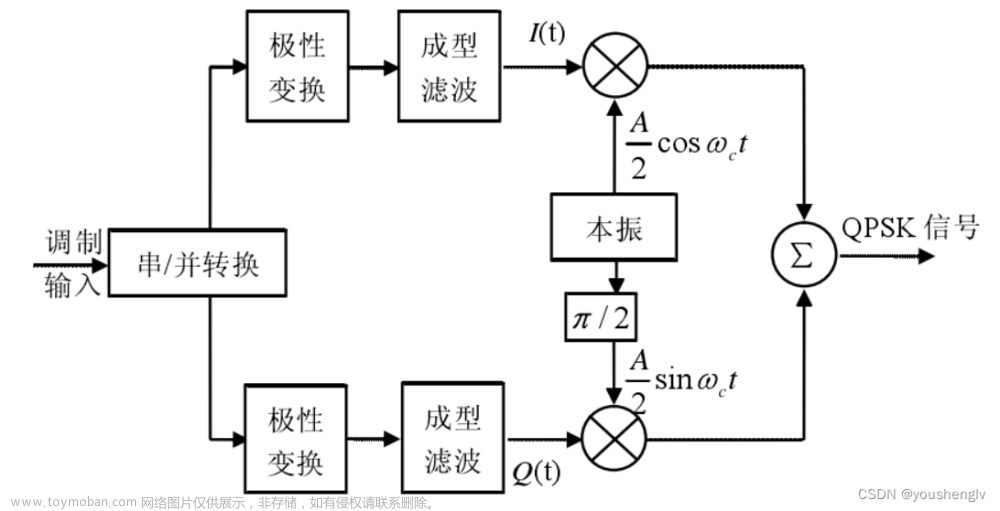

2.1 PPM调制解调原理

脉冲相位调制(PPM)最早由Pierce提出并应用于空间通信,是利用脉冲的相对位置来传递信息的一种调制方式。在光通信中,这种调制方式可以以最小的光平均功率达到最高的数据传输速率。PPM的优点在于:它仅需根据数据符号控制脉冲位置,不需要进行极性和脉冲幅度的控制,便于以较低的复杂度实现调制与解调,PPM特别适用于室内计算机红外线通信和对潜通信等要求低平均功率传输信息的场合。PPM信号调制广泛应用于超宽带移动通信、光通信等现代通信前沿技术领域。PPM信号的调制和接收对通信系统的性能起很大作用。

在PPM中,一个时间窗口被分成等长的N个时隙,脉冲可以在其中的任何一个时隙内出现。假设一个PPM符号的持续时间为(T),并且被分为(N)个等长的时隙,每个时隙的持续时间为(T_s),则(T = N \times T_s)。对于一个给定的信息比特序列,我们可以将其映射到一个特定的脉冲位置。例如,对于4-PPM((N=4)),比特序列“00”可以映射到第一个时隙的脉冲,“01”映射到第二个时隙,以此类推。

PPM解调的目标是从接收到的信号中恢复出原始的脉冲位置,从而还原出传输的信息。相关解调是一种常用的PPM解调方法。其基本原理是将接收到的信号与本地生成的参考信号进行相关运算,通过观察相关峰的位置来判断脉冲的位置。

2.2 基于FPGA的PPM系统实现

基于FPGA的PPM系统通常包括以下几个主要部分:

PPM调制器:根据输入的比特序列生成对应的PPM信号。这通常涉及到查找表(LUT)或算法逻辑来实现比特到脉冲位置的映射。

相关器:在接收端实现相关运算,用于检测PPM信号中的脉冲位置。相关器需要高精度的时序控制和数据处理能力。

同步模块:确保发送和接收端的符号同步,这是准确解调的关键。通常采用帧同步来实现。

数字信号处理(DSP)模块:用于优化信号质量,如滤波器设计、噪声抑制等。文章来源:https://www.toymoban.com/news/detail-771544.html

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/12/21 16:01:10

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module test();

reg i_clock;

reg i_rst;

initial

begin

i_clock=1'b1;

i_rst=1'b1;

#1000;

i_rst=1'b0;

end

always #5 i_clock=~i_clock;

reg[19:0]cnts;

always@(posedge i_clock or posedge i_rst)

begin

if(i_rst)begin //同步复位

cnts <= 20'd0;

end

else begin

if(cnts==151)

cnts <= 16'd1;

else

cnts <= cnts + 16'd1;

end

end

reg[7:0]data1;

always@(posedge i_clock or posedge i_rst)

begin

if(i_rst)begin //同步复位

data1<=8'd0;

end

else begin

if(cnts==151)

data1<=data1 + 8'd1;

else

data1<=data1;

end

end

wire o_t_dat;

TPPM TPPM_u1(

.i_clock (i_clock),//100MHz,input

.i_rst (i_rst),//input

.i_din (data1), //input [7:0]

.o_t_dat (o_t_dat),//output reg

.o_t_en ()//output reg

);

wire[7:0]rx_data;

RPPM RPPM_u1( //ppm解调模块

//时钟和复位

.i_clock (i_clock),//100MHz,input

.i_rst (i_rst),//input

.i_t_dat (o_t_dat),//input

//输入的数据和有效信号

.o_dout (rx_data), //output [7:0]

.o_en ()

//ppm输入信号

);

endmodule

00_054m4.完整算法代码文件获得

V文章来源地址https://www.toymoban.com/news/detail-771544.html

到了这里,关于m基于FPGA的PPM光学脉位调制解调系统verilog实现,包含testbench的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!