专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

文章来源:https://www.toymoban.com/news/detail-771893.html

文章来源地址https://www.toymoban.com/news/detail-771893.html

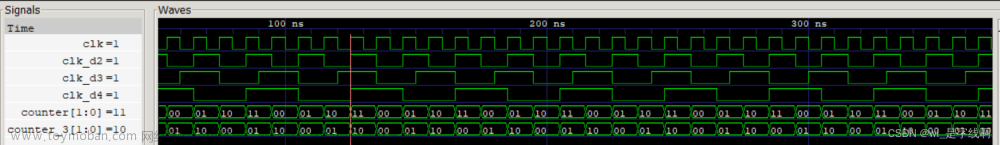

`timescale 1ns/1ns

module even_div

(

input wire rst ,

input wire clk_in,

output wire clk_out2,

output wire clk_out4,

output wire clk_out8

);

//*************code***********//

reg out2, out4, out8 ;

always @ (posedge clk_in or negedge rst) begin

if (~rst) out2 <= 'd0 ;

else out2 <= ~out2 ;

end

always @ (posedge clk_out2 or negedge rst) begin

if (~rst) out4 <= 'd0 ;

else out4 <= ~out4 ;

end

always @ (posedge clk_out4 or negedge rst) begin

if (~rst) out8 <= 'd0 ;

else out8 <= ~out8 ;

end

assign clk_out2 = out2 ;

assign clk_out4 = out4 ;

assign clk_out8 = out8 ;

//*************code***********//

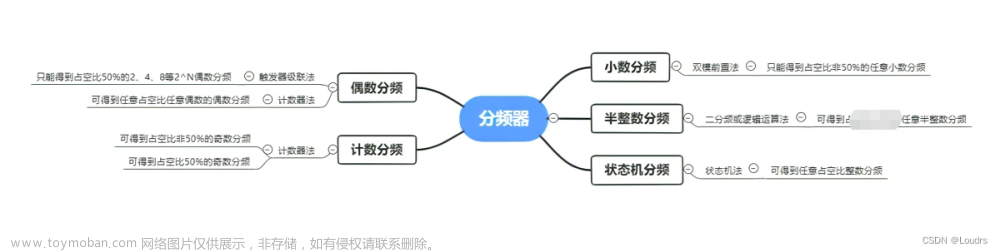

endmodule到了这里,关于「Verilog学习笔记」时钟分频(偶数)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!