请阅读【ARM Coresight SoC-400/SoC-600 专栏导读】

下篇文章:ARM Coresight 系列文章 2 - ARM Coresight 介绍

1.1 ARM Debug 概述

在过去的系统中,开发人员可能使用昂贵的硬件工具,如逻辑分析仪或示波器来观察程序的行为。但现代处理器是一个复杂的SOC,通常包含内存、缓存、和许多其他逻辑单元。可能没有芯片外可见的处理器信号,因此无法通过连接逻辑分析器(或类似的)来监控行为。因此ARM系统通常包括专门的硬件,以提供广泛的控制和观察设施的调试。经常遇到的debug方式有以下几种:

- external debug;

- self-hosted debug;

- invasive debug;

- non-invasive debug;

- semihosting debug。

下面会分别进行介绍。

1.1.1 External debug

外部调试是指调试器位于Target 外部。例如,主机通过调试器连接独立开发板上的Armv8-A处理器,这就是外部调试。外部调试的另一个示例是一个调试器运行在一个处理器上,调试位于同一SoC上的另一个处理器。

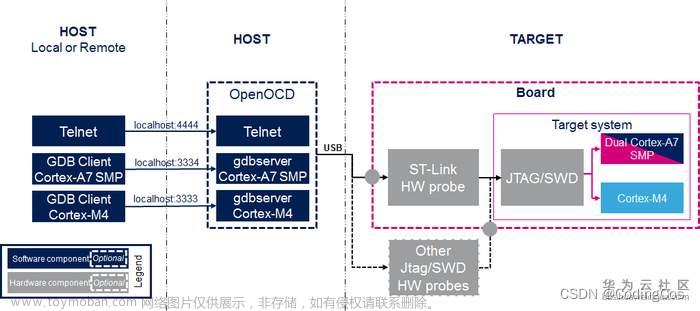

外部调试通常在进行芯片验证和bringup时使用。通常,外部调试依赖于正在调试的Target上的物理连接器,例如JTAG或Serial Wire debug (SWD)。外部调试还需要在Target和运行调试器的主机之间连接一个调试探针probe。

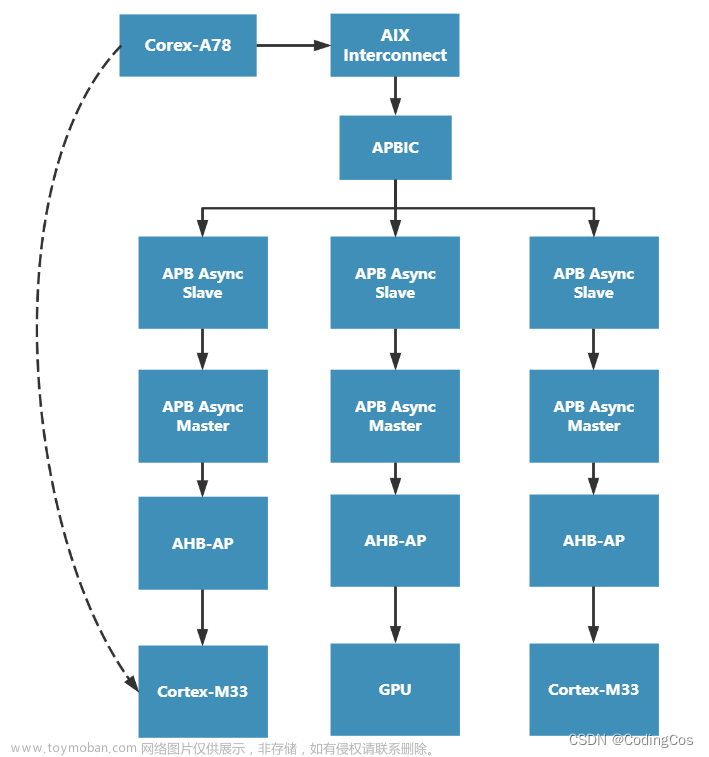

下图显示了调试探针在主机和调试目标之间的连接关系:

1.1.2 Self-hosted debug

当调试器和被调试的软件在同一个处理器上运行时,就会发生Self-hosted debug。gdbserver 就是一个很好的例子,它用于Linux应用程序调试。Gdbserver 是一个程序,它与Linux应用程序一起运行,并允许像GDB或Arm调试器这样的调试环境来调试应用程序。

自调试通常用于调试在操作系统下运行的应用程序,或者在物理调试连接器不可用时使用。

1.1.3 Invasive debug

侵入式调试会修改处理器的状态。例如,当使用调试器设置断点时,处理器会在命中断点时停止。侵入式的调试主要有:

- 停机以及单步执行程序

- 硬件断点

- 断点指令(BKPT)

- 数据观察点,作用于单一地址、一个范围的地址,以及数据的值。

- 访问寄存器的值(既包括读,也包括写)

- 调试监视器异常

- 基于 ROM 的调试(闪存地址重载(flash patching) )

通常,使用侵入式调试技术引入的细微变化不会影响程序的执行。但是,一些 bug,例如与时间相关的问题,可能对这些细微的更改非常敏感。这意味着侵入式调试技术不适合此类bug。

1.1.4 Non-invasive debug

相对于侵入式调试,非侵入式调试始终不会修改处理器状态。例如,生成和收集trace数据通常不会影响处理器,所以trace被归类为非侵入式调试。其他非侵入式调试操作还有:

- PMU和采样PC指针;

- 软件跟踪(通过 ITM(指令跟踪单元));

1.1.5 Semihosting debug

半宿主是一种机制,使在嵌入式系统(也称为目标)上运行的代码能够与主机的I/O通信并使用主机的I/O,例如键盘输入和显示输出等。其实最简单的就是在host PC侧使用串口工具进入显示和命令输入。

1.2 Target 连接

1.2.1 Debugger 连接失败常见情况

-

Is Core PowerDown

Debugger连不上下电状态的core。如果target是SMP系统,包含bootcode、firmware、os等软件阶段,当用不到某些core时,这些软件可能会让这些core处于下电状态,那么在这种情况下debugger是连不上core的debug逻辑部分的。 -

Is Core Reset

Debugger连不上复位状态的core。在如果某些core还没有被master core解复位的话,debugger也是控制不了core的。 -

Different security state

ARMv8 v9是支持安全和非安全状态的。如果安全态被硬件lock,那么debugger是访问不了的。 -

Different exception level

如果 EL3 的exception level被 lock 住,debugger 也是访问不了的。

1.2.2 Target 与 Debugger 连接注意事项

一些target需要特殊步骤才能建立debug连接。这时候就要问设计者或者用户手册来寻找建立debugger连接的前置条件。下面是一些可能的通用操作:

- 上电并且解复位core(Powering up or taking a core or processor out of reset);

- 一些设计者会增加开关来开启debug功能(Unlocking scan chains or devices);

- 一些设计者可能会通过跳帽来控制GPIO作为debug引脚(Multiplexed signals);

- 一些设计者仅提供了连线,没有预留debug口(Missing connectors)。

1.3 Debug Event

在 Coretex-M 中,用于debug 目的而触发的事件叫做 debug event:

debug event 的触发可以导致以下事件的发生:

- 进入 Debug state,如果Halting debug 功能使能之后,debug event 可以 halt processor 在 debug state 状态下,通过设置

DHCSR.C_DEBUGEN位可以使能 halting debug 功能。 - 当halting debug 功能被关闭的情况下,可以触发 DebugMonitor 中断,可以通过设置

DHCSR.C_DEBUGEN位为0来关闭 halting debug 功能,或者通过来通过debug 认证接口来关闭 halting debug 功能, DebugMonitor exception 需要通过配置DEMCR.MON_EN为1,才能使能。

1.3.1 debug event 分类

| Event 触发原因 | 异常支持的功能 | DFSR bit | Notes |

|---|---|---|---|

| Internal halt request | Halt and DebugMonitor | HALTED | Step command, processor halt request, and similar |

| Breakpoint | Halt and DebugMonitor | BKPT | Breakpoint from BKPT instruction or match in FPB |

| Watchpoint | Halt and DebugMonitor | DWTTRAP | Watchpoint match in DWT, including PC match watchpoint |

| Vector catch | Halt only | VCATCH | One or more DEMCR.VC_* bits set to 1, and the processor took the corresponding exception |

| External | Halt and DebugMonitor | EXTERNAL | External Debug Request asserted |

| FPB的指令断点匹配 | Halt and DebugMonitor | For Cortex-M3 |

1.3.2 debug mode

在 Cortex-M 中的调试操作模式分为两种:

- 第一种称为“halt”(停机模式),在进入此模式时,处理器完全停止程序的执行。

- 第二种则称为“debug monitor exception”(调试监视器模式),此时处理器执行相应的调试监视器异常服务例程,由它来执行调试任务,并且依然允许更高优先级的异常抢占它。调试监视器的异常号为 12,优先级可编程。除了调试事件可以触发异常外,手工设置其悬起位也可以触发本异常。

1.4 断点类型

ARM 提供了多种类型的断点,包括硬件断点、软件断点和数据断点。

-

硬件断点(hardware breakpoint)是由处理器内部的调试逻辑实现的,比如 FPB中的比较器可以配置一些寄存器来监视PC的地址。当执行到被监视的地址或满足条件时,处理器会触发硬件断点中断。但是硬件断点的数量通常有限。

-

软件断点(software breakpoint)是通过在代码中插入特殊的指令来实现的。当执行到该指令时,处理器会触发断点中断。软件断点的数量通常没有明确限制,但在实际使用中可能会受到处理器性能和调试工具的限制。ARM 中常用断点指令:

- 在 T32 (ARM的16位指令集架构,也被称为Thumb-2)中 breakpoint instruction 也是

BKPT #<immediate> - 在 A32 (ARM的32位指令集架构,也被称为ARMv7-A)中 breakpoint instruction 是

BKPT #<immediate> - 在 A64 (ARM的64位指令集架构)中 breakpoint instruction 是

BRK #<immediate>

- 在 T32 (ARM的16位指令集架构,也被称为Thumb-2)中 breakpoint instruction 也是

ARM CoreSight 还支持多种断点条件和触发条件的设置,以满足不同的调试需求。例如,可以设置断点只在特定的处理器核心上触发,或者只在特定的条件满足时触发。

1.4.1 断点指令 BKPT 介绍

以 Cortex-M 为例,断点指令的格式为 BKPT #im8,它是一个16位的 Thumb指令,编码为0xBExx——其低8位就是指令中#im8的值。

当该指令执行时,会产生一个调试事件。当 C_DBGEN 置位时可以用于喊停处理器内核;或者当调试监视器使能时,触发调试监视器异常。对于后者,因为调试监视器异常也是一种优先级可编程的普通异常,所以也可以因为其优先级不够高而不能立即响应。可见,因为 NMI 和硬 fault 的优先级总是比它的高,所以不能在它们的服务例程中使用 BKPT 指令来启动调试——只有在它们返回时才能响应调试监视器异常。

使用 BKPT 时另一个要注意的是,当调试监视器异常返回后,它返回到的是 BKPT 指令的地址,而不是返回 BKPT 后面一条指令的地址。这与常规的异常返回是不同的,原因在于,在正常情况下使用 BKPT 指令时, BKPT用于取代一条正常的指令,并且当命中了该断点而执行了调试动作后,把该BKPT指令所占用的内存恢复为先前被BKPT取代的指令,并且让该指令是下一条即将执行的指令,而其它的部分不受影响(这其实也是软件断点的实现方式)。

如果在BKPT指令执行时却发现 C_DEBUGEN 和 MON_EN 都为0,则会因为无法进入调试而上访成硬fault,并且把硬 fault 状态寄存器(HFSR)的 DEBUGEVT 位给置 1,同时在调试fault状态寄存器(DFSR)中的 BKPT 位也置1。如果程序存储器的值不能更改,则可以通过编程FPB来产生硬件断点。但是,只支持6个指令地址和两个文字地址。

1.4.2 断点指令 BRK 介绍

在PE执行完 BRK 指令之后将会触发一个 Breakpoint Instruction exception,在 异常症状寄存器 ESR 中会记录异常的一些信息,比如记录是 BRK 指令还是 BKPT指令导致的 断点异常,记录 BRK/BKPT 指令后的立即数到 ESR.ISS的 bit[15:0] 中。

至于为何要记录 BRK/BKPT 指令后的立即数,是因为在实际的应用中可以根据立即数来区分不同的场景。比如linux/arch/arm64/include/asm/brk-imm.h 中定义了下面一些立即数来表示了不同功能的BRK指令。

/*

* #imm16 values used for BRK instruction generation

* 0x004: for installing kprobes

* 0x005: for installing uprobes

* 0x006: for kprobe software single-step

* Allowed values for kgdb are 0x400 - 0x7ff

* 0x100: for triggering a fault on purpose (reserved)

* 0x400: for dynamic BRK instruction

* 0x401: for compile time BRK instruction

* 0x800: kernel-mode BUG() and WARN() traps

* 0x9xx: tag-based KASAN trap (allowed values 0x900 - 0x9ff)

*/

#define KPROBES_BRK_IMM 0x004

#define UPROBES_BRK_IMM 0x005

#define KPROBES_BRK_SS_IMM 0x006

#define FAULT_BRK_IMM 0x100

#define KGDB_DYN_DBG_BRK_IMM 0x400

#define KGDB_COMPILED_DBG_BRK_IMM 0x401

#define BUG_BRK_IMM 0x800

#define KASAN_BRK_IMM 0x900

#define KASAN_BRK_MASK 0x0ff

1.4.3 FPB( Flash Patch and Breakpoint )

FPB 有两项功能:

- 把代码地址空间中对指令或字面值(literal data)的加载,重载到SRAM的地址空间中。

- 硬件断点支持。产生一个断点事件,从而使处理器进入调试模式(停机或调试监视器异常)

在实现FPB的时候可以将其配置为提供 4-8个比较器。可以单独的将某一个比较器配置为返回 一条BKPT指令给 processor 当指令地址发生匹配的时候。通过这种方式来提供 硬件断点的功能。FPB 模块包含一个全局使能配置和各个比较器单独使能配置。

Cortex-M7 中 FPB 的寄存器表如下:

a. If four instruction comparators are implemented.

b. If eight instruction comparators are implemented.

c. For FP_COMP0 to FP_COMP7, bit 0 is reset to 0. Other bits in these registers are not reset.

1.4.3.1 Flash Patch Comparator Registers

用这个寄存器存放和PC地址比较的值,该寄存器的功能定义如下:

文章来源:https://www.toymoban.com/news/detail-772173.html

文章来源:https://www.toymoban.com/news/detail-772173.html

下篇文章:ARM Coresight 系列文章 2 - ARM Coresight 介绍文章来源地址https://www.toymoban.com/news/detail-772173.html

到了这里,关于【ARM Coresight Debug 系列 1 -- ARM Debug 技术概述】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!