一、组合逻辑、时序逻辑的适用场合

1、时序逻辑 和组合逻辑

组合逻辑:

-

组合逻辑是一类逻辑电路,其输出仅仅取决于当前的输入信号状态,而不考虑过去的信号状态。

-

组合逻辑电路的输出完全由输入决定,没有时钟信号的概念,因此输出是输入的函数。

-

例子包括逻辑门(AND、OR、NOT等)和其他不带存储元件(如触发器)的电路。

时序逻辑:

-

时序逻辑是一类逻辑电路,其输出不仅取决于当前的输入信号状态,还受到时钟信号和过去的输入信号状态的影响。

-

时序逻辑包括时钟触发器(flip-flops)和时钟触发器之间的互连,以及时序逻辑电路,如寄存器、计数器等。

-

时序逻辑考虑了时间的概念,通常在时钟信号的上升沿或下降沿触发,因此可以用来存储信息和实现状态机等功能。

总体而言,组合逻辑处理无状态的逻辑功能,而时序逻辑引入了状态和时钟信号,使得电路能够存储和处理有状态的信息,从而实现更复杂的功能和控制。在硬件描述语言(如Verilog和VHDL)中,

通过 always @ (*) 表达式通常表示组合逻辑,

而 always @(posedge clock) 表达式表示时序逻辑。

2、何时使用:

-

带有反馈(直接反馈、间接反馈)的必须用时序逻辑

(反馈:输出拉回到输入即为反馈,如 assign cnt = cnt + 1; assign flag = ~flag;没有时序控制 就会出现无限反馈)

//错误示例

always @ (flag) begin

if (flag == 1'b1)

cnt = cnt + 1'b1;

else

cnt = cnt;

end这个代码会出现的问题就是 没有时序控制 会出现无限反馈 我们无法知道cnt加了多少次

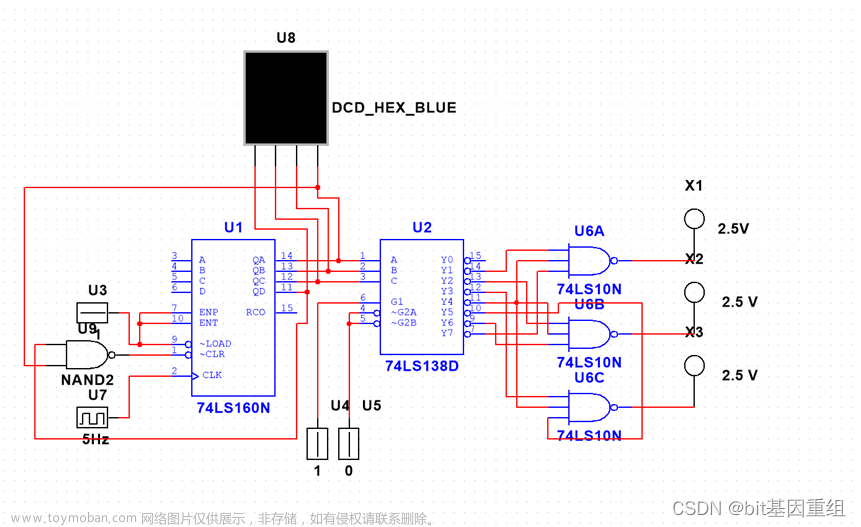

等效电路如下

文章来源:https://www.toymoban.com/news/detail-773168.html

文章来源:https://www.toymoban.com/news/detail-773168.html

-

根据时序对齐关系进行选择:

这里就很经典了 之前写牛客题目的时候颇有感受!(最近没写牛客题目,到组合逻辑 利用门电路进行经典组合逻辑的编写,有点折磨!) -

根据运行速度进行选择:

就是如果一个组合逻辑很长 延时很大 我们可以通过在中间加入寄存器实现传输速度的增加

文章来源地址https://www.toymoban.com/news/detail-773168.html

文章来源地址https://www.toymoban.com/news/detail-773168.html

二、数字逻辑电路的时序分析

1、FPGA真实结构:基于SRAM(静态存储器)(掉电丢失)的FPGA 即为LUT(查找表)一般是4/5/6输入

产生随机的0、1序列的方法 (妙啊)同理可以产生0-2、0-3、0-4......

产生随机的0、1序列的方法 (妙啊)同理可以产生0-2、0-3、0-4......

2、组合逻辑产生延时 导致时序逻辑出错

3、时序分析(时序约束):

-

建立时间(setup time、Tsu):在采样(时钟上升沿)之前,数据要保持不变的最小时间;(由器件本身特性决定)

-

时间裕量:在时钟上升延前保持不变的时间I(一般认为<1个时钟周期)-Tsu;

-

保持时间(hold time、Th):在在采样(时钟上升沿)之后,数据要保持不变的最小时间;(由器件本身特性决定)

-

建立时间或保持时间不足就会出现亚稳态

4、单拍系统:

5、建立时间的分析模型

-

悲观移除( 共同路径悲观去除):去除clock path上相同路径的悲观计算量

-

多角度分析:根据PVT分析 温度越低、电压越高 延迟越小(利用此特点进行快模型、慢模型时序仿真,无论快慢模型 都要满足时序约束(建立时间、保持时间))

-

定义:在一片wafer(晶圆)上,不可能每点的载流子平均漂移速度都是一样的,随着电压、温度不同,它们的特性也会不同,把他们分类就有了PVT(Process,Voltage,Temperature)

-

性能影响:

7、亚稳态的缓解:亚稳态无法彻底消除,只能缓解。

-

1.降低时序逻辑延迟:如采用流水线、重定时技术;

-

2.降低寄存器延迟:使用反应更加迅速的寄存器;

-

3.降低时钟频率,增大时钟周期;

-

4.复位电路采用异步复位同步释放;

-

5:数据在跨时钟域传输中,可以采用两级缓存、握手信号、异步FIFO等方法缓解。

到了这里,关于组合逻辑、时序逻辑的适用场合、数字逻辑电路的时序分析的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!