鱼弦:CSDN内容合伙人、CSDN新星导师、全栈领域创作新星创作者 、51CTO(Top红人+专家博主) 、github开源爱好者(go-zero源码二次开发、游戏后端架构 https://github.com/Peakchen)

文章来源:https://www.toymoban.com/news/detail-773238.html

文章来源:https://www.toymoban.com/news/detail-773238.html

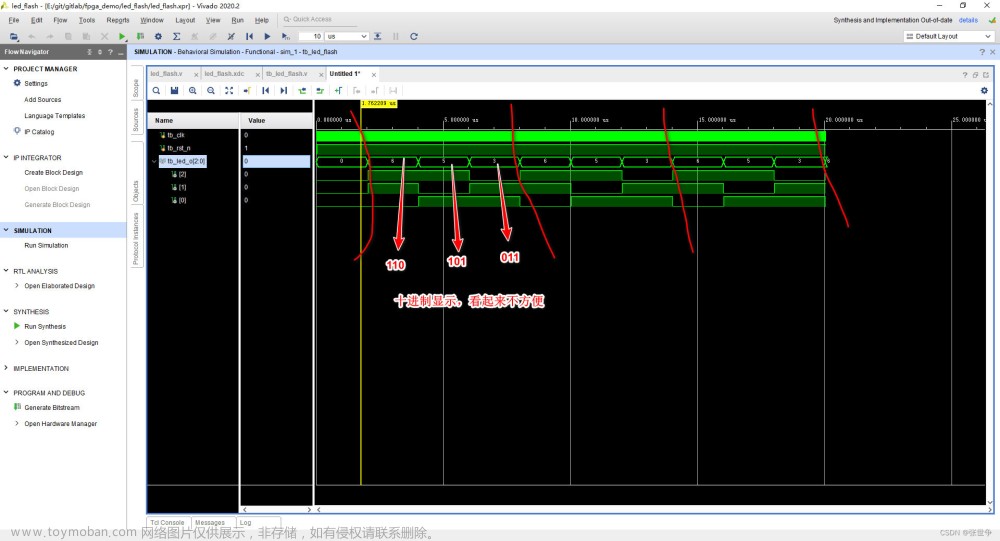

题目:二进制转BCD码的电路设计

一、设计要求

利用上海安路科技的EG4X20BG256板卡上面的资源(4个按键、4个Led、4个七段数码管)实现二进制到几类BCD码的转换和显示。

该FPGA板卡如下图所示,所用到的资源见不同颜色的圈。

(1)板卡上,4个七段数码管如红圈所示;4个LED如绿圈所示,按照从左至右的方向,其编号为:LEd1、LeD2、Led3、lED4;4个按键如黄圈所示,从左至右依次为RESET、KeY1、Key2、kEY3。

(2)各部分功能分配

按键:LED灯亮/灭控制

leD:亮或者灭

数码管:显示转换后的BCD码

(3)功能要求

按键与LeD控制:通过按下不同按键,控制对应的led的亮/灭,其中RESET对应Led1,KEY1对应leD2,以此类推。

控制规则:按键每按下一次,LED状态翻转一次(从1变为0,或者从0变为1,即亮灭转换)。其中LED亮表示输入二进制为1,LED灭文章来源地址https://www.toymoban.com/news/detail-773238.html

到了这里,关于fpga开发:二进制转BCD码的电路设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[FPGA]用Verilog写一个简单三位二进制加法器和减法器](https://imgs.yssmx.com/Uploads/2024/02/761556-1.png)