在电子通信技术日益发展的时代潮流下,直接式(DFS)和锁相式(PLL)已经不能满足生活和科研方面对于频率技术的需求。经过科研人员的不断攻坚下,直接数字频率合成器(DDS)应运而生。它现在广泛运用于移动通信、电子雷达、航天等方面。本次设计主要通过FPGA模块+单片机最小系统实现对数字信号、模拟信号的控制和输出功能,并基于此原理完成信号发生器的软件、硬件设计。

第一章 方案分析与系统设计

1.1 设计方案选型与分析

方案1:采用Qualcomm公司生产的DDS集成芯片Q2368设计信号发生器。该芯片内部包括了相位累加寄存器,波形存储器,频率控制字等模块,并且拥有灵活的频率和相位控制方式。当工作于最基本的DDS方式时,PIRA和PIRB配合即可实现,频率和相位的控制,但集成好的DDS芯片不能面向使用者进行二次开发,只能输出自带的波形。此方案也可实现DDS的设计,但该芯片的外围电路比较复杂,输出波形也不便于设计。

方案2:采用基于锁相环式的频率设计方法实现信号发生器的功能。该频率合成器可实现频率的加、减、乘、除,它的整体结构是一种闭环系统。同时此种信号发生器设计时,可采用ADI公司的ADF4113锁相环芯片来实现,锁相环控制频率在指定位数上。该芯片的功能优良,常用于设计较高分辨率、低杂散的频率合成器。它的结构简单,便于集成和小型化是较突出的优势,流行于市场上的电子、通信产品的设计。较为短板的地方在于,此方案无法实现任意波形的输出。

方案3:采用基于FPGA的直接数字式的频率设计方法实现信号发生器的功能。其基本结构包括累加寄存器和波形存储器两部分,此设计主要基于LUT查找表的原理,多个LUT组合可实现ROM查找表功能。通过FPGA芯片完成电路设计,当控制字输送进累加寄存器并进行加操作,输出控制数据可选择ROM查找表中存放的波形数据进行输出,再搭配模拟电路的方法实现波形输出,当改变波形存储器(ROM查找表)中的波形数据,并选择信号输出就可以设计出任意波形发生器。此设计方法的直接数字式结构简单、便于集成、频率分辨率相较其他方法高出很多等优点,且可实现幅度、频率、相位的数控调节。

通过上文中提到的几种设计方法的对比,第一种设计方案直接使用DDS集成芯片,但是它的但这种设计存在诸多的缺陷,例如不够灵活、模块固定、不容易更换,只能输出出厂时在其内部设计好的波形数据,使用者再次设计自己想要的波形,因此不选择方案一。第二种设计方案,在设计中的分辨率要低于第三种设计方案,无法实现任意波形的设计,并且它使用时锁定的时间相对而言比较长,故不方便进行设计快速锁定的信号发生器件。方案三,此设计方法的直接数字式结构简单、便于集成、频率分辨率相较其他方法高出很多,本次设计最高频率达到10MHz,在使用时功耗方面也具有相对较低的突出点,同时在理论功能上也能够实现任意波形的组合和选择输出,因此本设计采用此方案三。

1.2 DDS结构和设计方法

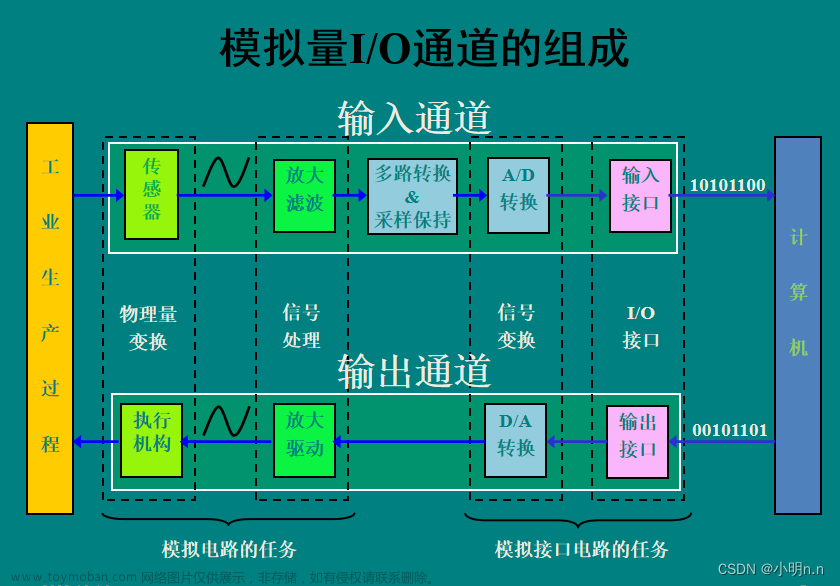

DDS技术是基于奈奎斯特取样定理,其工作的原理如图2.1所示,利用相位累加原理从相位的方面考虑研究波形信号的基本组织结构和工作原理。这次以正弦波为例子,通过正弦波线性增加的相位即可对它进行波形信号取样、波形信号量化、数据编码一系列操作实现连续的模拟信号转换成离散的数字信号,并将生成的二进制数字信号码存储在波形存储器(ROM/RAM)中,就相当于在内部存储器中存储了一个完整的周期性波形幅度值。当需要一个连续的正弦波时,可以通过控制频率控制字,来达到以相位累加器的相位变化量控制采样点数量的功能。同时,从正弦波的相位与时间的角度来看,角频率ω=△φ·△t,故在采样频率恒定的条件下,在内嵌模块中把波形存储器中的波形幅度数据并周期性地识别读出并输出可视的模拟信号波形。

图1 DDS工作原理

信号发生系统的核心部分是DDS模块,也是系统中波形数据输出的基本工作过程,该模块的结构如图2.2所示。根据以上的原理图和如图2.2所示的基本功能结构,fclk是整个DDS模块的系统时钟,它控制着各个子模块的工作实时性。比如,当一个正弦波输出时,通过认为设置输入频率控制字和相位控制字就分别控制这个波形输出的频率和波形的初始相位,当频率控制字的数值大小在键控下变化,输出的波形信号的频率高低也随之变化,相位累加器是实现控制波形输出的核心部分,波形的这样就达成了频率控制。

图2 DDS基本结构

1.3 系统设计总体思路

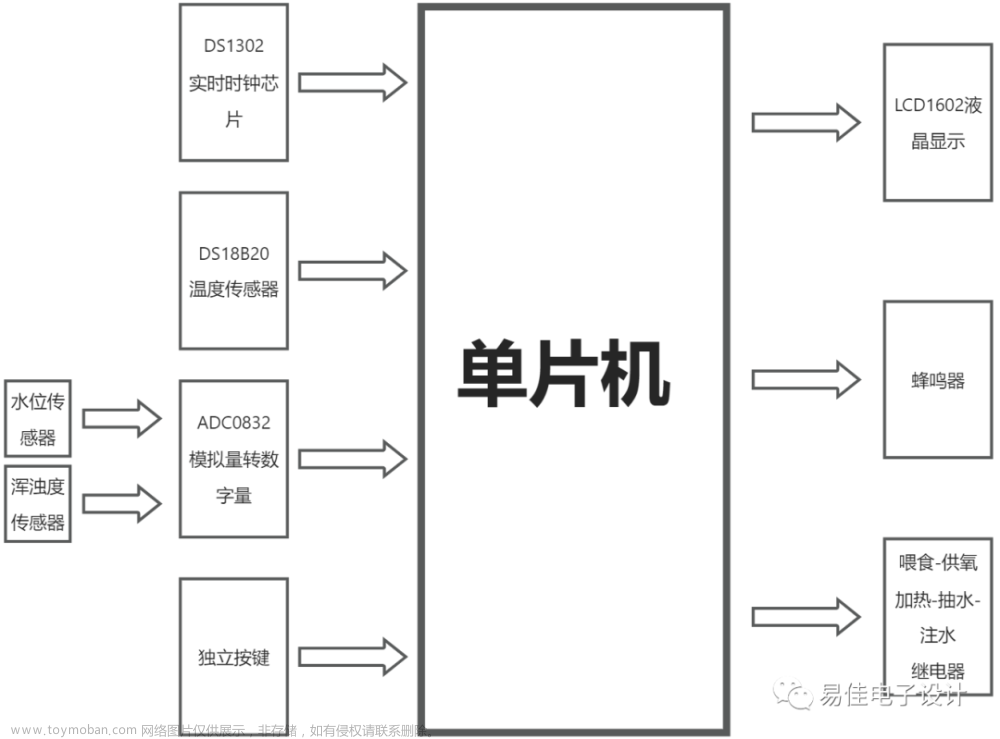

此次基于FPGA的DDS信号发生器主要通过高速集成电路硬件描述语言(VHDL)在Quqrtus19上进行电路设计、功能仿真。设计好的DDS电路下载到EP1C3T144C8N芯片上。同时选用AT89S52单片机最小系统,通过软件编程实现4×4的独立矩阵键盘的控制功能和液晶LCD1602的显示功能。通过向频率、相位、幅度控制字寄存器传送频率、相位、幅度控制字,实现键盘控制输出波形种类、频率变化、幅度变化、相位变化的功能,并且在LCD1602上实时显示出来。数模转换电路的设计主要用到AD公司生产的AD9708芯片,该芯片的主要功能是将离散的数字信号输出为模拟信号,再经过滤波后,将平稳、清晰、连续的波形信号输出在示波器上。

第二章 硬件系统设计

2.1 硬件系统总体设计

本次硬件电路通过AltiumDesigner19完成设计,DDS信号发生器的总体硬件结构设计包括:FPGA (EP1C3T144C8N)控制模块、单片机最小系统、D/A(AD9708)转换模块、幅度控制(TLC5615)模块、LCD1602显示模块、4×4按键输入模块。本设计以FPGA和单片机做为控制器,通过DDS技术输出需要的波形数据,然后通过高速AD输出模块输出波形;并能经过按键模块调节频率的数值以及通过拨码开关切换波形种类,且所输入的频率数值可通过LCD1602显示,最后通过示波器进行测试。

2.2 FPGA选型设计

2.2.1 FPGA概要

近几年内,在电子器件、半导体工艺的设计中,我们常常会用到现场可编程门阵列(FPGA)。由于它电路集成度高、数据处理速度快、内存容量较大等优势,FPGA十分地广泛应用于数字信号处理、视屏图文解析、应用数据传输等领域。FPGA发展到现在已经不是单纯的一种器件了,在数字信号处理的领域中FPGA是不可分割的一部分,我们常常使用Verilog语言来设计自己需要的数字系统和信号发生器[17]。

2.2.2 FPGA芯片选型

在本次的设计中,在对CycloneII系列芯片进行查阅资料并进行了解的情况下,选用的FPGA芯片为AITERA公司在二十一世纪初研制并发售的EP2C5T144C8N,如图3.1所示,此款芯片一共有144个引脚数,具有系统自带晶振输出时钟信号,同时可使用PLL进行市长管理[18]。具有上千个逻辑元件的表面安装现场可编程门阵列IC,使用时功耗不到1.8W,对于学习研发者该芯片在同类的芯片中有着较为突出的优势,功能齐全的同时出售价格比同种类芯片低,性价比较高。它的系统输入输出电压为3.3伏特,内核工作电源电压为1.15~1.25伏特,最大的工作频率为250MHz,芯片的工作温度在0℃~70℃之间,使用的静态随机存储器(SRAM)工艺更是达到了0.33UM的数量级。

在这里列出了部分CycloneII型芯片参数比对,如表3.1所示。故在考虑到资源最大利用率,成本最小化时,选用了EP2C5T144C8N芯片用作FPGA的开发。

表4 CycloneII芯片举例

图5 EP2C5T144C8N芯片

第三章 软件系统设计

3.1 系统软件总设计

本次选题的软件系统设计主要使用Verilog语言设计基于FPGA的DDS模块,使用C语言设计基于单片机最小体统的键盘控制模块和波形信息显示模块。通过C语言控制单片机将键盘输入的数据进行处理,实现单片机对整个系统的交互式控制,把经过单片机处理后的数据显示信息通过总线接口送入LCD1602控制液晶显示。

程序开始执行时,当键盘有按下输入时,单片机开始扫描键盘数据,并计算对应按键的功能实现,得到频率控制字,后进入DDS累加器模块,经过相位累加器对控制字的累加运算后得到地址,然后通过四个存储波形的ROM选择对应的波形进行输出,系统工作流程如图

图6 系统软件工作流程图

3.2 单片机控制程序设计

本次的单片机控制部分使用Keil5编写C语言程序实现,编程实现键盘扫描控制的功能,LCD波形数据显示的功能。

3.2.1 键盘扫描模块

本次选题键盘设计采用4×4的组合按键,共有4根I/O口线作为行扫描线,4根I/O口线作为列扫描线。当程序开始执行时,判断是否有按键按下时,每个按键都有着对应的行、列值,并以此组合编码来对这个按键进行识别。可将高低电平以1和0数字量表示,当没有按键按下时,对应的所有行线处于高电平(1状态),对应的列线处于低电平 (0状态)。而当进行操作时按下按键,此时对应按键的行线变化为低电平(0状态),再需要确定列的位置时,就依次从列线上输出低电平(0状态),其他的列线处于高电平(1状态),扫描各行线的高低电平状态,当扫描到某一行出现低电平(0状态),则可确定按下的按键位置编码。

系统初始化后,对键盘所在行列扫描和进行编码排序,键盘工作流程如图4.2所示,通电后系统初始化,初始化的键盘按键功能分布如图

图7 键盘工作流程图

图8 键盘功能分布位图

当按下频率设置键后,键盘的功能流程如图所示,此时键盘的按键状态发生改变,键盘按钮功能分布如图

图9 频率设置工作流程图

3.3 DDS软件模块设计

3.3.1 波形存储(ROM)模块

波形存储器的原理就相当于将一个设计好的波形在内存单元种预先存储好,在需要使用时就可以直接从波形存储器种调用输出。首先是设计一个ROM来存储基本的波形数据,如图4.7所示,为建立的正弦波ROM的IP核,其中ROM为8位,地址深度为256,ROM部分将会在DDS模块中进行例化。后续可根据相同原理添加三角波ROM的IP核,方波ROM的IP核,锯齿波ROM的IP核,并在顶层文件中设置好参数,如图

图10 ROM的IP核设置

图11 波形存储模块

3.3.2 波形选择模块

波形选择模块以读取键盘输入的数据信息并计算来决定输出的波形种类,当以同一按键的初始值确定,每按下一次实现二进制位的加一,selectOut端口输出计算出的控波形制字0100、0101、0110、0111,如图

图12 波形选择模块

3.3.3 四选一选择模块

本模块主要根据控制数据对输出的波形数据进行选择,主要使用case语句实现对四种波形的选择输出,当写入wave_mode端口读取到0100时输出波形为正弦波,读取到0101时输出波形为方波、读取到0110时输出波形为三角波、读取到0111时输出波形为锯齿波弦,具体的四位选择器如图

图13 四选一模块

3.3.4 幅度控制模块

本次设计中,幅度控制模块,如图4.13所示,此模块输出控制信息到TLC5615的DIN、SCLK、CS的I/O端口,控制TLC5615输出不同的电压给AD9708数模转换器的参考电压端口,从而控制波形幅度。

图14 幅度控制模块

3.3.5 系统时钟

在本次的FPGA软件系统设计部分,FPGA的全局时钟是不可或缺的,在选择的FPGA芯片版型中带有系统晶振,原始频率为50MHz。在本次设计中为了使各模块更紧密地配合,减小传输和触发的抖动和时延,故设计的各子模块的系统时钟需要一致,在本次系统设计中全局时钟可以选择利用FPGA嵌入的内核来设计,可以选择DLL/PLL/MMC。

图15 时钟输入设置

图15 时钟输入设置

图16 时钟输出设置

文章来源:https://www.toymoban.com/news/detail-774669.html

文章来源:https://www.toymoban.com/news/detail-774669.html

图18系统时钟模块文章来源地址https://www.toymoban.com/news/detail-774669.html

到了这里,关于毕设分享|基于51单片机DDS信号发生器设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!