时钟对于 FPGA 是非常重要的,但板载晶振提供的时钟信号频率是固定的,不一定满

足工程需求,所以分频和倍频还是很有必要的。

一、计数器分频

这里通过计数的方式来实现分频。

1.通过计数器来实现6分频。两种方式。第一种直接通过计数方式直接获取获取。输入信号sys_clk和sys_rst_n,输出分频的信号clk_out,还有一个变量计数器cnt。

cnt:计数器说明,要进行6分频,原始信号6个周期变一个周期输出,输出6分频周期的半个周期占三个原始时钟周期,对原始时钟计数3(0 1 2)

module divider_six

(

input wire sys_rst,

input wire sys_clk,

output reg clk_out

);

reg [2:0] cnt;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

cnt <= 2'd0;

else if(cnt == 2'd2)

cnt <= 2'd0;

else

cnt <= cnt+2'd1;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

clk_out <= 1'b0;

else if(cnt == 2'd2)

clk_out <= ~clk_out;

else

clk_out <= clk_out;

endmodule

testbench

`timescale 1ns/1ns

module tb_divider_six();

reg sys_rst;

reg sys_clk;

wire clk_out;

initial

begin

sys_clk = 1'b1;

sys_rst = 1'b0;

#20

sys_rst = 1'b1;

end

always #10 sys_clk = ~sys_clk;

divider_six divider_six_inst

(

.sys_rst(sys_rst),

.sys_clk(sys_clk),

.clk_out(clk_out)

);

endmodule

此时输出时钟就是clk_out ,如果直接用clk_out当作系统工作时钟

//直接使用clk_out作为工作时钟

always@(posedge clk_out or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

a <= 0;

else

a <= a + 1;

二、 通过计数器控制标志信号,通过标志信号当作系统工作时钟

module divider_six

(

input wire sys_rst,

input wire sys_clk,

output reg clk_flag

);

reg [2:0] cnt;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

cnt <= 2'd0;

else if(cnt == 3'd5)

cnt <= 3'd0;

else

cnt <= cnt+3'd1;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

clk_flag <=1'b0;

else if(cnt == 3'd4)

clk_flag <=1'b1;

else

clk_flag <=1'b0;

endmodule

此时产生使能信号flag(实际还是周期变化的信号理解为时钟,但是不当作时钟信号使用,当作使能信号触发,但是组合逻辑还是用系统源时钟)。

//工作时钟还是系统时钟

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

a <= 1'd0;

else if(clk_flag == 1'b1)

a <= a + 1'b1;

总结:两种方式的区别

这里为什么要说明这两种方式呢?

这里就要说到FPGA中的全局时钟网络,因为在 FPGA 中凡是时钟信号都要连接到全局时钟网络上,全局时钟网络也称为全局时钟树,是 FPGA 厂商专为时钟路径而特殊设计的,它能够使时钟信号到达每个寄存器的时间都尽可能相同,以保证更低的时钟偏斜(Skew)和抖动(Jitter)。然而我们采用第一种方式产生的时钟clk_out信号并没有连接到全局时钟网络上,这种做法所衍生的潜在问题在低速系统中不易察觉,而在高速系统中就很容易出现问题,但 sys_clk 则是由外部晶振直接通过管脚连接到了 FPGA 的专用时钟管脚上,自然就会连接到全局时钟网络上,所以在 sys_clk 时钟工作下的信号要比在 clk_out 时钟工作下的信号更容易在高速系统中保持稳定。所以第二种方式相对来说更加安全。

上述已经说到6分频,属于偶数分频。下面就来介绍奇数分频。奇数分频采用上述第二种方式来实现的话,思路和步骤都差不多。我这里介绍一下奇数分频采用上述的第一种方式。那么问题又来了,既然上述第一种方式没有第二种好,为什么还有讲的,哈哈,是的。我记录他并不是因为他的好,而是因为这里奇数分频时的思路和逻辑思维。这里实现一个5分频

首先是输入时钟和复位,一个计数器,两个变量分频时钟,一个输出时钟。要实现N奇数分频,计数器计数到N-1,这里5分频最大计数到4。然后变量clk1初始状态为高电平,系统时钟上升沿到来时有效,这里计数到2时拉低,其实这里可以计数到0,1,2,3都是可以的。clk2初始状态也是高电平,系统时钟下降沿到来时有效。这里计数到与clk1计数最大值一致就行,然后clk1与clk2做与运算就可以得到输出5分频时钟clk_out。

两个四分频,计数值范围不一样,造成相位偏移半个周期,两个四分频信号相与,输出5分频时钟信号,(最好该信号依然当作flag使能信号使用,在时序逻辑输入时钟还是使用原始时钟)

module divider_five

(

input wire sys_clk ,

input wire sys_rst_n ,

output wire clk_out

);

reg [2:0] cnt;

reg clk1;

reg clk2;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 3'd0;

else if(cnt == 3'd4)

cnt <= 3'd0;

else

cnt <= cnt + 1'b1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk1 <= 1'b1;

else if(cnt == 3'd2)

clk1 <= 1'b0;

else if(cnt == 3'd4)

clk1 <= 1'b1;

else

clk1 <= clk1;

always@(negedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk2 <= 1'b1;

else if(cnt == 3'd2)

clk2 <= 1'b0;

else if(cnt == 3'd4)

clk2 <= 1'b1;

else

clk2 <= clk2;

assign clk_out = clk1 & clk2;

endmodule

testbench

`timescale 1ns/1ns

module tb_divider_five();

reg sys_clk;

reg sys_rst_n;

wire clk_out;

initial

begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#30

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

divider_five divider_five_inst

(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.clk_out (clk_out)

);

endmodule

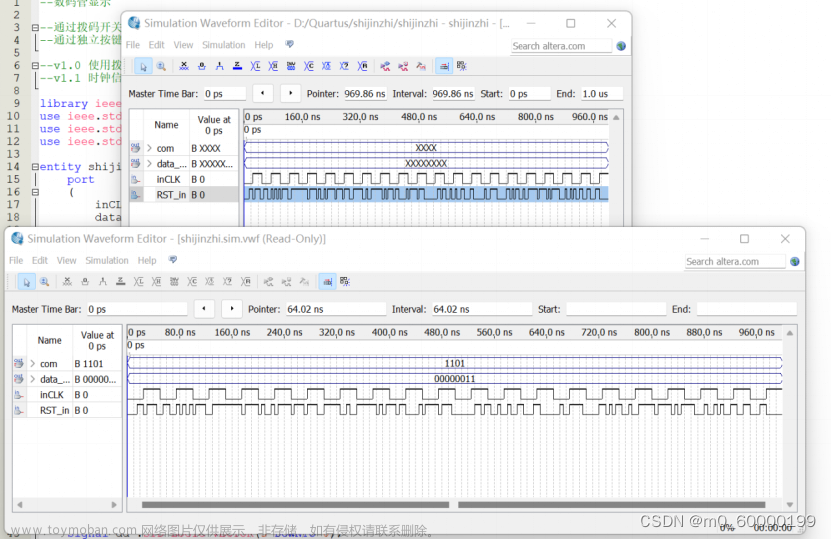

仿真

分频系数:50MHz晶振输入

输出1KHz时钟频率,50_000_000/1000=50_000

输出100KHz时钟频率,50_000_000/100_000=500文章来源:https://www.toymoban.com/news/detail-775239.html

来源:有所更改,加入自己理解(175条消息) FPGA——分频器_fpga分频器_rοckman的博客-CSDN博客https://blog.csdn.net/a17377547725/article/details/125927896文章来源地址https://www.toymoban.com/news/detail-775239.html

到了这里,关于FPGA_分频(信号使能分频与计数器分频)(奇偶分频)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![fpga[1]计数器(附源码)](https://imgs.yssmx.com/Uploads/2024/02/424742-1.jpeg)