电路和数据时钟恢复电路

CDR。光电检测电路完成将光信号转化为电脉冲信号,目前

阶段,

APD

雪崩二极管和

PIN

光电二极管等光探测器件被广泛应用。跨阻放大器完成

微弱的电流信号到强度足够的电压信号的放大和调理。主放大器的增益要能够自动调

节,使得光电检测器件输出的电流信号出现波动时能够自动调节增益,使得输出的可提

取电压信号幅值保持稳定,文献

[20]

中使用

MAXIM3269

与

AXIM3267

联合实现

2.5G

bit/s

的微弱电流信号放大功能,值得借鉴。数据时钟恢复电路

CDR

完成串行数据流到

并行数据的提取和恢复隐藏在其中的时钟,可以使用现场可编程逻辑门阵列

FPGA

来实

现。

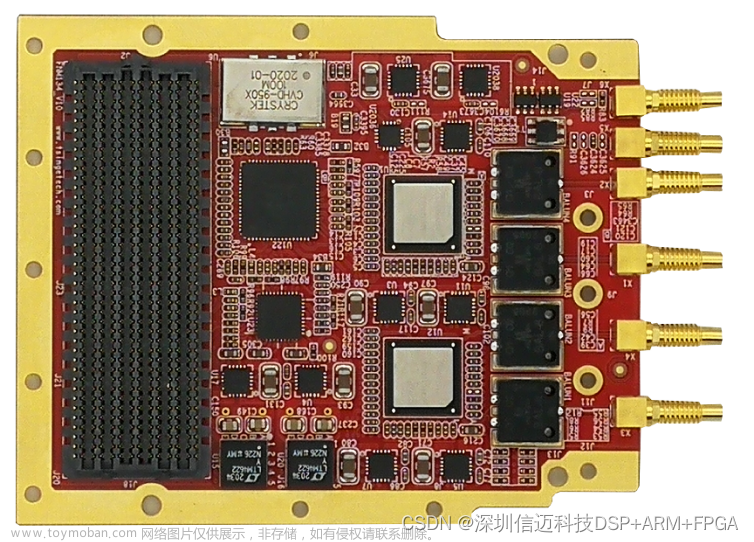

方案二:集成化构建方案

如图

2.3

所示为集成化构建方案的结构组成图,从中可以看出共三个模块构成,它

们分别是收发控制部分、专用芯片部分及光电转换部分。目前光纤通信技术已经得到广

泛应用,通信方案的构建方式正在向着模块化和集成化的方向发展

[8]

。其中,光电转换

部分集成了光发射电路及光探测电路,并提供发送和接收两个接口,常用的接口类型包

括

SC

和

FC

两种。专用芯片部分集成了数据并行到串行的转换、数据和时钟提取

CDR

、

平衡编码解码等功能,并提供发送参考时钟和恢复时钟引脚和并行接口总线给其余模

块。

文献

[9,11]

中都是采用集成化构建方案,在这些方案中,采用专用的数据转换芯片

和光电转换芯片来实现光纤通信电路的构建。光电转换模块主要是

Agilent

公司的

HFBR

系列,

HFBR-53A3VEM

、

HFBR-53A3VFM

等型号产品应用广泛。串并转换、时钟提

取等专用芯片模块主要是

CYPRESS

公司的

CY7B

、

CY7C

系列,

TI

公司的

TLK

系列,

其中

CY7B923

、

CY7B933

、

CY7C924

、

TLK1221

等型号器件应用广泛。

两种方案优缺点比较:

分立式构建方案比较灵活,维护以及升级方便,但是显然的缺点就是整体结构复杂,

需要使用大量元件来实现,因此会造成光纤通信整体的体积庞大,与整个系统相比,显

然有头重脚轻的毛病既不现实也不合适,同时需要对光纤的传输细节有清晰的认知,测

试、开发周期较长;而集成化构建方案总体结构简单明晰、且各子部分可靠性非常高,

设计者只需关注各个部分的连接即可,开发周期短,调试方便。因此本课题采用集成化

构建方案来完成核心运算处理单元

DSP

主系统与远程传感伺服系统的数据传输任务。

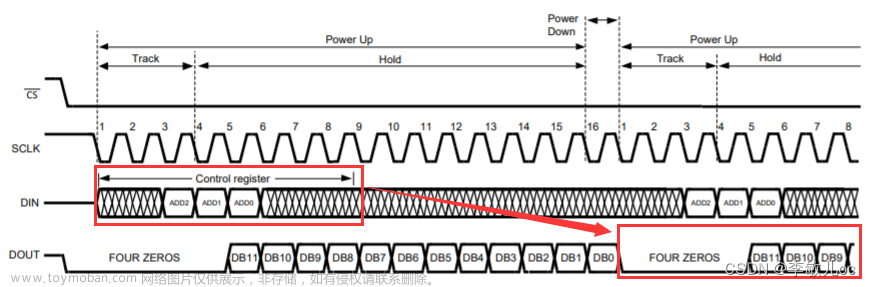

2.3.2 EnDat 双向串行通信方案选择

目前阶段,

EnDat

双向串行通信方案主流有两种,一种是直接采用

MAZeT

公司提

供的宏模块,另外一种是根据

EnDat

协议规范自主编写控制器内核实现其功能。文献

[47]

采用了

DSP

直接实现

EnDat

接口通信的方法,值得借鉴。

方案一:采用

MAZeT

宏模块

海德汉第三方合作伙伴

MAZeT

针对

Xilinx

公司

Virtex

和

Spartan

系列及

Altera

公

司

Acex

和

Cycolne

系列

FPGA

专门提供了

EnDat

协议的宏模块

[11]

,该宏模块实现了

EnDat

协议的全部功能,支持

EnDat2.2

版本的所有模式指令访问,并向下兼容

EnDat2.1

版本,同时该宏模块提供了

6

位地址总线、

16

位数据总线、读使能、写使能、中断触发

等访问接口,使得用户可以像访问

SRAM

一样简单的就能实现

EnDat

的所有功能,该

解决方案结构如图

2.4

所示。

方案二:自主编写

EnDat

实现

图

2.5

是自主编写

EnDat

时序解决方案的结构组成,从中可以看出与采用

MAZeT

宏模块的解决方案相类似,区别仅仅是两者来源不同,第一种方案采用官方的宏模块实

现,第二中方案则利用硬件描述语言

Verilog HDL

自主编写 EnDat 时序来实现其功能。

两种方案优缺点比较:

采用

MAZeT

宏模块的解决方案,把复杂的

EnDat 时序转换成了比较简单的时序,

因而减小了开发难度,缩短了开发周期,因而该方案具有较好的稳定性和可靠性;但同

时缺点也非常明显,首先

MAZeT

宏模块需要购买,价格相对昂贵,因此如果不需要大

批量生产,一般都不会采取这种方案,另外,

MAZeT

宏模块提供了完整的功能,因而

会占用大量的

FPGA

逻辑资源,而系统需求分析中指出全部的功能实现是不必要的,且

系统整体结构还包括了大量其余外设的控制器,因而本课题采用自主编写

EnDat

时序的

解决方案,只需编程实现

EnDat

的部分功能,因而节约了开发时间,降低了成本,同时

增加了设计的灵活性。

信迈提供DSP+FPGA半导体运动台方案。文章来源地址https://www.toymoban.com/news/detail-777736.html