👉个人主页: highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

目录

1.1全局动态铜皮参数设置

1.2手动绘制铜皮

1.3手动挖铜

1.4 手动修改铜皮边界

1.5删除孤岛铜皮

1.6动/静态铜皮转换

1.7合并铜皮

1.8平面铺铜和铜皮分割

1.9铜皮颜色设置

今天分享布线操作技巧中的铜皮操作。

1.1全局动态铜皮参数设置

单板上的电源部分、铺地都需要用到铜皮操作。先来熟悉一下铺铜的参数设置。Shape-global dynamic parameters,设置全局的动态铜皮参数。

第1页是铜皮填充参数,这里勾选smooth平滑铺铜,否则通铺不会主动避让。Xhatch style指的是网格铜的类型,这里一般默认即可,通常情况下我们一般铺实心铜,这个在操作铺铜时可以选择实心还是网格。后面的网格铜的参数都默认即可。另外可以勾选自动删除孤岛铜皮。

第2页用来控制铜皮的空位置,比如有的地方比较狭窄,窄到什么程度这里就不铺铜,从这里设置。Artwork format:光绘格式,默认选RS274X。Minimum aperture for gap width:缝隙宽度小于设置值时,就不铺铜,一般设置为10mil。suppress shape less than:铺设铜皮的宽度,默认铺出来的铜皮宽度不会小于设置值,一般设置25mil。create pin void:遇到通孔焊盘时的避让,一般就选择individual单独避让,还有in-line条形避让可以设置,一般不用。下面两个是避让时铜皮的形状,一般就默认圆形即可。

第3页表示间距设置,包括铜皮到焊盘、过孔、走线、文字、铜皮的间距,这里的Oversize value值的是,除了约束管理器设置的间距之外,再额外增加的距离,通常这里设置为0,可以直接在约束管理器进行调整。

第4页表示散热焊盘的连接方式,通常情况下通孔pin用十字连接,smd pin和过孔用全连接。十字连接的宽度设置用固定数值,可以是10mil或者15mil。

设置好铺铜参数后,开始执行铺铜命令。

1.2手动绘制铜皮

手动绘制铜皮操作:

执行菜单命令Shape,铺铜命令分别为:Polygon(绘制多边形,包括圆弧)、Rectangular(绘制矩形)、Circular(绘制圆形),这里可以根据需求选择铜皮形状。在option面板设置铺铜参数,先选择要铺铜的层,然后设置铜皮类型,通常为dynamic copper,表示动态实铜,另外还有,dynamic Crasshatch (动态网格铜)、Static Solid(静态实铜)、Static Crasshatch(静态网格铜)、Unfilled(不填充)适用于绘制board outline、package geometry、room等,不能用于Etch。下面的assign net name为给铜皮赋予网络,可以在这里先选择好网络名,也可以铺完后再赋予网络。铺完后再赋予网络的步骤为:shape-select shape or void/cavity,点击选中铜皮,右键-assign net-在PCB上点击想要赋予的网络即可。

铺完后的每一个单独的铜皮还可以单独修改参数,shape-select shape or void/cavity,点击选中铜皮,右键-parameters,可以进入和全局铜皮参数设置一样的界面进行参数修改。

1.3手动挖铜

手动挖铜操作:

在铺铜之后可能会需要删除一些碎铜或尖角铜皮,挖铜的功能就是将多余部分的铺铜进行移除,此操作只针对铺铜有效。

执行菜单命令Shape-Manual Void/Cavity,挖铜命令类型有:

Polygon:在一个完整的铜皮中挖掉一个任意形状的洞;

Rectangular:在一个完整的铜皮中挖掉一个矩形的洞;

Circular:在一个完整的铜皮中挖掉一个圆形的洞;

Delete:将用manual void/ polygon挖掉的的铜皮恢复,激活命令后,点击两次挖铜轮廓边界,即可删除此挖空;

Element:静态铜皮的手动避让命令,只针对静态铜皮有效,铺完静态铜皮后,注意先要修改此铜皮的参数,设置避让的距离,然后激活命令,先点击铜皮,然后点击要避让的元素,如smd pin,即可完成避让;

Move:移动挖铜区域的轮廓,只针对静态铜皮的挖铜有用,激活命令后,点击两次挖铜轮廓边界,挖铜区域就会悬停在鼠标上,再点击铜皮的其他部位,可以原处挖空移动到鼠标点击的位置;

Copy:复制挖铜区域的轮廓,只针对静态铜皮的挖铜有用,激活命令后,点击两次挖铜轮廓边界,挖铜区域就会悬停在鼠标上,再点击铜皮的其他部位,可以再挖一个此轮廓的铜皮;

1.4 手动修改铜皮边界

手动修改铜皮边界操作:

有时候手动画完铜皮后,发现铜皮边界有点大或者有点小,想要调整就可以用shape-edit boundary,然后收尾两次点击原铜皮边界,即可完成修铜。

1.5删除孤岛铜皮

删除孤岛铜皮操作:

自动铺铜和修铜后,可能会出现某铜皮网络没有与单板上的此网络其他元素相连,这就叫孤岛铜皮,这些铜皮需要删掉或者想办法将其于其他部分连接起来。Shape-delete island,option面板会出现当前层的孤岛数量,delete all on layer,可以删除所有当前层的孤岛。点击First可以定位到当前的孤岛位置,如果有多个孤岛,first点击后变为next,继续点击可以接着定位下一个孤岛。

1.6动/静态铜皮转换

铺了的铜皮可以进行类型转换,若先铺了一块静态铜皮,通过命令shape-change shape type,在option面板中选择to dynamic copper,然后点击铜皮,即可完成切换,切换后会自动避让。同样的,动态也可以切换为静态,通常板卡设计差不多的时候,可以切换为静态铜皮,这样在后期修改走线时没有那么卡。

1.7合并铜皮

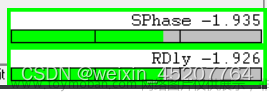

当画了两个网络一样的铜皮叠在一起,如下图所示,可以使用铜皮合并命令,shape-merge shapes,然后分别点击两个铜皮,即可完成合并。

1.8平面铺铜和铜皮分割

设计中经常会遇到有多种地平面的情况,比如模拟地、数字地、机壳地,这些不同的地平面如果一个个手动画效率会比较低,可以先铺一个整平面,然后进行分割。

先绘制分割线,add-line,在option面板选择画线层为anti etch的所有层,线宽根据实际要求分割宽度设置。

然后开始铺地,edit-split plane-create,选择要铺铜的层,选择动态铜皮,点击create,提示要赋予网络,给两块铜皮分别赋予网络即可完成分割铺铜,也可以点击cancel,铺完铜后再手动赋予网络。此方法也可用于电源平面分割。

1.9铜皮颜色设置

给铜皮设置不同颜色:

当电源平面有多种电源,可用不同颜色加以区分,在颜色管理器中设置:

文章来源:https://www.toymoban.com/news/detail-777860.html

文章来源:https://www.toymoban.com/news/detail-777860.html

以上操作还可以对同一个网络的不同元素赋予不同颜色。文章来源地址https://www.toymoban.com/news/detail-777860.html

到了这里,关于【allegro 17.4软件操作保姆级教程七】布线操作基础之二--铜皮操作的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!