个人笔记。

vivado不同版本之间有可能并不兼容,需要更改一些配置即可。我现在用的是vivado2017.4版本,现在想打开vivado2018.3版本的工程,但会出现警告,主要是版本不兼容导致。

可以按以下步骤来解决。

1、用一个文本编辑器打开我们的工程项目.xpr,修改version和minor

看到2018版本的version和minor为7和39,而2017版本为7和 35(如果不知道自己版本是多少可以用编辑器打开一个自己版本的工程查找)修改后记得保存后再打开工程

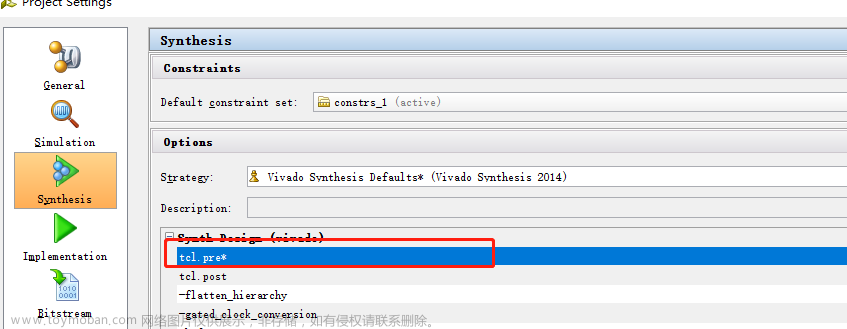

2、完成第一步后打开工程如果出现报错“ 【Common 17-70】 Application Exception: SrcMgr::createSS : type not set”,则在.xpr中找到下图程序段

将其删除,再保存,打开工程即可。

3、如果工程里有ip核的话,会出现ip核被锁的情况

只要依次点击Tools→Report→Report IP Status,将要解锁的ip核勾选再点击Upgrade Selected即可。到这一步已经完成了解决版本兼容的问题。

有个别特殊情况的ip核你会发现找不到所以没办法解锁

这种ip核一般是自己配置的,所以只要按照原来的配置方法即可。文章来源:https://www.toymoban.com/news/detail-778567.html

其他版本之间的兼容问题也可按照此方法解决。文章来源地址https://www.toymoban.com/news/detail-778567.html

到了这里,关于【FPGA】解决vivado工程版本兼容问题的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!