这篇具有很好参考价值的文章主要介绍了Vivado软件的使用。希望对大家有所帮助。如果存在错误或未考虑完全的地方,请大家不吝赐教,您也可以点击"举报违法 "按钮提交疑问。

目录

1 新建工程

1.1 Flow Navigator

1.2 数据窗口区域

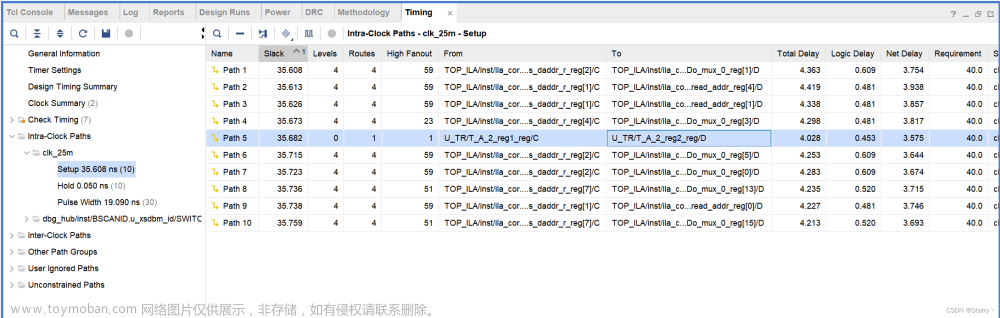

1.3 Properties 窗口

1.4 工作空间(Workspace)

1.5 结果窗口区域

1.6 主工具栏

1.7 主菜单

1.8 窗口布局(Layout)选择器

2 设计输入

修改字体大小

3 分析与综合

4 约束输入

5 设计实现

6 下载比特流

1 新建工程

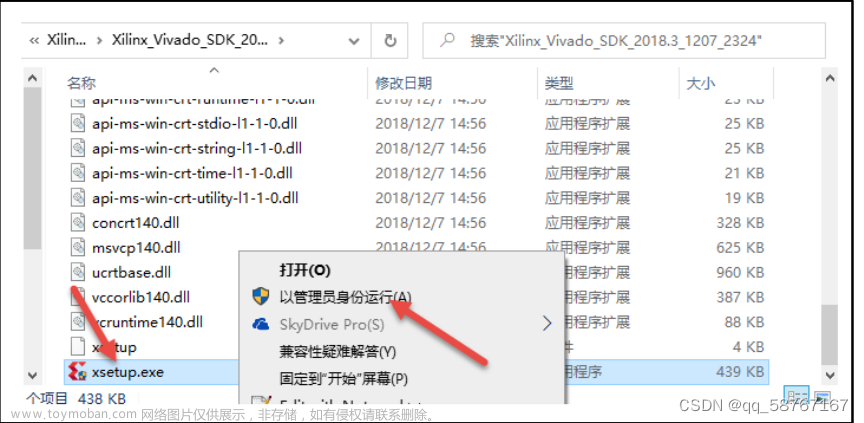

双击Vivado 2018.3

点击“Create Project ”

1 Vivado 软件启动界面

2 新建工程向导

3 输入工程名称和路径

4 工程类型的选择

5 添加源文件的界面

6 添加约束文件

7 ZYNQ-7010 核心板芯片型号

8 工程概览(Summary)页面

工程创建完成后,就进入了 Vivado 的工程主界面,如下图所示:

Vivado 工程主界面

下面介绍 Vivado 工程主界面中的几个主要子窗口:

1.1 Flow Navigator

Flow Navigator 提供对命令和工具的访问,其包含从设计输入到生成比特流的整个过程。 在点击了相应的命令时,整个 Vivado 工程主界面的各个子窗口可能会作出相应的更改。

1.2 数据窗口区域

默认情况下,Vivado IDE

的这个区域显示的是设计源文件和数据相关的信息。

• Sources

窗口:显示层次结构(

Hierarchy

)、

IP

源文件(

IP Sources

)、库(

Libraries

)和编译顺序(Compile Order

)的视图。

• Netlist

窗口:提供分析后的(

elaborated

)或综合后的(

synthesized

)逻辑设计的分层视图。

1.3 Properties 窗口

显示有关所选逻辑对象或器件资源的特性信息。

1.4 工作空间(Workspace)

工作区显示了具有图形界面的窗口和需要更多屏幕空间的窗口,包

括:

• Project Summary

。提供了当前工程的摘要信息,它在运行设计命令时动态地更新。

• 用于显示和编辑基于文本的文件和报告的 Text Editor

。

• 原理图(Schematic

)窗口。

• 器件(Device

)窗口。

• 封装(Package

)窗口。

1.5 结果窗口区域

在 Vivado IDE 中所运行的命令的状态和结果,显示在结果窗口区域中,这是一

组子窗口的集合。在运行命令、生成消息、创建日志文件和报告文件时,相关信息将显示在此区域。默认情况下,此区域包括以下窗口:

• Tcl Console

:允许您输入

Tcl

命令,并查看以前的命令和输出的历史记录。

• Messages

:显示当前设计的所有消息,按进程和严重性分类,包括“

Error

”、“

Critical Warning”、“Warning

”等等

• Log

:显示由综合、实现和仿真

run

创建的日志文件。

• Reports

:提供对整个设计流程中的活动

run

所生成的报告的快速访问。

• Designs Runs

:管理当前工程的

runs

。

1.6 主工具栏

主工具栏提供了对 Vivado IDE 中最常用命令的单击访问。

1.7 主菜单

主菜单栏提供对 Vivado IDE 命令的访问。

1.8 窗口布局(Layout)选择器

Vivado IDE 提供预定义的窗口布局,以方便设计过程中的各种任

务。布局选择器使您能够轻松地更改窗口布局。或者,可以使用菜单栏中的“Layout”

菜单来更改窗口布局。

2 设计输入

创建工程顶层文件:点击“

Sources

”窗口中的“

+

”号

1 添加源文件按钮

选择添加设计源文件(注意,Vivado

不支持使用原理图的方式来输入设计),然后点击“Next

”按钮:

2 选择添加设计源文件

在弹出的页面中添加或者创建一个文件。如果事先有编写好的代码,可以点击“Add Files ”按 钮来添加文件;如果没有,则点击“Create File ”创建一个新的设计文件:

3 点击创建源文件

4 输入源文件名称

5 添加的源文件

接下来会弹出一个定义模块的页面,用于设置源文件的模块名称和端口列表,Vivado 会根据在此窗口中的设置,自动地在 HDL 源文件中写入相应的 verilog 语句。我们会手动输入代码,所以这里不作任何设置,直接点击“OK ”按钮即可:

6 定义顶层模块名和模块端口

7 模块定义确认页面

这时工程主界面的“Sources ”窗口中就出现了我们刚刚创建的源文件:

8 源文件创建完毕

我们双击打开“my_test”文件,删除文件中默认的代码,然后替换成 LED

灯闪烁代码:

module led_twinkle(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output [1:0] led //LED 灯

);

//reg define

reg [25:0] cnt ;

//*****************************************************

//** main code

//*****************************************************

//对计数器的值进行判断,以输出 LED 的状态

assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10 ;

//计数器在 0~5000_000 之间进行计数

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 26'd0;

else if(cnt < 26'd5000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

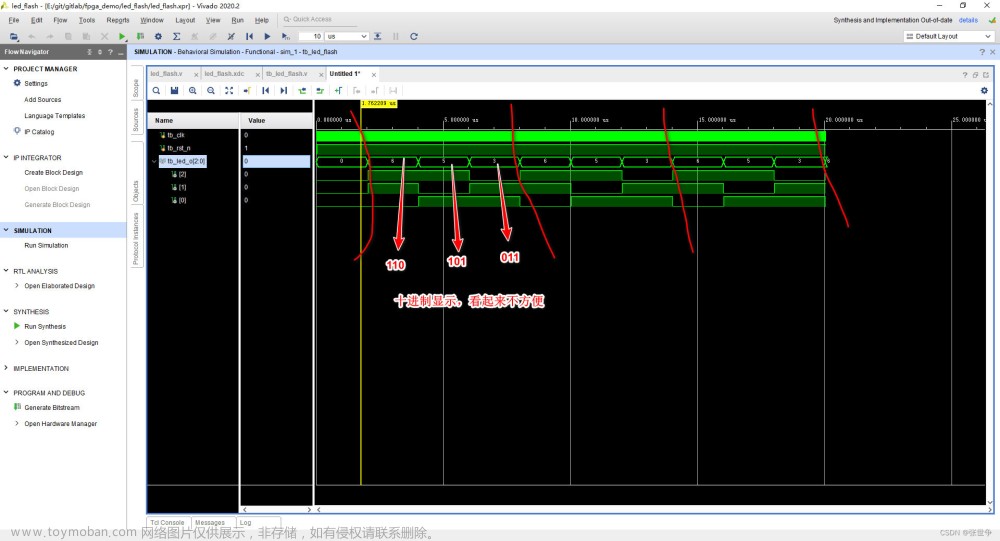

endmodule 代码编写完成后,软件中显示的界面如下图所示。

9 Verilog 文件编写完成界面

修改字体大小

依次点击“Settings

”→“

Text Editor” →“

Fonts and Colors

”,在窗口中的“

Size

”选项中来修改字体大小。

修改代码的字体大小

单击工作空间中的保存按钮或者按下键盘的“Ctrl+S

”,来保存编辑完成后的代码.

3 分析与综合

点击“Flow Navigator

”窗口中的 “Open Elaborated Design

”按钮:

此时,Vivado

会编译 RTL 源文件并进行全面的语法检查 ,并在 Messages

窗口中给出相应的“

Error

” 和“Warning

”。如果出现“

Error

”,则分析失败,用户必须修改设计文件,并重新编译源文件来取消 “Error

”。如果出现“

Warning

”,用户也可逐一查看,以确定哪些是设计缺陷,哪些是可以忽略的。打开分析后(Elaborated)的设计,

Vivado

会生成顶层原理图视图 ,并在默认

view layout

中显示设计,如下图所示:

打开的 Elaborated Design

可以看到,此时窗口布局已经发生了变化,新增了 Schematic

(原理图)、

Netlist

(网表)等窗口。此时,底部的 Messages

窗口会显示分析阶段产生的消息,如下图所示:

Messages 窗口中的消息

可以看出,我们 LED

闪烁实验的代码并没有产生警告或者错误。

此时,我们也可以进行 I/O 引脚分配,在右上角的窗口布局( Layout )选择器中选择 “I/O Planing”:

点击“I/O Planing”Layout

I/O Planing 窗口布局

在下方的“I/O Ports”窗口中,就可以进行 IO 的分配了。这里我们暂时不分配,先对设计进行综合, 综合之后再统一输入时序约束和 IO 引脚的物理约束 。

关闭分析后的界面:

关闭分析后的设计

点击“Run Synthesis”按钮,来对代码进行综合

Launch Runs 窗口,点击OK

可在“ Design Runs”窗口中查看到正在综合。

综合完成后,弹出如下窗口:

综合完成

关闭该窗口。接下来进行约束的输入。

4 约束输入

首先创建一个约束文件。点击“Sources ”窗口中的“ + ”号,在弹出的窗口选择“ Add or create constraints”,点击“ NEXT ”按钮,如下图所示:

1 添加约束文件

在接下来的界面中点击“Create File ”创建一个新的约束文件,如下图所示:

2 创建一个新的约束文件

3 输入约束文件的名称

接下来点击“Finish ”按钮,完成约束文件的创建 :

4 完成约束文件的创建

这时我们就可以在“Sources ”窗口中看到添加的这个约束文件了,如下图所示:

5 添加完成的约束文件

Vivado 的约束文件是以“ .xdc ”为后缀的文本文件,其中存储的是一条条的 xdc 约束命令。

双击打开 led_twinkle.xdc

文件,开始对工程进行约束。约束一般分为两种,一种是

IO 管脚的约束 ,另外一种是对时序进行约束 。我们先来看下 IO 管脚的约束,约束语句如下:

#IO 管脚约束

set_property -dict {PACKAGE_PIN U18 IOSTANDARD LVCMOS33} [get_ports sys_clk]

set_property -dict {PACKAGE_PIN N16 IOSTANDARD LVCMOS33} [get_ports sys_rst_n]

set_property -dict {PACKAGE_PIN H15 IOSTANDARD LVCMOS33} [get_ports {led[0]}]

set_property -dict {PACKAGE_PIN L15 IOSTANDARD LVCMOS33} [get_ports {led[1]}]

第一行以“#

”号开头,表示这是一条注释 语句,每一条注释也单独占用一行。第二行是有效的约束命令,每一个约束命令单独占用一行 ,命令的结尾不需要像 verilog

代码一样,添加分号“

;”结束符号。 命令的

第一个关键字 代表

该命令的名称 ,

其后的所有字段都是该命令的参数列表 。

IO 管脚约束是对端口的引脚位置和电平标准进行约束 ,例如第二行命令是对系统时钟的管脚进行约束,“set_property”是

命令的名称 ;“PACKAGE_PIN U18”是

引脚位置参数 ,代表引脚位置是 U18;“[get_ports sys_clk]”代表该约束所要附加的对象是 sys_clk 引脚;“IOSTANDARD LVCMOS33”代表该引脚所使用的电平标准是LVCMOS33。

IO 管脚约束比较好理解,就是我们的程序所驱动的

IO

和

ZYNQ

芯片的

IO

对应起来。而时序约束 (Timing Constraints

)用来描述设计人员对时序的要求 ,比如时钟频率,输入输出的延时等,以满足设计的时序要求。约束语句如下:

#时钟周期约束

create_clock -name clk -period 20 [get_ports sys_clk ]

“create_clock

”是该命令的名称,它会创建一个时钟;其后的“-name clk”、“-period 20”、“[get_ports sys_clk ]

”都是该命令的各个参数,分别表示所创建时钟的名称是“

clk

”、时钟周期是

20ns 、时钟源是 sys_clk

端口,一般只对输入的时钟做周期的约束 。

对时钟的约束最简单的理解就是,设计者需要告诉 EDA 工具设计中所使用的时钟的频率是多少;然后工具才能按照所要求的时钟频率去优化布局布线,使设计能够在要求的时钟频率下正常工作。本次实验sys_clk 的时钟频率为 50MHz ,周期为 20ns ,在做约束时可以等于这个值或者略低于这个值,不建议周期设置的太小,否则软件在布局布线时很难满足这个要求。

其实对于比较简单的设计,可以不对工程做时序约束,即使不进行时序约束,也不影响最终的功能。而当设计变得复杂起来,或者输入的时钟频率比较高的时候,如果不添加时序约束,那么就有可能在验证设计结果的时候出现一些意料之外的情况。由于本次实验较为简单,这里只对工程对 IO 管脚约束,不进行时序约束,led_twinkle.xdc 文件输入 IO 管脚约束语句后,点击“保存”的图标或者按下键盘的 “Ctrl+S ”进行保存。输入 IO 管脚约束语句后如下图所示:

输入 IO 管脚约束语句

点击 Text Editor 中的保存按钮后,就完成了约束的输入。

5 设计实现

约束输入完毕之后,就可以开始实现设计了。

1 点击“Run Implementation”按钮

2 开始实现

文章来源地址https://www.toymoban.com/news/detail-778573.html

3 实现完成

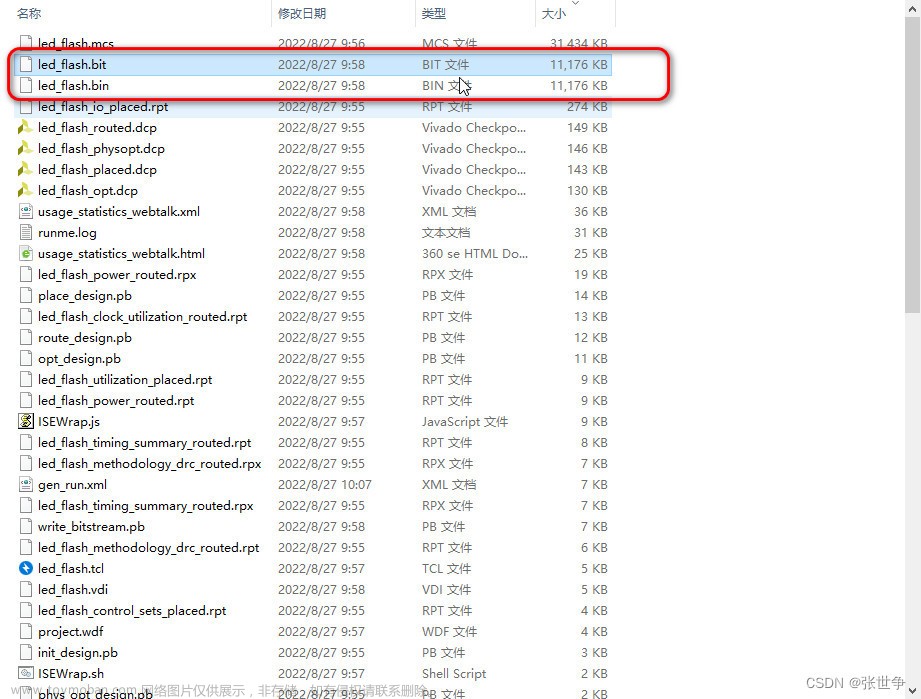

6 下载比特流

1 Generate Bitstream

文章来源:https://www.toymoban.com/news/detail-778573.html

2 开始生成比特流

比特流生成完毕之后, Vivado 会弹出提示窗口,我们点击取消关闭该窗口:

3 比特流生成完毕

4 Open Hardware Manager

5 Auto Connect

6 Program Device

7 下载比特流

到了这里,关于Vivado软件的使用的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处: 如若内容造成侵权/违法违规/事实不符,请点击违法举报 进行投诉反馈,一经查实,立即删除!