目录

前言

一、通过 添加 mark debug

1、进行综合

2、抓取信号

3、保存

4、查看信号

二、通过 ILA IP核

1. 在Vivado 的 IP栏里添加ILA

2. 在需要用到的模块里例化 ILA

三、对比

总结

前言

在对FPGA编程时,我们经常需要从与FPGA相连的芯片中读取信号,可以用FPGA芯片特定的软件来抓取信号,下面是用vivado抓取信号的两个方法。

一、通过 添加 mark debug

在需要观察的信号前面加:(* MARK_DEBUG="true" *)

(* MARK_DEBUG="true" *)output CpSl_PLL1CE_o ,

(* MARK_DEBUG="true" *)output CpSl_PLL1CSB_o ,

(* MARK_DEBUG="true" *)output CpSl_PLL1CLK_o ,

(* MARK_DEBUG="true" *)output CpSl_PLL1SDI_o ,

(* MARK_DEBUG="true" *)input CpSl_PLL1SDI_i

1、进行综合

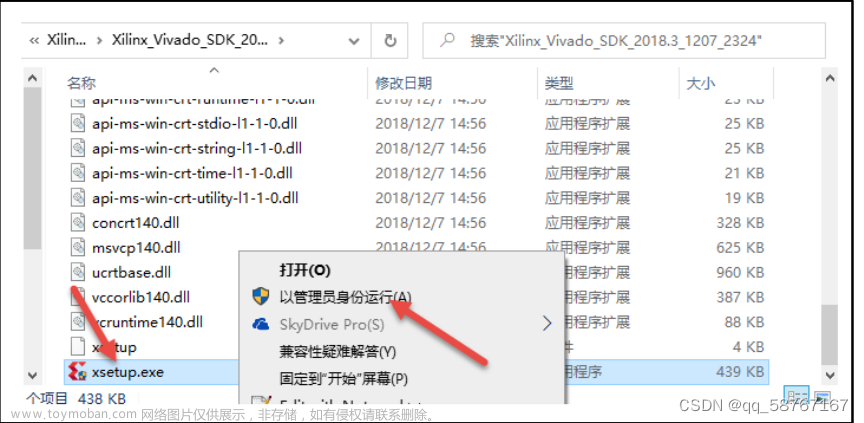

左击 run synthesis 进行综合。

2、抓取信号

左击如图所示的小三角,一定要是小三角。

左击set up debug,稍等一会儿,就能在出来的界面上选择要观察的信号了。

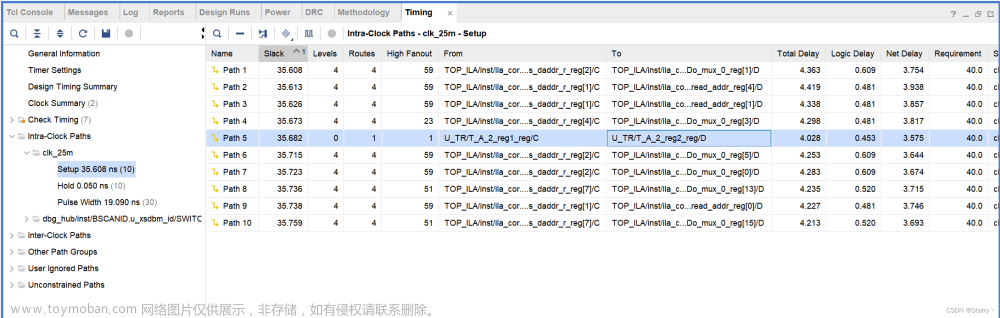

时钟标红的地方,右击标红的地方,选择 select clock domain ,选择要使用的时钟即可。

3、保存

以上步骤完成后,一定好ctrl + s 或者点击左上角的保存标志保存好。

4、查看信号

保存好综合后,生成比特文件,连接板卡,下载比特文件到芯片里,选择要查看的信号即可。

二、通过 ILA IP核

1. 在Vivado 的 IP栏里添加ILA

根据需要选择端口数

根据需要修改 名字,以及位宽。

设置好后点击OK,

最后点 generate。

2. 在需要用到的模块里例化 ILA

例如,在verilog模块中例化:

三、对比

使用mark debug的方式需要先综合然后进行抓取的信号的更新,不能直接生成比特文件,否则无法观察到信号;使用ILA的话,例化之后直接生成比特文件,最后可以观察到信号。文章来源:https://www.toymoban.com/news/detail-778814.html

总结

点滴积累,不断进步。文章来源地址https://www.toymoban.com/news/detail-778814.html

到了这里,关于vivado 抓取信号:mark debug 和 ILA的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!