Xilinx FPGA开发环境vivado使用流程

1.启动vivado

2.选择Create New Project

3.指定工程名字和工程存放目录

4.选择RTL Project

5.选择FPGA设备

6.工程创建完成后

7.开始编写verilog代码

第一步:点击Add Sources按钮

第二步:选择add or create design sources按钮,即添加设计文件

第三步:选择create file

文件新建完成后:

此时可以定义I/O端口,我们选择自己在程序中编写。

第四步:在编辑器中编写verilog程序

8.添加XDC管脚约束文件

XDC文件里主要是完成管脚的约束,时钟的约束,以及组的约束

第一步:新建约束文件

第二步:创造约束文件

第三步:编辑管脚约束文件

其中,

Set_property PACKAGE_PIN “引脚编号” [get_ports “端口名称”]

Set_property IOSTANDARD “电压” [get_ports “端口名称”]

9.编译

第一步:运行Run Synthesis 综合

第二步:运行Run Implementation 布局布线

第三步:运行Generate Bitstream 生成bit文件文章来源:https://www.toymoban.com/news/detail-778891.html

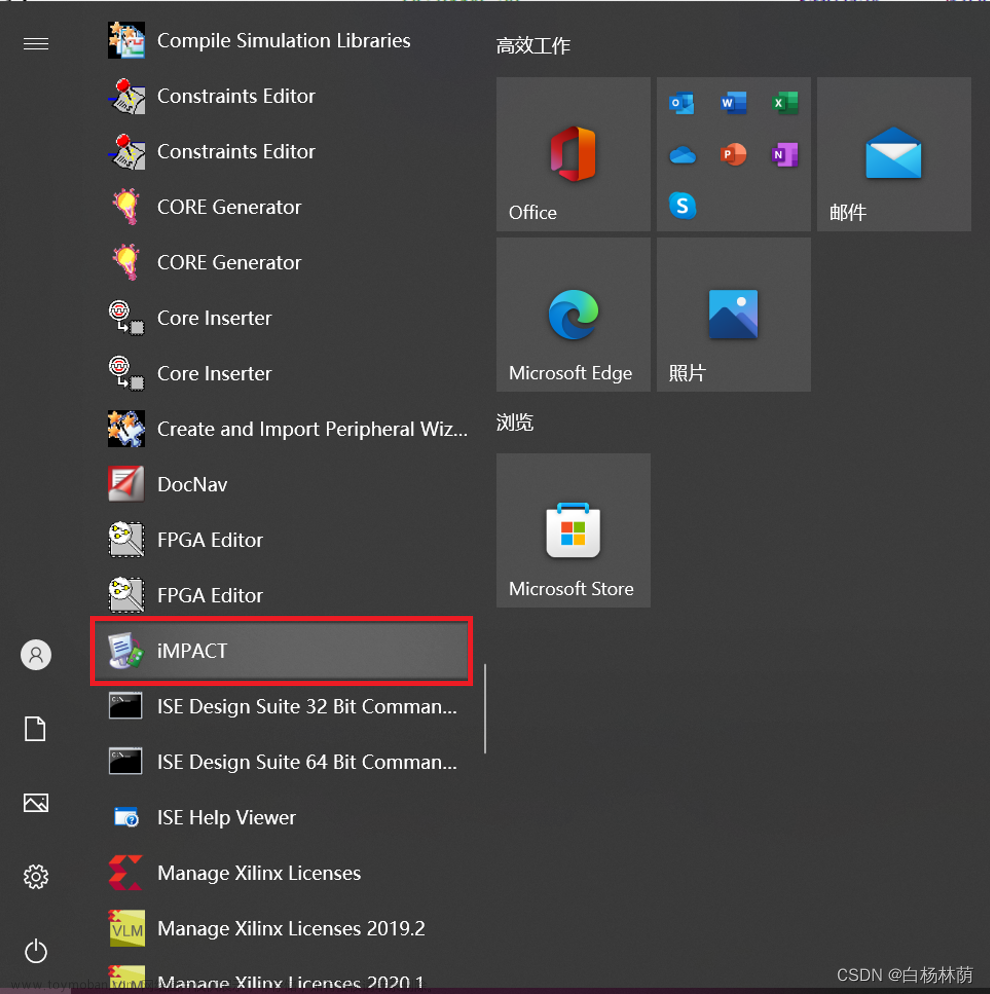

10.下载和调试

运行Hardware Manager。文章来源地址https://www.toymoban.com/news/detail-778891.html

到了这里,关于Xilinx FPGA开发环境vivado使用流程的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![xilinx FPGA 板子vivado无法识别 Labtoolstcl 44-27] No hardware targets exist on the server [localhost:3121]](https://imgs.yssmx.com/Uploads/2024/02/774191-1.png)