前言

本次主要介绍一下关于EDA做的初次实验:流水灯设计。实验包括Vivado仿真的具体流程、实现EDA板子的实物仿真。

一、设计内容

1.学习Vivado软件,并按照Vivado开发流程,熟练其Vivado的硬件、软件使用的流程。

2.利用给定流水灯的原程序,仿真程序,进行软件仿真,观察其结果。

3.利用给定流水灯的原程序,约束程序,进行硬件实物仿真,观察流水灯变化的情况。

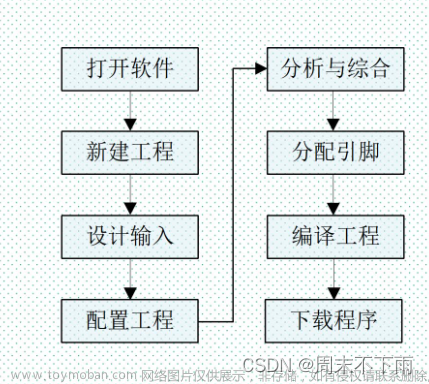

二、设计过程(及设计步骤)

2.1 工程建立

(1)打开Vivado软件,出现下面窗口,打开Create Project创建项目 (2)点击Next

(2)点击Next

(3)创建工程名字,选择保存路径,并选中创建项目子路径

(4)选择RTL Project一项,并勾选Do not specify sources at this time。 (5)选择对应的FPGA对应的器件。这里选择的是xc7a35tcsg324-1。

(5)选择对应的FPGA对应的器件。这里选择的是xc7a35tcsg324-1。 (6)确认相关信息与设计所用的FPGA器件信息是否一致,一致的话点击Finish,完成空白工程建立。

(6)确认相关信息与设计所用的FPGA器件信息是否一致,一致的话点击Finish,完成空白工程建立。

2.2 添加源文件

(1)打开Add Sources的对话框,点击Add or create design sources。

(2)选择Create File,然后在弹出的框中输入File name,点击OK。

(3)点击Finish。

(4)输入设计模块所需的端口,并设置端口方向。如果端口为总线型,勾选Bus选项,并通过MSB和LSB确定总线宽度。最后点击OK。 (5)点击新建的源文件,添加源程序

(5)点击新建的源文件,添加源程序

源程序如下所示:

module flowfight( //声明模块名,方便后面的调用

input clk, //声明端口的输入输出信号

input rst,

output [15:0] led

);

reg [23:0] cnt_reg; //寄存24位的中间参量,为下面时钟分频做准备

reg [15:0] light_reg; //对应16位的输出信号led

always @ (posedge clk) //clk上升沿触发

begin

if(!rst) cnt_reg <= 0; //rst为0时,cnt_reg赋值为0

else cnt_reg <= cnt_reg + 1; //rst为1时, cnt_reg加一

end

always @ (posedge clk) //clk上升沿触发

begin

if (!rst)

light_reg <= 16'h 0003; // light_reg初始赋值,第0,1位为高电平

else if (cnt_reg == 24'hffffff) //利用cnt_reg,进行时钟分频,方便硬件观察现象

begin

if (light_reg == 16'hc000) //流水灯循环一个流程后

light_reg <= 16'h0003; //重新对light_reg初始赋值,第0,1位为高电平

else

light_reg <= light_reg << 1; //流水灯左移一位

end

end

assign led = light_reg; //将寄存的light_reg的值赋值到led输出端口

endmodule

2.3 添加约束文件

(1)打开Add Sources的对话框,点击Add or create constraints。

(2)选择Create File,然后在弹出的框中输入File name,点击OK。 (3)点击Finish。

(3)点击Finish。 (4)点击新建的约束文件,添加约束程序

(4)点击新建的约束文件,添加约束程序

约束程序如下所示:

set_property PACKAGE_PIN K3 [get_ports {led[0]}]

set_property PACKAGE_PIN M1 [get_ports {led[1]}]

set_property PACKAGE_PIN L1 [get_ports {led[2]}]

set_property PACKAGE_PIN K6 [get_ports {led[3]}]

set_property PACKAGE_PIN J5 [get_ports {led[4]}]

set_property PACKAGE_PIN H5 [get_ports {led[5]}]

set_property PACKAGE_PIN H6 [get_ports {led[6]}]

set_property PACKAGE_PIN K1 [get_ports {led[7]}]

set_property PACKAGE_PIN K2 [get_ports {led[8]}]

set_property PACKAGE_PIN J2 [get_ports {led[9]}]

set_property PACKAGE_PIN J3 [get_ports {led[10]}]

set_property PACKAGE_PIN H4 [get_ports {led[11]}]

set_property PACKAGE_PIN J4 [get_ports {led[12]}]

set_property PACKAGE_PIN G3 [get_ports {led[13]}]

set_property PACKAGE_PIN G4 [get_ports {led[14]}]

set_property PACKAGE_PIN F6 [get_ports {led[15]}]

set_property PACKAGE_PIN P15 [get_ports rst]

set_property PACKAGE_PIN P17 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

2.4 添加仿真文件,并仿真

(1)打开Add Sources的对话框,点击Add or create simulation sources。 (2)选择Create File,然后在弹出的框中输入File name,点击OK。

(2)选择Create File,然后在弹出的框中输入File name,点击OK。 (3)点击Finish。

(3)点击Finish。

(4)点击OK。

(5)点击新建的仿真文件,添加仿真程序

仿真程序如下所示:

module con_flowfight1(

);

reg clk;

reg rst;

wire [15:0] led;

flowfight u0( //调用源程序,并给调用的模块进行命名

.clk(clk), //将端口映射进行例化名

.rst(rst),

.led(led));

parameter PERIOD = 10; //参数声明,并赋值为10

always //每隔5ns,时钟翻转一次

begin

clk = 1'b0;

#(PERIOD/2) clk = 1'b1;

#(PERIOD/2);

end

initial //对clk,rst进行赋值

begin

clk = 1'b0;

rst = 1'b0;

#100;

rst = 1'b1;

#100;

rst = 1'b0;

#100;

rst = 1'b1;

end

endmodule

(6)点击左侧Run simulation下的Run Behavioral simulation进行仿真。

2.5 生成比特文件,并进行硬件仿真

(1)如下图所示,点击Setting 下的_bin_file,可以保存生成的Bit文件

(2)如图点击Generate Bitstream,工程会自动完成综合、实现、Bit文件生成的工程

(3)点击Open Target,选择Auto Connect连接到板卡。

(4)选择生成的bit文件对FPGA芯片进行编程仿真。

三、 仿真结果

如下图所示,该仿真结果是流水灯循环一个周期的过程。其中高电平表示亮灯,从led[0],led[1]亮起,逐渐向led的高位循环一位,其结果和预期相符。

四、 硬件验证

下图是流水灯实物仿真的其中的一个过程:

五、 问题解决

1.问题:添加的源文件/仿真文件,在保存时,显示有错误警示,并且点击错误查询,总是指向module的第一行。

解决办法:我在源文件/仿真文件命名时,没有太过注意,应该满足: (1) 源文件保存的文件名必须和源文件module后面的文件名一致;(2)仿真文件保存的文件名也必须和仿真文件module后面的文件名一致。

2.问题:添加的仿真程序,在调用源程序时,显示错误。

解决办法:仿真文件里在调用源程序时,‘U0’前那个文件名必须和源文件中module后的文件名一致。其中‘U0’是是模块的命名,没有特定要求。

3.问题:硬件仿真时,不了解其操作流程。

解决办法:在进行硬件仿真时,确实不知道该怎么做,后来询问的同学,才完成流程,出来实验现象。

4.问题:看不懂流水灯源代码的程序,尤其是其中设定的中间24位的参量cnt_reg,不知道他起到的作用是什么。

解决办法:仔细的研读了流水灯的程序,例如<<是左移一位。其中使用cnt_reg,编写的一段程序是为了降低时钟的频率,实现时钟的分频。由于EGO1上时钟的频率是100Mhz,人眼无法识别流水灯的现象,因此需要时钟分频,增大流水灯一次循环的时间,方便人眼识别。文章来源:https://www.toymoban.com/news/detail-778995.html

六、 心得体会

这是我第一次接触Vivado,在进行流水灯的实验中,虽然不用自己编写代码,但是由于并不了解Vivado的开发流程,也是遇到了很多问题,但是最终都顺利的解决了,但是也是感触良多。

首先在进行程序仿真时,总是显示错误,但是程序又没有问题。在这一点上,确实花费了很长的时间,我开始时,逐字逐句的读取了log,error等等,然而并没用找到解决办法。后来百度后,发现可能是杀毒软件的问题,我又试着重新安装了Vivado,最后成功进行了仿真。

再者进行流水灯的实验时,只是按照学习通上的步骤按图索骥完成了实验,不太懂得源程序,仿真程序,约束程序之间的关系。百度查询了一些资料,才知道,其中仿真时,只需要用到源程序,仿真程序,而约束文件是负责连接源程序中端口信号和EGO1板子上对应的引脚的。因此在进行实物仿真时,可以先在Vivado上进行仿真,观察现象是否符合预期。

最后一点体会就是看懂流水灯的程序花了很长时间,但是也对我后续编写源代码提供了很大的助力。文章来源地址https://www.toymoban.com/news/detail-778995.html

到了这里,关于EDA设计:流水灯的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!