2.1 设计输⼊

1. 模块名称:FrequencyDivider

2. 输⼊输出:CLK、RSTn、CLK_15

2.2 引脚约束

1. 输⼊端 ⾃定义

2. 输出端 ⾃定义

2.3 设计要求

1. 输出时钟的周期是输⼊时钟的15倍(15分频器)

2. 分别实现 7/15 占空⽐和 50% 占空⽐两种分频⽅式

3. 使⽤RTL View分析电路的区别

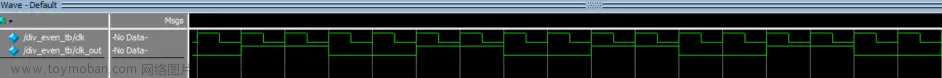

2.4 电路仿真1. 使⽤ModelSim仿真

7:15分频

即分频输出CLK15的一个周期中,高低电平时间之比为 7:8,据此可以在控制输出CLK15的高低电平

设计代码:

module FrequencyDivider(CLK,RSTn,CLK_15);

input CLK,RSTn;

output CLK_15;

reg [3:0]counter_p,counter_n;

reg CLK_p,CLK_n;

assign CLK_15 = CLK_p | CLK_n;

always@(posedge CLK or negedge RSTn)

if(! RSTn) begin

counter_p <= 0;

CLK_p <= 0;

end

else if(counter_p < 14)

begin

counter_p <= counter_p + 1;

if(counter_p < 7)

CLK_p <= 1;

else

CLK_p <= 0;

end

else

counter_p <= 0;

always@(negedge CLK or negedge RSTn)

if(! RSTn) begin

counter_n <= 0;

CLK_n <= 0;

end

else if(counter_n < 14)

begin

counter_n <= counter_n + 1;

if(counter_n < 7)

CLK_n <= 1;

else

CLK_n <= 0;

end

else

counter_n <= 0;

endmodule

(2)50%分频 【是由两个分别由上升沿pos和下降沿neg触发的分频信号合成(或 运算)】

设计代码:

module FrequencyDivider(CLK,RSTn,CLK_15);

input CLK,RSTn;

output CLK_15;

reg [3:0]counter_p,counter_n;

reg CLK_p,CLK_n;

assign CLK_15 = CLK_p | CLK_n;

always@(posedge CLK or negedge RSTn)

if(! RSTn) begin

counter_p <= 0;

CLK_p <= 0;

end

else if(counter_p < 14)

begin

counter_p <= counter_p + 1;

if(counter_p < 7)

CLK_p <= 1;

else

CLK_p <= 0;

end

else

counter_p <= 0;

always@(negedge CLK or negedge RSTn)

if(! RSTn) begin

counter_n <= 0;

CLK_n <= 0;

end

else if(counter_n < 14)

begin

counter_n <= counter_n + 1;

if(counter_n < 7)

CLK_n <= 1;

else

CLK_n <= 0;

end

else

counter_n <= 0;

endmodule

由RTL view可以看出:

CLK_15由或运算得来,由CLK_n和CLK_p相加得来,而两者的区别在于CLK的边沿不同

一个为上升沿,一个为下降沿,因此其中一个D触发器的时钟clk取了一次反

3.创建VWF进行功能仿真:

文章来源:https://www.toymoban.com/news/detail-779092.html

文章来源:https://www.toymoban.com/news/detail-779092.html

文章来源地址https://www.toymoban.com/news/detail-779092.html

文章来源地址https://www.toymoban.com/news/detail-779092.html

到了这里,关于【FPGA & Verilog】奇数分频器 (50%)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!