版本:vivado 2018.3

vivado 自定义封装ip核,可以将ip核封装成带AXI总线,也可将ip核封装成不带AXI总线。

本次设计介绍,如何将当前工程封装成ip核(不带AXI总线)

目录

一、工程文件介绍

二、封装IP核步骤

三、将IP核添加到ip核库

一、工程文件介绍

1. 创建如下的工程:

2. 工程内的.v文件如下:

module uart_rx

#(

parameter integer BPS = 9_600 , //发送波特率

parameter integer CLK_FRE = 50_000_000 //输入时钟频率

)

(

//系统接口

input sys_clk , //50M系统时钟

input sys_rst_n , //系统复位

//UART接收线

input uart_rxd , //接收数据线

//用户接口

output reg uart_rx_done , //数据接收完成标志,当其为高电平时,代表接收数据有效

output reg [7:0] uart_rx_data //接收到的数据,在uart_rx_done为高电平时有效

);

//param define

localparam integer BPS_CNT = CLK_FRE / BPS; //根据波特率计算传输每个bit需要多个系统时钟

//reg define

reg uart_rx_d1 ; //寄存1拍

reg uart_rx_d2 ; //寄存2拍

reg uart_rx_d3 ; //寄存3拍

reg [31:0] clk_cnt ; //计数器,用于计数发送一个bit数据所需要的时钟数

reg [3:0] bit_cnt ; //bit计数器,标志当前发送了多少个bit

reg rx_en ; //接收标志信号,拉高代表接收过程正在进行

reg [7:0] uart_rx_data_reg; //接收数据寄存

//wire define

wire neg_uart_rxd ; //接收数据线的下降沿

assign neg_uart_rxd = uart_rx_d3 & (~uart_rx_d2); //捕获数据线的下降沿,用来标志数据传输开始

//将数据线打3拍,作用1:同步不同时钟域信号,防止亚稳态;作用2:捕获下降沿

always@(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

uart_rx_d1 <= 1'b0;

uart_rx_d2 <= 1'b0;

uart_rx_d3 <= 1'b0;

end

else begin

uart_rx_d1 <= uart_rxd;

uart_rx_d2 <= uart_rx_d1;

uart_rx_d3 <= uart_rx_d2;

end

end

//捕获到数据下降沿(起始位0)后,拉高传输开始标志位,并在第9个数据(终止位)的传输过程正中(数据比较稳定)再将传输开始标志位拉低,标志传输结束

always@(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

rx_en <= 1'b0;

else begin

if(neg_uart_rxd )

rx_en <= 1'b1;

//接收完第9个数据(终止位)将传输开始标志位拉低,标志传输结束,判断高电平

else if((bit_cnt == 4'd9) && (clk_cnt == BPS_CNT >> 1'b1) && (uart_rx_d3 == 1'b1) )

rx_en <= 1'b0;

else

rx_en <= rx_en;

end

end

//当数据传输到终止位时,拉高传输完成标志位,并将数据输出

always@(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

uart_rx_done <= 1'b0;

uart_rx_data <= 8'd0;

end

//结束接收后,将接收到的数据输出

else if((bit_cnt == 4'd9) && (clk_cnt == BPS_CNT >> 1'd1) && (uart_rx_d3 == 1'b1))begin

uart_rx_done <= 1'b1; //仅仅拉高一个时钟周期

uart_rx_data <= uart_rx_data_reg;

end

else begin

uart_rx_done <= 1'b0; //仅仅拉高一个时钟周期

uart_rx_data <= uart_rx_data;

end

end

//时钟每计数一个BPS_CNT(传输一位数据所需要的时钟个数),即将数据计数器加1,并清零时钟计数器

always@(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)begin

bit_cnt <= 4'd0;

clk_cnt <= 32'd0;

end

else if(rx_en)begin //在接收状态

if(clk_cnt < BPS_CNT - 1'b1)begin //一个bit数据没有接收完

clk_cnt <= clk_cnt + 1'b1; //时钟计数器+1

bit_cnt <= bit_cnt; //bit计数器不变

end

else begin //一个bit数据接收完了

clk_cnt <= 32'd0; //清空时钟计数器,重新开始计时

bit_cnt <= bit_cnt + 1'b1; //bit计数器+1,表示接收完了一个bit的数据

end

end

else begin //不在接收状态

bit_cnt <= 4'd0; //清零

clk_cnt <= 32'd0; //清零

end

end

//在每个数据的传输过程正中(数据比较稳定)将数据线上的数据赋值给数据寄存器

always@(posedge sys_clk or negedge sys_rst_n)begin

if(!sys_rst_n)

uart_rx_data_reg <= 8'd0; //复位无接收数据

else if(rx_en) //处于接收状态

if(clk_cnt == BPS_CNT >> 1'b1) begin //传输过程正中(数据比较稳定)

case(bit_cnt) //根据位数决定接收的内容是什么

4'd1:uart_rx_data_reg[0] <= uart_rx_d3; //LSB最低位

4'd2:uart_rx_data_reg[1] <= uart_rx_d3; //

4'd3:uart_rx_data_reg[2] <= uart_rx_d3; //

4'd4:uart_rx_data_reg[3] <= uart_rx_d3; //

4'd5:uart_rx_data_reg[4] <= uart_rx_d3; //

4'd6:uart_rx_data_reg[5] <= uart_rx_d3; //

4'd7:uart_rx_data_reg[6] <= uart_rx_d3; //

4'd8:uart_rx_data_reg[7] <= uart_rx_d3; //MSB最高位

default:; //1和9分别是起始位和终止位,不需要接收

endcase

end

else //数据不一定稳定就不接收

uart_rx_data_reg <= uart_rx_data_reg;

else

uart_rx_data_reg <= 8'd0; //不处于接收状态

end

endmodule 二、封装IP核步骤

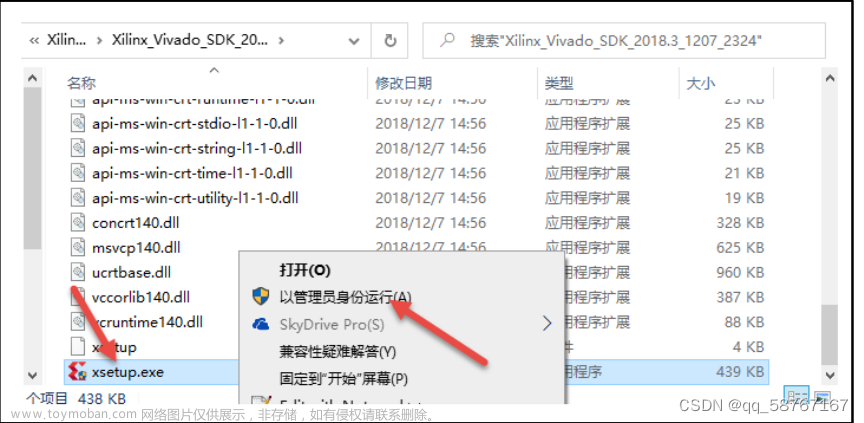

step1: Tools---Great and Package New IP,弹出的界面点击next

step2:选择Package your current project,点击Next

setp3:①选择 ip核存放的位置 ②勾选“include .xci files” ③点击next

setp4:弹出一个总结窗口,点击Next

setp5:弹出Package ip 界面。如果不小心关了这个界面,可以在最左边的“PacgeIP”

Identification:此界面可以修改ip核的名字、ip核展示的名字等等

Compatibility:增加或者删除适用于哪些型号的FPGA芯片,一般默认

File Groups :ip核文件类别,可以选择是否包含 综合和仿真文件

Customization Parameters:双击可配置参数的名字、默认值等等

Ports and Interfaces:ip核的输入和输出端口

Addressing and Memory :ip核的地址,如果PS通过AXI总线访问PL,PS可通过这个地址识别到这个IP核,可以理解为IP核的ID

Customazation GUI : IP核的GUI界面

setp6:Review and Packaga可看到ip核的一些总结信息,点击 "Package IP" ,ip核已经封装完成。

文章来源地址https://www.toymoban.com/news/detail-779177.html

封装完成ip核后,可以在 ip catelog里面搜到到封装完成的ip核,如下:

三、将IP核添加到ip核库

如果想将封装好的ip核,在其他的工程里面使用,还需要将ip核文件添加到ip核库里面。

Settings---IP---Reposilory,选择ip的文件,点击ok

文章来源:https://www.toymoban.com/news/detail-779177.html

到了这里,关于VIVADO 自定义封装ip核(超详细)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[Vivado那些事儿]将自定义 IP (HDL)添加到 Vivado 模块设计(Block Design)](https://imgs.yssmx.com/Uploads/2024/02/783440-1.png)