基于FPGA的EMAC模块与FIFO模块:高速数据传输与存储

在现代社会,高速数据传输和存储是信息技术领域的关键问题之一。而基于FPGA的EMAC模块与FIFO模块则成为了解决这些问题的重要途径。本文将介绍这两个模块的原理、实现方法以及如何在FPGA中应用它们。

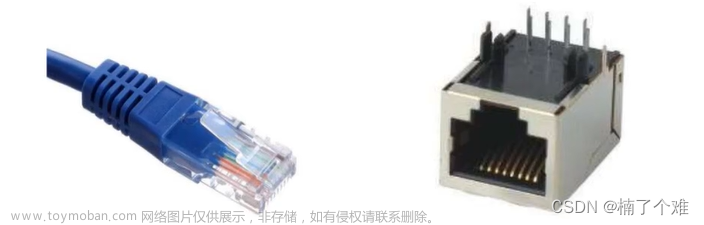

EMAC模块是以太网MAC控制器模块,其作用是实现以太网的发送和接收功能。它的实现原理是通过调用底层硬件和协议栈完成数据包的组装和解析,从而实现数据的传输。在FPGA中,我们可以使用Verilog HDL语言编写EMAC模块的代码,并将其综合到FPGA芯片中。下面是一个简单的EMAC模块的Verilog代码:

module EMAC (

input clk, rst,

input [31:0] rx_data,

input start_rx,

output [31:0] tx_data,

output start_tx,

output [3:0] status

);

// 实现代码

endmodule

上面的代码定义了一个EMAC模块,其中包括时钟、复位、接收数据、发送数据等信号。需要注意的是,EMAC模块的实现要考虑到网络通信中的多种协议,如TCP、UDP等,以保证数据的正确传输。因此,在实际应用中需要根据具体的需求进行调整。

FIFO模块则是一种先进先出的数据缓存模块,用于暂存来自EMAC模块的数据,并在需要时进行读取。它可以解决高速数据传输中出现的速度不匹配问题,提高了系统的稳定性和可靠性。同样地,我们也可以使用Verilog HDL语言编写FIFO模块的代码,并将其综合到FPGA芯片中。下面是一个简单的FIFO模块的Verilog代码:

module FIFO (

input clk, rst,

input [31:0] write_data,

input write_en,

output reg [31:0] read_data,

input read_en

);

// 实现代码

endmodule

上述代码定义了一个FIFO模块,其中包括时钟、复位、写入数据、读取数据等信号。这个FIFO模块的实现采用了一个简单的双指针队列,可以满足大多数数据缓存的需求。但如果需要更高的性能和更严格的保障,还需要对数据缓存的具体实现进行深入的研究与优化。

在FPGA中,我们可以将EMAC和FIFO两个模块结合起来,构建一个高速数据传输和存储系统。例如,我们可以使用EMAC模块实现网络数据的接收和发送,同时使用FIFO模块进行数据存储和读取。这样的系统可以支持高速网络通信、流媒体传输等应用场景。文章来源:https://www.toymoban.com/news/detail-779661.html

综上所述,基于FPGA的EMAC模块与FIFO模块提供了一种高效、可靠的数据传输和存储方案。通过结合这两个模块,我们可以构建出各种具有不同功能和性能的系统,解决多种数据传输和存储问题。文章来源地址https://www.toymoban.com/news/detail-779661.html

到了这里,关于基于FPGA的EMAC模块与FIFO模块:高速数据传输与存储的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!