前言

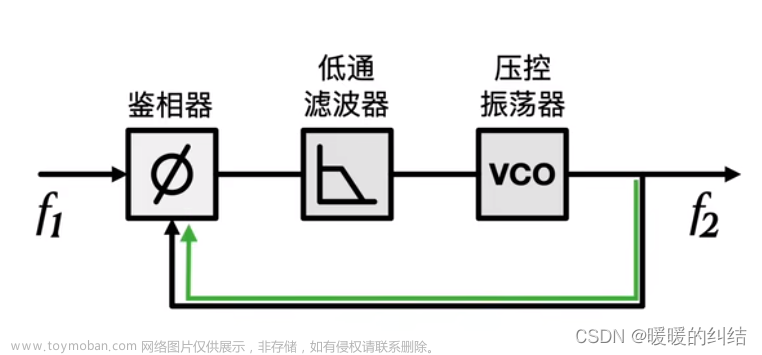

数字锁相环是锁相环电路的全数字实现。锁相环电路能够实现对输入信号的相位进行跟踪,进而在噪声中提取纯净的有用信号。

一、数字锁相环原理

1.1 数字鉴相器

数字鉴相器由乘法器和低通滤波器构成,又称为正弦形式的鉴相器。数字鉴相器有一重要指标——鉴相增益 K d K_d Kd,又可表示为鉴相器输出的最大电压。

1.2 环路滤波器

环路滤波器将鉴相器输出的含有纹波的信号平均化,将其转换为交流信号少的直流信号的低通滤波器。除此之外,还能控制环路特性,提供环路增益。

1.3 压控振荡器

压控振荡器的原理是,通过输入控制信号的大小,来控制其输出信号的频率变化。

1.4 二阶数字锁相环参数计算

锁相环环路传输模型:

具体推导请参杜勇老师的锁相环技术原理及FPGA实现和数字调制解调技术的Matlab与FPGA实现两本书,这里给出书中最终结果的计算公式。

以理想二阶环(有源比例积分滤波器)为例,计算环路滤波器的参数C1和C2,最后可取近似得二进制数

2

−

N

2^{-N}

2−N,采取对环路滤波器输入数据向右移动N位近似使用。

C

1

=

2

τ

2

+

T

2

τ

1

,

C

2

=

T

τ

1

C_1 = \dfrac{2\tau_2 + T}{2\tau_1}, C_2 = \dfrac{T}{\tau_1}

C1=2τ12τ2+T,C2=τ1T

ω

n

=

K

τ

1

,

ε

=

τ

2

2

K

τ

1

\omega_n = \sqrt{\dfrac{K}{\tau_1}}, \varepsilon = \dfrac{\tau_2}{2}\sqrt{\dfrac{K}{\tau_1}}

ωn=τ1K,ε=2τ2τ1K

其中,K为锁相环增益,T为输入信号的采样周期,

ω

n

\omega_n

ωn为固有振荡频率,

ε

\varepsilon

ε为阻尼系数,为保证较好的相位裕度,

ε

\varepsilon

ε一般取0.7。

根据上述表格和公式,计算得,

C

1

≈

2

ε

ω

n

T

K

C_1\approx\dfrac{2\varepsilon\omega_nT}{K}

C1≈K2εωnT,

C

2

≈

(

ω

n

T

)

2

K

C_2\approx\dfrac{(\omega_nT)^2}{K}

C2≈K(ωnT)2

假设环路滤波器的3dB截止带宽为

f

c

f_c

fc,则

f

c

=

2

τ

1

2

−

2

τ

2

2

f_c=\sqrt{\dfrac{2}{\tau_1^2-2\tau_2^2}}

fc=τ12−2τ222

关于固有振荡频率,

△

ω

L

2

ε

<

ω

n

<

8

ε

(

S

/

N

)

i

B

i

(

S

/

N

)

L

\dfrac{\triangle\omega_L}{2\varepsilon}<\omega_n<\dfrac{8\varepsilon(S/N)_iB_i}{(S/N)_L}

2ε△ωL<ωn<(S/N)L8ε(S/N)iBi,且

ω

n

f

s

≪

1

\dfrac{\omega_n}{f_s}\ll1

fsωn≪1,其中

(

S

/

N

)

i

(S/N)_i

(S/N)i和

(

S

/

N

)

L

(S/N)_L

(S/N)L分别为中频输入信号信噪比和环路信噪比,一般都要满足大于6dB,

B

i

B_i

Bi为中频信号带宽。

二、数字锁相环的FPGA实现

这里以二阶锁相环为例(采用理想二阶环),压控振荡器初始频率为2.4kHz,锁相环输入信号为2.5kHz,采样频率为50kHz(Vivado中DDS输入系统时钟的最小频率)。

2.1 鉴相器实现

使用IP核为Multiplier核和FIR Filter核。

主要代码如下:

// parameter Start_Frequency = 24'd838860; // 2.5 KHz, 输入信号

parameter Start_Frequency = 24'd805306; // 2.4 KHz,DDS初始频率输出

// 限幅处理

reg signed [9:0] din_d;

always@(posedge i_clk)

if(i_data == 10'b10_0000_0000)

din_d <= 10'b10_0000_0001;

else

din_d <= i_data;

// 实例化鉴相乘法器IP核

wire signed [9:0] sine, cosine;

wire signed [19:0] mult_out;

mult_gen_0 u0(

.CLK(i_clk),

.A(din_d),

.B(cosine),

.P(mult_out)

);

// 实例化鉴相滤波器IP核

wire s_axis_data_tready, s_axis_data_tvalid, m_axis_data_tvalid, aresetn;

wire signed [31:0] pd_Filter_out;

assign s_axis_data_tready = 1'b1;

assign s_axis_data_tvalid = 1'b1;

assign aresetn = i_rst_n;

fir_compiler_0 u1(

.aresetn(aresetn),

.aclk(i_clk),

.s_axis_data_tvalid(s_axis_data_tvalid),

.s_axis_data_tready(s_axis_data_tready),

.s_axis_data_tdata(mult_out[18:0]),

.m_axis_data_tvalid(m_axis_data_tvalid),

.m_axis_data_tdata(pd_Filter_out)

);

2.2 环路滤波器实现

根据环路滤波器参数

C

1

C_1

C1和

C

2

C_2

C2的数值,采用两次右移位运算,并做叠加。

通过环路滤波器,为锁相环提供环路增益

K

0

K_0

K0。

主要代码如下:

module LoopFilter(

i_clk,

i_rst_n,

i_pd,

o_frequency_df

);

input i_clk; // 系统时钟,50KHz

input i_rst_n; // 复位信号,低电平有效

input signed [23:0] i_pd; // 输入信号频率,50KHz

output signed [23:0] o_frequency_df; // 环路滤波器输出信号

reg signed [23:0] sum_d;

wire signed [23:0] pd_c2, pd_c1,sum;

assign pd_c1 = {{4{i_pd[23]}},i_pd[23:4]}; //c1

assign pd_c2 = {{11{i_pd[23]}},i_pd[23:11]}; //c2

always@(posedge i_clk or negedge i_rst_n)

if(!i_rst_n)

sum_d <= 0;

else

sum_d <= sum;

assign sum = pd_c2 + sum_d;

assign o_frequency_df = sum_d + pd_c1;

endmodule

2.3 压控振荡器实现

使用IP核为DDS核。

主要代码如下

// 实例化DDS核

wire reset_n,out_valid,clken;

wire signed [23:0] carrier;

wire signed [31:0] sine_cos;

assign sine = sine_cos[25:16];

assign cosine = sine_cos[9:0];

assign clken = 1'b1;

assign carrier = Start_Frequency + frequency_df;

dds_compiler_0 u2(

.aclk(i_clk),

.aclken(clken),

.aresetn(i_rst_n),

.s_axis_config_tvalid(1'b1),

.s_axis_config_tdata(carrier),

.m_axis_data_tvalid(out_valid),

.m_axis_data_tdata(sine_cos)

);

2.4 仿真结果

仿真平台:Vivado 2018.3

各模块:数字鉴相器(乘法器+低通滤波器),环路滤波器,压控振荡器

主要使用IP核:Multiplier,FIR Compiler,dds_compiler

二阶锁相环整体仿真图如下。

二阶锁相环局部仿真图如下(锁定后)。

总结

以上就是今天要讲的内容,本文简单地介绍了锁相环的原理,并通过verilog做仿真验证。最终仿真结果能够实现锁定,但锁定时间较长,表明参数仍可做调整。

参考书

1,杜勇,锁相环技术原理及FPGA实现;

2,杜勇,数字调制解调技术的Matlab与FPGA实现(Atera/verilog版)。文章来源:https://www.toymoban.com/news/detail-780648.html

二阶数字锁相环的FPGA实现的完整工程文件 文章来源地址https://www.toymoban.com/news/detail-780648.html

到了这里,关于数字锁相环的原理与FPGA实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!