前言

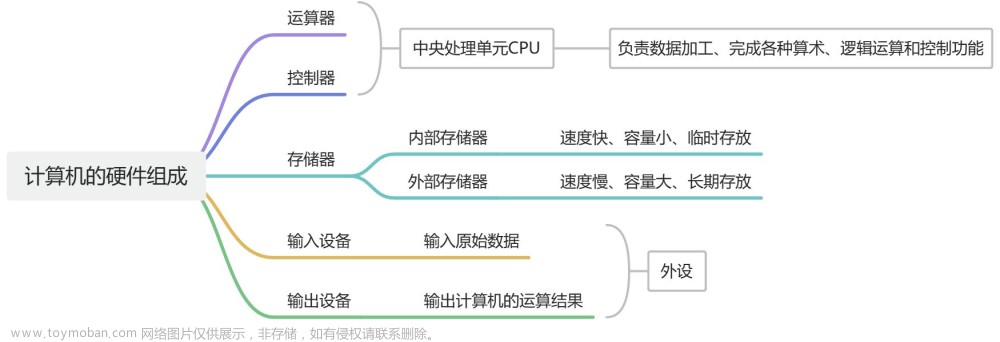

本章继续讲述计算机硬件系统设计的内容,之前已经大概说明了 ALU 和存储系统的设计,本文讲述CPU的设计。对应的有单周期、多周期 CPU 设计,以及流水线设计,中断处理会在后文中详细说明,本文不进行讲述。

单周期 CPU 设计

数据通路

即定长指令周期,机器性能取决于最慢的指令,导致时钟周期过长。

指令类型分为三类,R型指令、I型指令、J型指令。

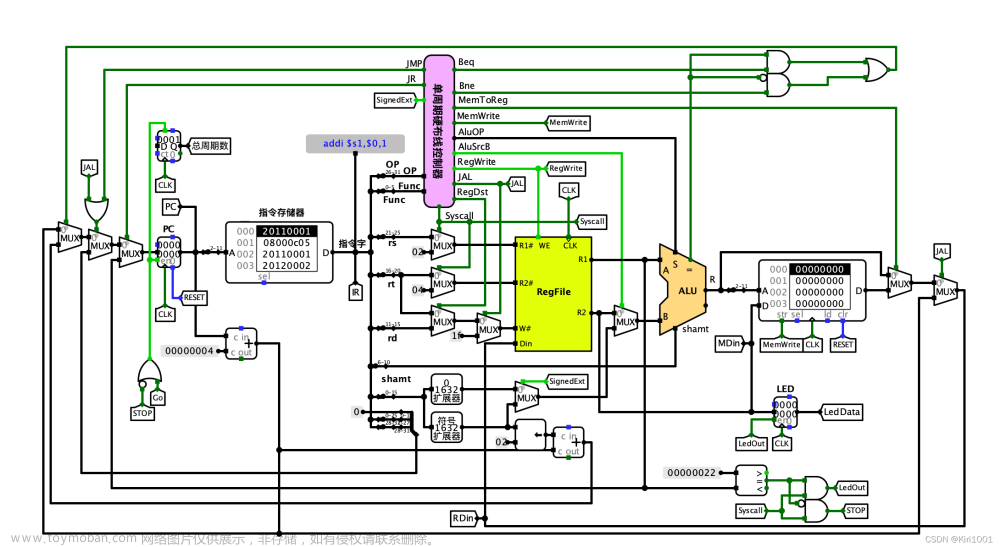

数据通路如下

最左侧多路选择器,当执行有条件跳转指令时,选择跳转地址,跳转地址由15位的立即数运算得到;下一层为无条件跳转指令选择,当执行JAL(函数调用指令)或J(无条件跳转指令)选择由26位立即数运算得到的地址;第三层选择为JR指令(跳转到寄存器记录地址,一般用于在JAL调用退出时使用),一般选择$31号寄存器保存JAL执行时PC的值,函数调用后,再读取 $31 的值进行返回。

本设计支持24条指令,这里不一一介绍,有疑问可以评论共同探讨学习。

控制器设计

控制器是通过分解指令,由OP和FUNC字段确定某种运算,给出控制信号,协同数据通路的工作,确保数据的正确流通。

控制器设计方法可以使用硬布线设计,也可以采用微程序设计。

第一步需要分析指令在执行过程需要的控制信号,之后根据分析,设计电路,使用课程包中的EXCEL,填写输入信号,生成控制器电路,以设计控制器。 由上图 指令-控制信号 得到控制信号生成表达式

由上图 指令-控制信号 得到控制信号生成表达式

将逻辑表达式输入,自动生成电路。

最后导入程序测试功能。

MIPS 指令流水线设计

理想流水线

理想流水线满足以下特点:阶段数相同,所有指令经过同样的流程、阶段;各段时延相同,各段传输延迟一致,不存在等待现象,所以设计时考虑最慢的处理过程;无资源冲突,各段之间不存在资源共享,各段完全并发;无段间互锁,进入流水线的数据与部件不受其他执行阶段的影响。

这里不在介绍各段的执行流程,细节参考MOOC课程。

流水接口部件设计

流水接口部件实际为寄存器的组合设计,用于暂存数据,本段输出处理好的数据暂存于寄存器,寄存器为后段提供数据。

考虑设计不同位数的接口部件,方便后期直接使用,同时注意使用同步清零,防止异步清零时丢失数据。

气泡流水线

在执行跳转指令时,由于前段已经加载其他指令,属于误取指令,故需要进行处理。这里介绍采用插入气泡的方法解决问题。这会导致流水行性能损失。

当判断流水线执行跳转指令时,取指阶段于译码阶段设计同步清零信号,清空流水线保证指令正确执行。

当流水段出现数据相关问题时,也可以采用插入气泡的方法解决问题。

数据重定向

使用气泡解决冲突问题时,流水线会有性能损失,故而可以采用数据重定向方法解决该类问题。

主体思路是通过寄存器使用检查,确定段间的争用关系,通过设计电路,完成数据重定向。

寄存器使用检查

通过之前设计完成的控制信号生成文件,只关注RegDst信号与RegWrite信号,即输入为6位OP字段,6位FUNC字段,输出两个寄存器信号。

寄存器冲突检测

通过设计好的寄存器检查电路组件,设计比较电路。

数据重定向实现

总结

本文仅提供设计思路,如有错误还请指正,也希望各位读者可以提供宝贵意见与指导,共同探讨学习。设计不尽完善,还有许多需要改进的地方,希望拙笔可以抛砖引玉,之后可以出现更多完善优秀的设计提供参考。文章来源:https://www.toymoban.com/news/detail-781255.html

本人也因对硬件设计极为感兴趣,欢迎各位提问交流,最后也衷心祝愿各位读者万事胜意,身体健康。文章来源地址https://www.toymoban.com/news/detail-781255.html

到了这里,关于【计算机硬件系统设计(华科)——单周期MIPS CPU(Logisim 实现)】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!