实验四 32位MIPS CPU设计实验

这次实验是32位MIPS CPU设计实验(单总线CPU-定长指令周期-3级时序),在头歌当中一共需要我们进行六道题的测试,分别为MIPS指令译码器设计,定长指令周期(时序发生FSM设计,时序发生器输出函数设计,硬布线控制器,单总线CPU设计),硬布线控制器组合逻辑单元。其中由于第六题是对前面五题一个最终的检验,所以我们不需要进行新的设计,这边我按照老师给的提纲分享了以下四个实验的具体设计原理:1、指令译码器电路设计 2、时序发生器状态机(定长指令周期)设计3、时序发生器输出函数(定长指令周期)4、硬布线控制器

1指令译码器电路设计

1.1设计要求

了解指令译码的基本概念,将32位MIPS指令字译码成不同的指令译码信号。利用logisim平台中现有运算部件构建利用比较器等功能模块将32位MIPS 指令字译码生成LW、SW、BEQ、SLT、ADDI、OtherInstr等指令译码信号,早给定CPU中实现支持以上指令的电路

1.2方案设计

1.2.1 指令作用

首先我们需要了解到这六条MIPS指令的作用,其中所有的imm立即数都需要括展到32位

Lw指令作用:从数存(数据存储器)中取数据写进寄存器

Sw指令作用:将寄存器中的值写入数存

Beq指令作用:当寄存器1的值和寄存器2的值相等时发生跳转,跳转的目的地址位当前指令的地址加上符号括展的imm的值

ADDI指令作用:用于寄存器中数值加上常数

Slt指令作用:比较rs和rt两个寄存器中的值,如果rs中的值小于rt中的值,则把rd计算器置一,否则把rd计算器清零

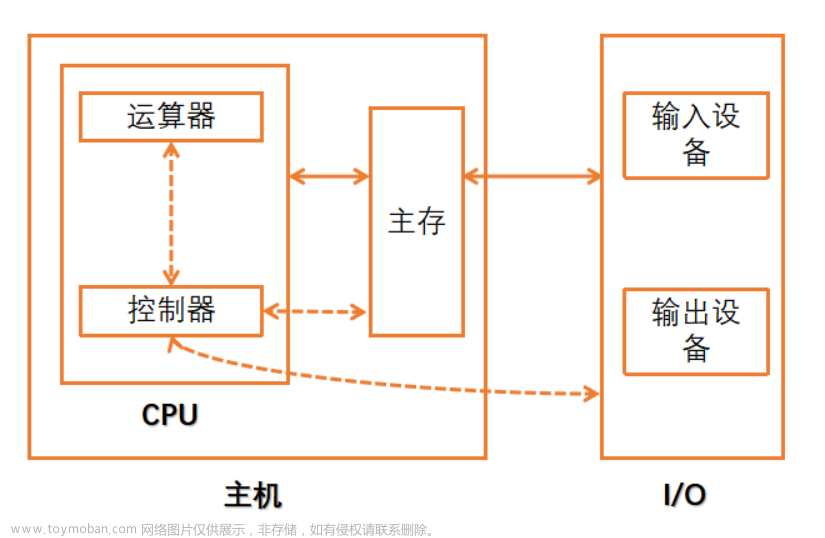

1.2.2 单总线CPU原理

这次使用为单总线CPU

首先我们看以下单总线结构CPU在logisim中的实现,我们可以看到在实际logisim,使用了slt信号控制alu进行比较rs和rt两个寄存器中的值的大小,本次简单的CPU实验,不需要sub信号,但是sub信号在A输入引脚可以进行连接,大家可以在下图寻找,当前并没有使用,psw寄存器只保留了一位equal的控制位,psw中并没有设计其余的状态标记,ALU的每一次运算都会比较x和y,在这边呢,就是A和B引脚输出的两个值的大小是否相等,并通过psw寄存器输出equal信号

1.2.3 指令译码原理

指令译码器是控制器核心功能部件,实现译码功能,负责将指令字翻译成一根根的指令译码信号,每一根指令译码信号代表一条具体的指令,如上图中的I1…Im。根据指令码的特定信息,译码产生指令译码信号,时钟产生器承担了持续控制的功能生成状态周期M和时钟节拍T,控制器利用这些持续信号,对操作信号进行持续调制。

1.2.4 设计思路

将指令寄存器IR送来的32位指令字,生成指令译码信号,当前IR中存放的是哪一种指令,讲过译码器之后,就应该令相应的引脚置一,而其余输出引脚为0

那么这边是利用比较器等功能模块将32位MIPS指令字译码对应生成指令译码信号,用比较器将IR送来的指令字的op字段,和已由分线器提取出的op字段,其中题目将各个op部分对应的常量值已经给出,我们需要对应指令码结构,将对应的op字段送到比较器,相比较之后的输出结果就连到相应的指令当中

1.3实验步骤

- 打开源程序,查看控制器的输入引脚,还有其他重要的输出引脚

- 查看指令码结构,与系统自带的op字段,然后进行连接

- 输出相应经过比较之后输出的指令结果

1.4故障与调试

1.4.1 slt连接问题

故障现象:slt信号的译码条件有两个,连线时发生问题

原因分析:slt信号的译码条件有两个,分别是op和0,以及funct字段的值是固定的十进制44,这两个条件需要同时成立,slt引脚才能输出1,那么两个条件同时成立,连线方式较其他的指令有点复杂

解决方案:在00另一边连的是op,funct旁边连接2a,这样就是正确的连接方式。

1.5测试与分析

溢出测试用例见表 1.3 。

表 1.3溢出信号测试用例

Cnt IR LW SW BEQ ADDI SLT OtherI

- 0000 2010ffff 0 0 0 1 0 0

- 0001 20110000 0 0 0 1 0 0

- 0002 ae300200 0 1 0 0 0 0

- 0003 22100001 0 0 0 1 0 0

- 0004 22310004 0 0 0 1 0 0

- 0005 ae300200 0 1 0 0 0 0

- 0006 22100001 0 0 0 1 0 0

- 0007 22310004 0 0 0 1 0 0

- 0008 ae300200 0 1 0 0 0 0

- 0009 22100001 0 0 0 1 0 0

- 000a 22310004 0 0 0 1 0 0

- 000b ae300200 0 1 0 0 0 0

- 000c 22100001 0 0 0 1 0 0

- 000d 22310004 0 0 0 1 0 0

- 000e ae300200 0 1 0 0 0 0

- 000f 22100001 0 0 0 1 0 0

- 0010 22310004 0 0 0 1 0 0

- 0011 ae300200 0 1 0 0 0 0

- 0012 22100001 0 0 0 1 0 0

- 0013 22310004 0 0 0 1 0 0

- 0014 ae300200 0 1 0 0 0 0

- 0015 22100001 0 0 0 1 0 0

- 0016 22310004 0 0 0 1 0 0

- 0017 ae300200 0 1 0 0 0 0

- 0018 20100000 0 0 0 1 0 0

- 0019 2011001c 0 0 0 1 0 0

- 001a 8e130200 1 0 0 0 0 0

- 001b 8e340200 1 0 0 0 0 0

- 001c 0274402a 0 0 0 0 1 0

- 001d 11000002 0 0 1 0 0 0

- 001e ae330200 0 1 0 0 0 0

- 001f ae140200 0 1 0 0 0 0

- 0020 2231fffc 0 0 0 1 0 0

- 0021 12110001 0 0 1 0 0 0

- 0022 1000fff7 0 0 1 0 0 0

- 0023 22100004 0 0 0 1 0 0

- 0024 2011001c 0 0 0 1 0 0

- 0025 12110001 0 0 1 0 0 0

- 0026 1000fff3 0 0 1 0 0 0

- 0027 1000ffff 0 0 1 0 0 0

- 0028 00000000 0 0 0 0 0 1

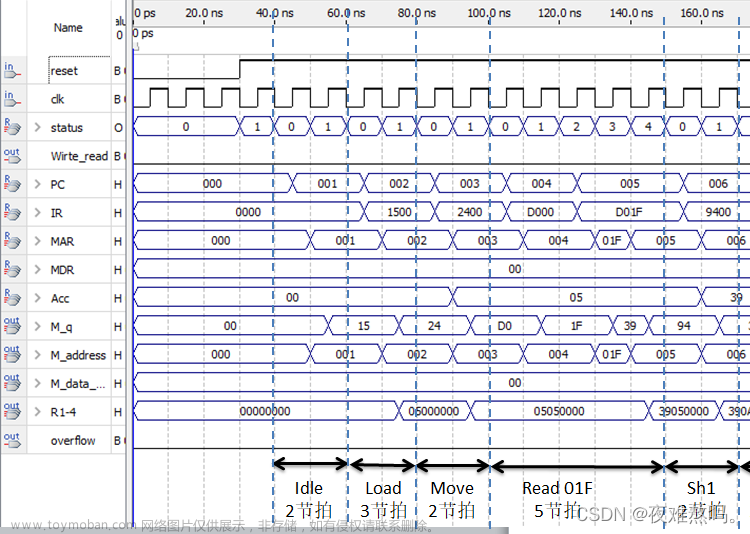

2时序发生器状态机(定长指令周期)设计

2.1设计要求

利用数字逻辑电路相关知识设计定长指令周期的三级时序系统,时序发生器包括状态机和输出函数两部分,设计状态机。

上一关实现了指令译码器后,就可以开始实现上图中的另外一个核心功能模块,时序发生器了,时序发生器内部框图如下图所示,主要包括状态寄存器,状态机组合逻辑,输出函数组合逻辑三部分。其中状态机负责现态与次态的转换,输出函数根据当前状态生成状态周期电位和节拍周期电位。

2.2方案设计

2.2.1时序产生器原理

其实这个原理较为简单,只需要了解这张图片就可以了,我们针对单总线架构cpu设计的定长指令周期的三级时序系统,由机器周期,节拍电位构成。其中机器周期用于表示当前指令处于哪一个周期,取指令周期mif,持续四个周期t,t1,t2,t3,t4之后变为低电平,而同时Mcal计算周期变成高电平,表示指令执行进入了计算周期,然后计算周期经过t1,t2,t3,t4,四个时钟节拍之后,变为低电平无效。同时进入执行周期,执行周期执行完4个节拍之后,又进入到取指周期,以此往复不断的循环,从而实现程序的自动执行,而节拍电位t1,t2,t3,t4。每一个t完成一个微操作

2.2.2状态寄存器原理

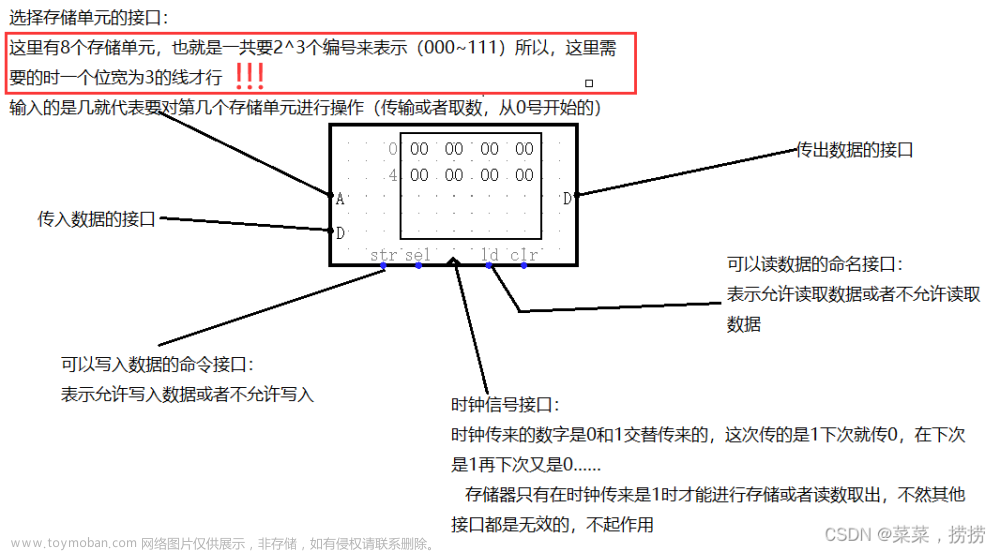

作用是把三个状态周期,总共12个节拍的三级时序系统,简化成12个状态来进行表示,如下图所示,用s0表示取指令周期的第一个节拍,以此类推,一共12状态。每一个次态和输入的现态都是加1的关系,本质上是计数器.通过下图我们可以得到m和t与现态之间的关系

2.2.3 设计思路

由此可见,现态和次态的真值表,从而得到次态与输入信号和现态之间的逻辑表达式,从而可以是实现状态机的组合逻辑设计,组合时序只与输入的现态有关系的,所以只需要一个一个的进行累加就行,并且还需要将相应的excel文件填写完成,之后将生成的逻辑表示式输入就可以了

2.3实验步骤

1)清楚了解状态机,知道m和t与现态之间的关系

2)将表格单总线MIPS三级时序产生器逻辑自动生成当中,最左侧的状态转换表填完完成,就是我们实现状态机设计,所对应的真值表,这个表我们只需要填写现态,为十进制的现态值,以及十进制的次态值就可以了,其中现态二进制s3-s0的值,与次态n3-n0的值会自动生成

填写完成如下表

3)通过表格触发器输出函数,自动生成逻辑表达式,复制我圈起来部分的内容,将其粘贴到logisim当中

4)点击logisim当中的时序发生器状态机(定长指令周期),然后点击分析组合逻辑电路

5)将在文件中复制的逻辑表达式,按照n3-n0的顺序,粘贴到下图当中,全部输入之后,点击生成电路

6)点击生成电路,进行测试

2.4故障与调试

这个实验没有遇到问题,较为简单

2.5测试与分析

测试用例如下,实验电路通过所有测试用例

3时序发生器输出函数(定长指令周期)设计

3.1设计要求

理解传统三级时序系统中时序发生器的基本原理,设计定长指令周期的时序发生器状态机以及输出函数。利用数字逻辑电路相关知识设计定长指令周期的三级时序系统,时序发生器包括状态机和输出函数两部分,上一实验完成了状态机的设计,这一实验要求我们实现输出函数的设计部分,设计实现输出函数组合逻辑。

3.2方案设计

3.2.1实际产生器原理

实际发生器组合逻辑,是根据当前输入的现态输出Mif,Mcal,Mex,以及T1到T4的节拍电位,与状态机用同样的方法填写,四个事态为一周期,其中第一阶段Mif=1,T1-T4依此为1,第二阶段,Mcal=1,其他置零,第三阶段,Mex=1.填写同一个表格当中的输出函数表,填好这个表之后,通过输出函数自动生成,表中可以自动获取我们的Mif,Mcal,Mex,T1到T4的逻辑表达式了,把相应的逻辑表达式复制之后,思路与下图相同

3.2.1设计思路

据当前输入的现态输出Mif,Mcal,Mex,以及T1到T4的节拍电位,与状态机用同样的方法填写,填写同一个表格当中的输出函数表,填好这个表之后,通过输出函数自动生成,表中可以自动获取我们的Mif,Mcal,Mex,T1到T4的逻辑表达式了,帮相应的逻辑表达式复制之后, 开始运行

3.3实验步骤

1)了解实际产生器原理,得出每个时期内Mif,Mcal,Mex在不同周期内数值的变化情况

2)根据上一步的数值的变化,将文件表中的输出函数真值表填写完成

3)将表填写完成之后,将其自动生成函数输入进logisim

4)运行电路进行检测

3.4故障与调试

3.4.1 复制出错

故障现象:输出函数真值表填写正确,但是在头歌网进行测评时,答案不正确

原因分析:再次检查函数真值表的填写,发现的确是正确的,那说明只能是复制错了

解决方案:再进行一次复制,结果正确

3.5测试与分析

测试用例如下,实验电路通过所有测试用例

4硬布线控制器设计

4.1设计要求

理解传统三级时序系统中硬布线控制器的设计原理,设计硬布线控制器组合逻辑单元,在实现了指令译码逻辑、时序发生器主要功能部件后,进一步设计实现控制器核心模块硬布线控制器组合逻辑单元

4.2方案设计

4.2.1设计思路

在实现了指令译码逻辑、时序发生器主要功能部件后,进一步设计实现控制器核心模块硬布线控制器组合逻辑单元, 列出所有微操作信号的产生条件,填写下面的excel表格,自动生成逻辑表达式,然后再Logisim中自动生成电路。

4.2.2硬布线控制器组合逻辑

在设计完上面的两个实验之后,就需要设计硬布线控制器的核心组合逻辑单元了,由于时序产生器以及承担了时序控制功能,所以硬布线控制器就变成了一个存组和逻辑,每一个控制信号c都是指令。所以我们只需要弄清楚各个操作控制信号其所产生的调节,就可以得到他们的逻辑表达式

4.2.3信号产生条件

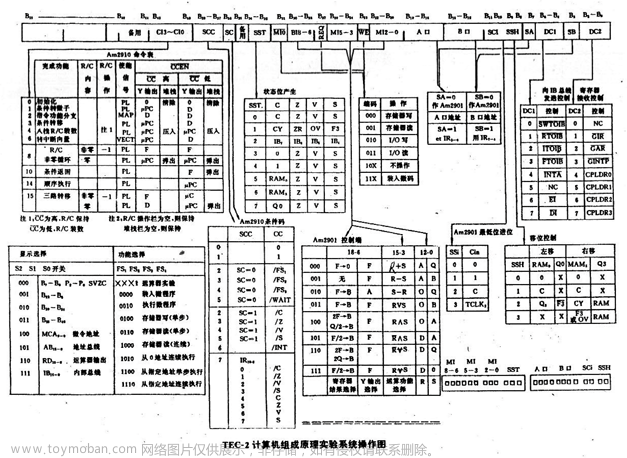

如下图所示,通过前面的数据通路分析,得到五条不同指令,在取指令周期,计算周期,执行周期的不同节拍中,会给出不同的控制信号。这边是所有控制信号的产生条件,需要将下面两图结合来看。所有的控制信号的逻辑表达式,cpu电路重法所有控点的逻辑表达式,是需要经过化简得

4.3实验步骤

1)理解上面两图

2)进行表格状态的填写

3)将生成的表达式复制进logisim,生成电路

4)然后进行测评

4.4.1 复制出错

故障现象:输出函数真值表填写正确,但是在头歌网进行测评时,答案不正确

原因分析:再次检查函数真值表的填写,发现的确是正确的,那说明只能是复制错了

解决方案:再进行一次复制,结果正确文章来源:https://www.toymoban.com/news/detail-781368.html

4.5测试与分析

测试用例如下,实验电路通过所有测试用例 文章来源地址https://www.toymoban.com/news/detail-781368.html

文章来源地址https://www.toymoban.com/news/detail-781368.html

到了这里,关于计算机组成原理32位MIPS CPU设计实验(指令译码器电路设计 、时序发生器状态机设计、时序发生器输出函数、硬布线控制器)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!