Vivado 10G Ethernet PCS/PMA介绍

1介绍

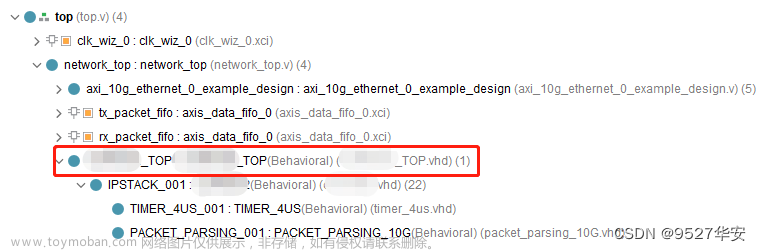

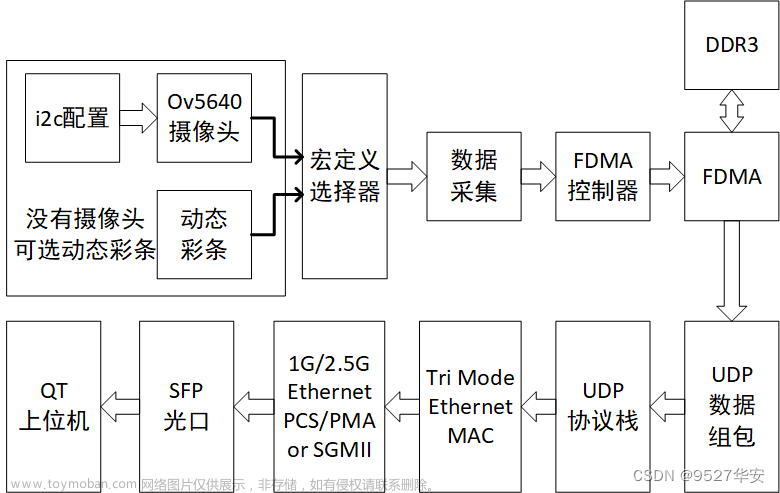

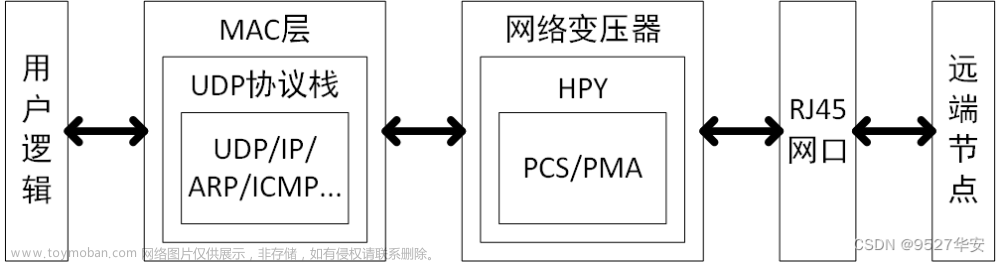

完整的10G以太网接口如下图,分为10G PHY和10G MAC两部分。

这篇文章重点讲 10G Ethernet PCS/PMA。文章来源:https://www.toymoban.com/news/detail-781736.html

2 IP的基本介绍

10G以太网物理编码子层/物理介质连接(PCS/PMA)核心在Xilinx 10G以太网介质访问控制器(MAC)核心和具有10Gb/s能力的PHY之间形成了无缝接口,实现了高速以太网系统和子系统的设计。文章来源地址https://www.toymoban.com/news/detail-781736.html

•根据万兆以太网规范设计IEEE标准802.3-2012第49、72、73、74条

•管理PCS/PMA寄存器的可选管理数据接口(MDIO)

•支持Zynq-7000、UltraScale中的10GBASE-SR、-LR和-ER光链路™, Virtex-7和Kintex-7设备(仅限LAN模式)

•支持UltraScale和Virtex-7设备中的10GBASE-KR背板链路,包括自动协商(AN)、训练和前向纠错(FEC)

•万兆以太网媒体独立接口(XGMII)与Xilinx万兆以太网MAC无缝连接

•10GBASE-R标准提供64位或32位数据宽度选项。10GBASE-KR标准始终提供64位数据宽度

到了这里,关于Xilinx IP 10G Ethernet PCS/PMA IP Core的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!