-

实验目的

- 掌握二进制计数器的工作原理。

- 能使用verilog设计计数器。

3、进一步熟悉QUARTUSII软件的使用方法和verilog输入方式

- 实验原理与内容

- 实验原理

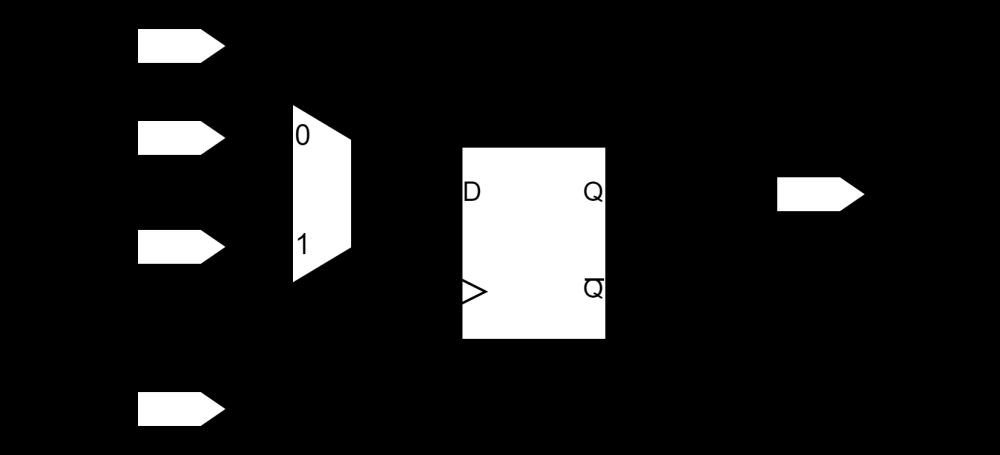

二进制计数器中应用最多、功能最全的计数器之一,是含异步清零和同步使能的具有并行载入功能的加/减法计数器。其具体工作过程如下:

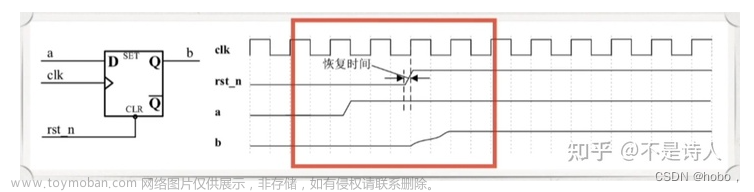

复位信号有效(低电平有效)时,计数值清零。并行载入控制信号有效时,并行数据输入端的数据存入计数器中。使能信号有效时,根据加减法控制信号来进行加法或者减法计数。具有并行载入数据功能的4位加法计数器原理图如图所示。请参考该图,设计具有异步复位和加/减法功能的计数器。

2.实验内容

本实验要求完成的任务是使用verilog和Quartus II,设计一个4位2进制计数器,并在可编程逻辑器件中实现。在时钟信号的作用下,通过加减控制信号、使能端、并行载入控制信号和复位信号来控制完成加/减法计数和并行载入数据的功能。实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用一位拨动开关K2表示加减控制信号,用一位拨动开关K3表示并行载入数据控制信号,用拨动开关K4~K7表示4位并行载入数据,用复位开关S1表示复位信号,用LED模块的LED1~LED4来表示4位计数器的二进制计数值,用LED12表示加/减法计数时的进位/借位信号。实验LED亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。通过输入不同的值实现计数器的工作时序,观察计数的结果。

数字时钟信号模块的电路原理如图所示,

下表是其时钟输出与FPGA的管脚连接表。

| 信号名称 |

对应FPGA管脚名 |

说明 |

| DIGITAL-CLK |

K7 |

数字时钟信号送至FPGA的K7 |

按键开关模块的电路原理如下图所示,下表是按键开关的输出与FPGA的管脚连接表。

| 信号名称 |

FPGA I/O名称 |

核心板接口管脚号 |

功能说明 |

| S[0] |

Pin_B12 |

JP1_79 |

‘S1’ Switch |

| S[1] |

Pin_B11 |

JP1_77 |

‘S2’ Switch |

| S[2] |

Pin_V4 |

JP3_56 |

‘S3’ Switch |

| S[3] |

Pin_T4 |

JP3_52 |

‘S4’ Switch |

| S[4] |

Pin_P3 |

JP3_48 |

‘S5’ Switch |

| S[5] |

Pin_AB11 |

JP3_40 |

‘S6’ Switch |

| S[6] |

Pin_A12 |

JP3_78 |

‘S7’ Switch |

| S[7] |

Pin_A11 |

JP3_76 |

‘S8’ Switch |

| S[8] |

Pin_V5 |

JP1_55 |

‘S9’ Switch |

| S[9] |

Pin_T3 |

JP1_51 |

‘S10’ Switch |

| S[10] |

Pin_AA12 |

JP3_43 |

‘S11’ Switch |

| S[11] |

Pin_T1 |

JP3_11 |

‘S12’ Switch |

三.实验过程

1.打开QUARTUSII软件,新建一个名为exp2的工程

2.建完工程之后,再新建一个verilog文件,打开verilog编辑器对话框编写verilog程序如下:

module exp2(R,Resetn,Clk,Load,En,up_down,Count,Q);

/*

* 说明:

* R 输入向量 提供并行数据

* Resetn 复位输入

* Clock 时钟信号

* Load Load==0(计数模式) Load==1(加载模式)

* En 使能输入端

* up_down 用于识别计数器执行加/减运算

* Q 输出向量

* Count 进位/借位信号

*/

input [3:0]R;

input Resetn,Clk,Load,En,up_down;

output reg [3:0]Q;

output reg Count;

reg Clock_1hz; //1Hz分频新信号

reg [26:0]Counter; //计数器用于分频时计数

//实现50MHz到1Hz分频操作,产生频率为1Hz的时钟信号

always @(posedge Clk)

begin

if(Counter == 'd25000000)

begin

Clock_1hz <= ~Clock_1hz;

Counter <= 0;

end

else

Counter <= Counter + 1;

end

//主程序部分,实现键控加法减法计数、并行载入数据、进位/借位输出

always @(negedge Resetn,posedge Clock_1hz)

begin

if(Resetn == 0)

begin

Q <= 0;

Count<=0;

end

else if(Load)

Q <= R;

else if(En)

begin

Q <= Q + (up_down ? 1 : -1);

if(up_down)

Count = (Q[3]&Q[2]&Q[1]&Q[0]);

else

Count = (!(Q[3]|Q[2]|Q[1]|Q[0]));

end

end

endmodule3.对编写的verilog程序进行编译并仿真,对程序的错误进行修改。

波形图如下:

4.编译仿真无误后,依照拨动开关、LED与FPGA的管脚连接表或参照实验箱用户手册进行管脚分配,分配完成后,再进行全编译一次,以使管脚分配生效,管脚分配图如下:

实验结果:

不拨动开关,即K7 K6 K5 K4表示D3 D2 D1 D0为0000;

拨动开关K4,即K7 K6 K5 K4表示D3 D2 D1 D0为0001;

拨动开关K5,即K7 K6 K5 K4表示D3 D2 D1 D0为0010;

拨动开关K5K4,即K7 K6 K5 K4表示D3 D2 D1 D0为0011;

拨动开关K6,即K7 K6 K5 K4表示D3 D2 D1 D0为0100;

拨动开关K6K4,即K7 K6 K5 K4表示D3 D2 D1 D0为0101;

拨动开关K6K5,即K7 K6 K5 K4表示D3 D2 D1 D0为0110;

拨动开关K6K5K4,即K7 K6 K5 K4表示D3 D2 D1 D0为0111;

拨动开关K7,即K7 K6 K5 K4表示D3 D2 D1 D0为1000;

拨动开关K1,使得CLK信号为1,计数器开始工作,前四个LED灯通过8421码计数0000,0001,0010,0011,0100,0101,0110,0111,1000并通过显示屏显示出数字,可以通过开关K2设置递增计数与递减计数,通过LOAD端表示存入一个数并从此数开始计数,通过Reset端进行复位清零,达到所需功能。

四、实验总结文章来源:https://www.toymoban.com/news/detail-781806.html

本实验最重要的是设计到复位清零端进行复位清零,对于递增计数与递减计数的设置需要清除verilog代码编写上的问题,设置Load端控制存入所需数字时高位低位互相对应,否则会产生一些不必要的问题,造成一些麻烦,在进行管脚分配的时候也要一一对应。文章来源地址https://www.toymoban.com/news/detail-781806.html

到了这里,关于【verilog】含异步清零和同步使能的加/减法计数器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!