一、QUARTUS II的简单上手及基本操作

找了好多好多,感觉网上都不太人性化,所以自己记录了一下自己写的,还是有点意思的的,但是这前面的没啥意思,到后面连起来用的时候就有意思了!

1、项目的创建

1、File -> New Project Wizard

后面没有选择, 一路无脑下来,项目就已经安装好了!

2、两种方法实现38译码器

一、纯原理图法

1.1新建一个图形设计文件

1.2 放置元器件

只要在如下区域双击,就可以开始放置元器件了!

基本上用得了的就是如下栏

基本上用得了的就是如下栏

1.3 主要使用到的元器件的种类

- NOT(可以直接用搜索框搜,没必要傻傻的找)

- AND

1.4 按图连线

1.5 编译

显示这个就算成功了,然后可以先看下效果,就是仿真一下,看看是不是自己想要的结果

1.6 仿真

1.6.1 新建一个VWF文件

1.6.2 设置仿真文件

1.6.3 在in 端口设置输入波形信号

可以直接框选几栏,然后再工具栏设置高低电平

也可以框选几栏,然后双击,就可以设置这里的值

小tips: 可以将这里的进制位改为十进制,因为可以看起来很方便(主要是懒得换算,输入一位就可以达到二进制四位的效果。)

设置成这样就可以了,表示1.2.3…

1.6.4 开始仿真

会弹出一个新页面,显示出仿真波形。仿真就这样结束了,说明符合我们的预期

1.7 设置引脚,准备下载!

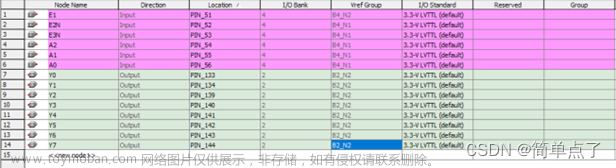

Assignments->Pin Planner

在这里输入对应的引脚号就行,然后直接退出

Tools->Programmer,下面对着书搞就行。(开发板不在身边,下不了程序)

总结一下

-

创建项目

-

创建图形设计文件

-

选择元器件

-

画图

-

编译

-

仿真

-

选择引脚

-

下载

二、纯VHDL

相同步骤省略,只关注VHDL

2.1创建vhd文件

g)]

小tips:看个人喜好,我喜欢用Notepad来代替quartus ii的编译

2.2 导入常用库

类似与c语言的Include 和python 中的import(一般无脑导入就行)

Library IEEE;

Use IEEE.STD_LOGIC_1164.all;

2.3 编写实体

实体,就是主要就是定义要使用的端口,注意,实体名称一定要和vhdl文件名称一样,否则报错

Entity sch38yimaqi_vhdl IS

Port(input1:IN std_logic_vector (2 DOWNTO 0);

D:OUT std_logic_vector (7 DOWNTO 0));

End;

2.4 编写结构体

结构体的感觉更像是其他语言里面函数之类的感觉,就是去实现功能,这里一个并行就可以完成

ARCHITECTURE behave OF sch38yimaqi_vhdl IS

BEGIN

PROCESS(input1) --进程程序,程序顺序执行

BEGIN

CASE input1 IS

WHEN "000" => D<="11111110"; -- 八位,当输入为000时,只有最后一位置0

WHEN "001" => D<="11111101";

WHEN "010" => D<="11111011";

WHEN "011" => D<="11110111";

WHEN "100" => D<="11101111";

WHEN "101" => D<="11011111";

WHEN "110" => D<="10111111";

WHEN "111" => D<="01111111";

WHEN OTHERS => D<="11111111";

END CASE;

END PROCESS;

END;

没有在学校的fpga的板子上试验过,如果运行不成功的话,应该只要修改一下逻辑值就够了,就是0 1 那些。

3、拓展题

1、 LED9-LED12全部灭掉,无非就是让led的那些端口全部置0(假如设置1 为亮的话),可以在定义端口的时候,直接给他们赋初值的时候就直接解决掉他们。

D4:OUT std_logic_vector (3 DOWNTO 0):="0000"); -- 初始化D9-D12 置低点位,不亮。

2、添加使能端的问题,同样也是一样的,只要添加一个if的判断语句就可以解决

ARCHITECTURE behave OF sch38yimaqi_more IS

BEGIN

PROCESS(input1) --进程程序,程序顺序执行

BEGIN

IF EN='1' THEN -- 当使能为1时,进行有效译码

CASE input1 IS

WHEN "111" => D<="00000001"; -- 八位,当输入为000时,只有最后一位置0 实验led亮为1 按键摁下为0

WHEN "110" => D<="00000010";

WHEN "101" => D<="00000100";

WHEN "100" => D<="00001000";

WHEN "011" => D<="00010000";

WHEN "010" => D<="00100000";

WHEN "001" => D<="01000000";

WHEN "000" => D<="10000000";

WHEN OTHERS => D<="00000000";

END CASE;

ELSIF EN='0' THEN -- 不需要译码时,使能端置0,全部输出低电平

D<="00000000";

END IF;

END PROCESS;

END;

3、流水灯的实现具体可以参考另外一篇,这里主要是有两种思路

第一种,就是用rol函数(就是沿着向量右移一位)

可以参考这个

PROCESS(tim) -- 含有多个进程语句,都为并行执行

BEGIN

IF(tim'event and tim = '1') THEN

sta <= sta rol 1;

END IF;

END PROCESS;

第二种是,直接连接向量的头,也可以达到移位的效果文章来源:https://www.toymoban.com/news/detail-782143.html

BEGIN

IF(tim'event and tim = '1') THEN

sta <= sta(6 DOWNTO 0) & sta(7);

END IF;

END PROCESS;

4、字太多了,不想看

完全代码如下文章来源地址https://www.toymoban.com/news/detail-782143.html

Library IEEE;

Use IEEE.STD_LOGIC_1164.all;

Entity sch38yimaqi_more IS

Port(input1:IN std_logic_vector (2 DOWNTO 0);

EN:IN std_logic;

D:OUT std_logic_vector (7 DOWNTO 0);

D4:OUT std_logic_vector (3 DOWNTO 0):="0000"); -- 初始化D9-D12 置低点位,不亮。

End;

ARCHITECTURE behave OF sch38yimaqi_more IS

BEGIN

PROCESS(input1) --进程程序,程序顺序执行

BEGIN

IF EN='1' THEN -- 当使能为1时,进行有效译码

CASE input1 IS

WHEN "111" => D<="00000001"; -- 八位,当输入为000时,只有最后一位置0 实验led亮为1 按键摁下为0

WHEN "110" => D<="00000010";

WHEN "101" => D<="00000100";

WHEN "100" => D<="00001000";

WHEN "011" => D<="00010000";

WHEN "010" => D<="00100000";

WHEN "001" => D<="01000000";

WHEN "000" => D<="10000000";

WHEN OTHERS => D<="00000000";

END CASE;

ELSIF EN='0' THEN -- 不需要译码时,使能端置0,全部输出低电平

D<="00000000";

END IF;

END PROCESS;

END;

到了这里,关于实验一:38译码器的VHDL实现及原理图实现的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!