Gvim写RTL code,VCS仿真,Verdi看波形,DC做综合下约束,Primetime做STA,Spyglass做异步时序分析。

VCS全称Verilog Computer Simulation ,VCS是逻辑仿真EDA工具的编译源代码的命令。要用VCS做编译仿真,首先得有一个RTL代码,比如我们写了一个全加器和全加器的testbench,总共两个.v文件 。

有了RTL文件后,如何调用VCS进行编译呢? 在.v文件所在的目录下打开terminal,键入:

vcs -sverilog -debug_all full_adder.v full_adder_tb.v -l com.log

上面有很多细节,一个一个讲:

-sverilog:编译命令选项,识别SystemVerilog语法,如果代码中有SV语法,则编译的时候必须加这个选项。

-debug_all:编译命令选项,可以将debug的信息全部保存下来,比如波形文件。

-l com.log:编译命令选项,将编译过程生成的日志写入com.log文件。

执行完上面这条代码后,如果编译没有报错,一切正确,那么在当前文件夹就会生成一个simv文件,这个文件就是仿真文件,我们跑仿真就用这个文件,注意是simv不是sim。

当然除了写命令调用VCS,也可以用命令:dve & ,启动逻辑仿真工具VCS自带的一个图形化界面dve。命令中的& 表示后台运行dve命令,不占用当前的 terminal。

图形化界面如果想要跑仿真,点击simulate的setup选项,然后选中编译过后的仿真文件simv文件,就可以进行跑仿真了。

把需要看波形的信号点击,Add to wave,然后就会打开一个波形窗口。

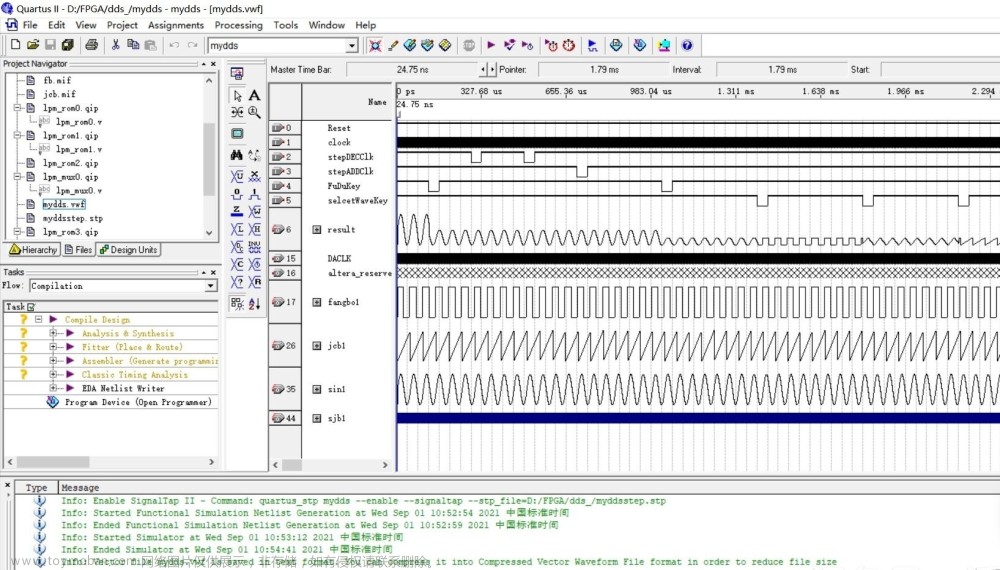

生成的波形窗口如下,在底层的输入命名行输入:run,就会开始跑仿真了。

输入run之后,开始仿真就可以看波形了。

按f键,显示所有波形,下面的log窗口就是显示仿真的日志。

上面讲的操作是用界面化的DVE窗口去操作的,实际上我们都使用脚本命令的方法去操作,写命令行编译、写命令行仿真、写命令行看波形。

看波形命令为:dve -vpd vcdplus.vpd & ,想要看波形,我们需要在tb文件里面输出波形文件才行,在tb中展示为:

initial begin

$vcdpluson;

end

输出波形文件后就可以用脚本命令调用dve看波形了。

综上,我们用VCS进行编译、仿真、看波形的脚本命令分别为:

编译源代码:vcs -sverilog -debug_all full_adder.v full_adder_tb.v -l com.log

跑仿真:./simv -l sim.log

看波形:dve -vpd vcdplus.vpd &

但事实上,如果每次编译仿真看波形,都要用手去打这些字符的话,会很累,能不能用什么脚本命令,让我们能够键入很少的字符,就可以进行编译仿真看波形,甚至一条龙服务呢?有,Makefile。

我们用Gvim新建一个文本文件,命名为Makefile,然后如图所示写命令,写命令的方式就是,写一个随便什么关键字,然后+冒号+回车,再键入你设置关键字绑定的脚本命令。比如我们上面写的com,是用来编译的用户自定义关键字,下一行就紧跟着我们定义关键字所代表的代码。注意一个细节,怎么判断我们写的脚本是否被自定义挂件字链接了呢?看颜色,如果没有连接上的话,颜色是普通的黑色,如下图:

这就代表没链接上,通常是由于缩进问题导致的,这点需要注意。

还有一个细节,细心的人会发现,我们编译的时候,没有把文件的名字写到com脚本连接的命令里,而是写 -f rtl.list。这是什么意思呢,这里的rtl.list用来存放我们rtl 代码的名字,用这种方式更方便,后续修改rtl代码名称也好,增减也好都好修改,我们只需要把所有rtl代码的名字都存放到rtl.list中,生成rtl.list的命令也很简单,只要检索当前目录下所有以.v结尾的文件的文件名,然后存入rtl.list就行了,linux命令:find -name "*.v" > rtl.list

对于某个信号,还有一些好用的快捷键可以实用比如圈出来的三个按键

它们分别是:Trace Drivers (Ctrl + D)追踪它的驱动、Trace Value Change ( Ctrl + Shift + D) 追踪代码中数值改变的位置、Trace Loads (Ctrl + Loads)追踪它的负载。

选择要追踪的边沿或者数值,可以直接追踪。

在上面已经提到过Makefile 脚本的书写格式,就是写一个关键字加冒号,然后回车输入一行命令,输入完后,以后要运行这行命令就不用全部打全了,只需要在terminal界面,输入make 关键字就行了。

比如,我们已经在当前文件夹下写好了上面所示的Makefile脚本文件,然后我们也写好了rtl代码,并在terminal 中输入:find -name "*.v" >rtl.list,把.v文件的相对路径都放到了rtl.list中。这时候如果要编译,我们只需要在terminal界面输入:make com 回车

系统会自动帮我们打出com关键字所链接的命令行,如图所示:

Makefile 脚本命令解释:

Makefile 脚本命令解释:

vcs表示调用vcs软件,-sverilog 表示编译所用的规范,如果我们写的代码里有systemverilog就一定要有这个选项,-debug_all 完全调试模式, -timescale = 1ns/1ps 这个在编译的时候就写,那么在tb里面就不用写了,表示最小仿真时间是1ns,最小仿真精度是1ps。-f rtl.list意思是吧rtl.list里的所有文件都编译进去, -l com.log 意思是把编译产生的编译文件保存在com.log文件中。

./simv 表示运行当前文件夹下的simv文件,这个文件在com命令过后会生成,也就是编译结束后会生成。-l sim.log,意思是把仿真产生的仿真信息都存储在sim.log文本文件中。

把以后缀“.vpd”、“.log”、“.key”、“.vdb”的文件删掉,把csrc文件删掉,把sim开头的文件删掉,把DVEfiles文件删掉。删掉运行verdi软件产生的一些附属文件。文章来源:https://www.toymoban.com/news/detail-783723.html

这里写的是设计的一些VCS操作,实际上如果是做验证的话,还会有更多的一些操作,比如收覆盖率,仿真给随机种子等。文章来源地址https://www.toymoban.com/news/detail-783723.html

到了这里,关于逻辑仿真工具VCS的使用-Makefile的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!