- bit [15:0]记录interrupt的原因;

- bit[max:16]时user自定义的,默认不使用;

一个中断,trap to M-mode的条件如下:

- 当前是M-mode, mstatus.MIE==1,或者当前的权限等级低于M-mode, 此时不管当前的xIE是否为1,M-mode的中断总是有效的;

- 满足上面的条件后,还需要mip/mie对应bit的值都设置为1;

- 如果有中断委托寄存器,对应bit不能被委托;

M-mode的中断优先级是最高的;

在实际实现的时候,mip中的bit可以设置为writable,或者read-only;

- 如果是可写的,那么往这个bit写0,可以清除对应pending的中断;

- 如果是read-only的,那么必须提供其他的方式来清除这个bit;

在实际实现时,如果中断可pending的话,mie对应bit都要设置成writable的;

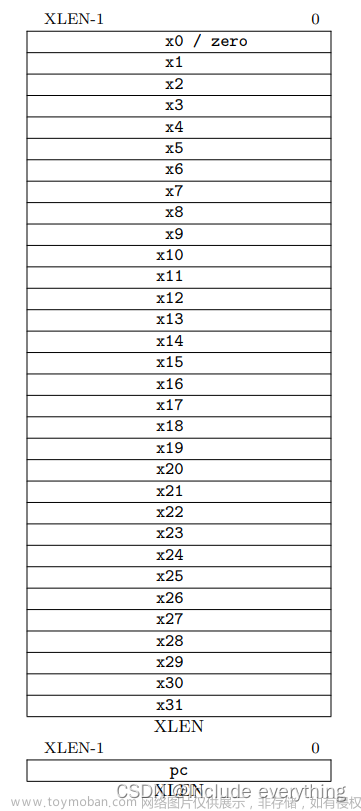

CSR中每个bit的描述如下:

- mip.MEIP & mie.MEIE分别对应machine-level external interrupts的pending&enable bits;

- MEIP必须是RO的,需要通过interrupt controller来set和clear;

- mip.MTIP & mie.MTIE分别对应machine-level timmer interrupts的pending&enable bits;

- MTIP必须是RO的,通过往mtimecmp寄存器写入对应的值来清除;

- mtimecmp寄存器的写入方式请参考:(后续补充)

- mip.MSIP & mie.MSIE分别对应machine-level software interrupts的pending&enable bits;

- MSIP必须是RO的,通过访问memory-mapped control registers来写入数据,这个中断一般是harts间用来通信的,machine_level的处理器中断;

- 每个hart也可以通过往control register中访问,写入自己的MSIP;

- 如果系统中只有一个hart, 或者platform中通过external interrupts(MEI)来代替,那么MSIP/MSIE都是read-only zero的;

如果s-mode没有实现,那么SEIP/STIP/SSIP/SEIE/STIE/SSIE都是read-only zero的;

如果实现了,那么supervisor modei相关的bit描述如下:

- mip.SEIP & mie.SEIE分别对应supervisor-level external interrupts的pending&enable bits;

- SEIP是writable的,可以被M-mode的软件写入,用来指示S-mode有一个ext int pending;

- 除此以外,该bit也可能会被platform-level interrupt controllr产生;

- 所以SEIP是上述两种来源的逻辑或操作生成的;

- 当用CSR指令来读mip时,SEIP的值,是上面两种来源的逻辑或,但是如果针对CSRRS/CSRRC这类,先读出来,再写入的指令,来自中断控制器的值,并不参与运算;只有软件写入的SEIP,参与CSRRS/CSRRC指令的计算;

- mip.STIP & mie.STIE分别对应supervisor-level timmer interrupts的pending&enable bits;

- STIP可写,M-mode的软件,可以将timer的interrupts, 委托到S-mode;

- mip.SSIP & mie.SSIE分别对应supervisor-level software interrupts的pending&enable bits;

- SSIP writable, 可以通过软件写入,也可以通过platform-specific interrupt controller置位;

上述的这些中断优先级如下:MEI, MSI, MTI, SEI, SSI, STI文章来源:https://www.toymoban.com/news/detail-784075.html

如果interrupt通过mideleg寄存器,委托到S-mode, SIP/SIE寄存器才是可见的,否则,对应bit都是read-only zero的;文章来源地址https://www.toymoban.com/news/detail-784075.html

到了这里,关于Machine Interrupt Registers的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!