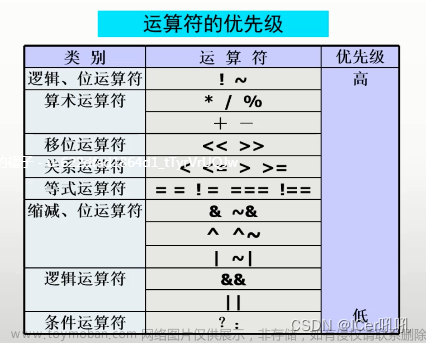

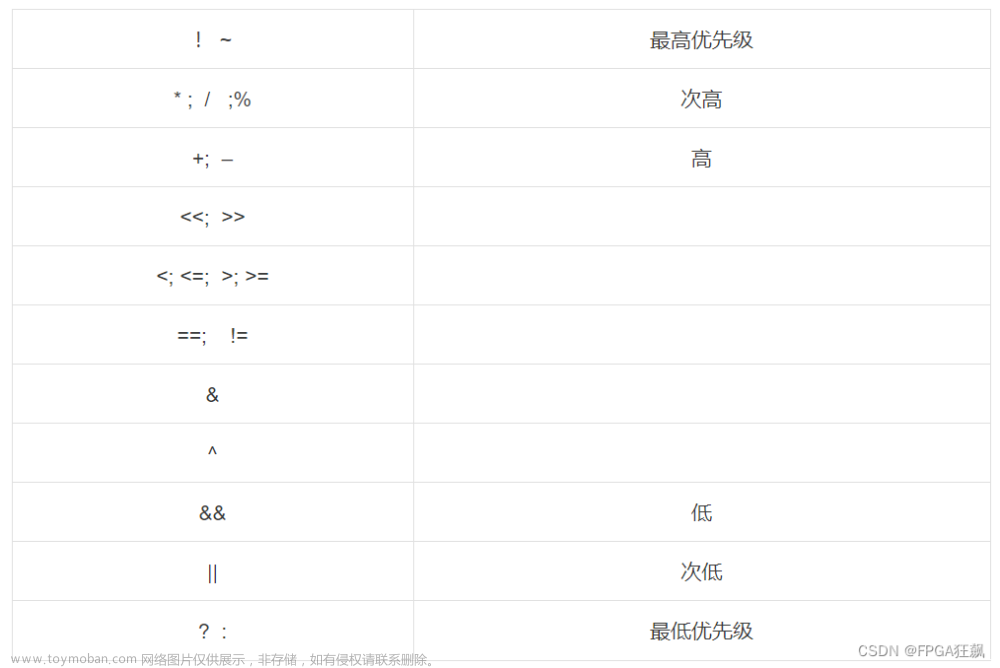

今天看书上的Verilog代码中,出现了运算符

~^,从来没见过,搜了一些资料,记录一下。assign slt_result[0] = (alu_src1[31] & ~alu_src2[31]) | ((alu_src1[31] ~^ alu_src2[31]) & adder_result[31]);

结论

~^、^~作为二元运算符时,是同或;~^、^~作为一元运算符时,是缩减异或的取反(感谢@smile、陌离老哥在评论区指正);

~&只能作为一元运算符,是对缩减&结果的取反;

~|只能作为一元运算符,是对缩减|结果的取反;

对缩减异或取反不等于缩减同或!例如

5'b11011:

( ( ( ( 1 ⊕ 1 ) ⊕ 0 ) ⊕ 1 ) ⊕ 1 ) = ( ( ( 0 ⊕ 0 ) ⊕ 1 ) ⊕ 1 ) = ( ( 0 ⊕ 1 ) ⊕ 1 ) = ( 1 ⊕ 1 ) = 0 ( ( ( ( 1 ⊙ 1 ) ⊙ 0 ) ⊙ 1 ) ⊙ 1 ) = ( ( ( 1 ⊙ 0 ) ⊙ 1 ) ⊙ 1 ) = ( ( 0 ⊙ 1 ) ⊙ 1 ) = ( 0 ⊙ 1 ) = 0 ∴ ¬ ( 1 ⊕ 1 ⊕ 0 ⊕ 1 ⊕ 1 ) ≠ ( 1 ⊙ 1 ⊙ 0 ⊙ 1 ⊙ 1 ) ((((1\oplus 1)\oplus 0)\oplus 1)\oplus 1)=(((0\oplus 0)\oplus 1)\oplus 1)=((0\oplus 1)\oplus 1)=(1\oplus 1)=0 \\ ((((1\odot 1)\odot 0)\odot 1)\odot 1)=(((1\odot 0)\odot 1)\odot 1)=((0\odot 1)\odot 1)=(0\odot 1)=0 \\ \therefore \lnot (1\oplus 1\oplus 0\oplus 1\oplus 1) \neq (1\odot 1\odot 0\odot 1\odot 1) ((((1⊕1)⊕0)⊕1)⊕1)=(((0⊕0)⊕1)⊕1)=((0⊕1)⊕1)=(1⊕1)=0((((1⊙1)⊙0)⊙1)⊙1)=(((1⊙0)⊙1)⊙1)=((0⊙1)⊙1)=(0⊙1)=0∴¬(1⊕1⊕0⊕1⊕1)=(1⊙1⊙0⊙1⊙1)

有没有

&~和|~呢?

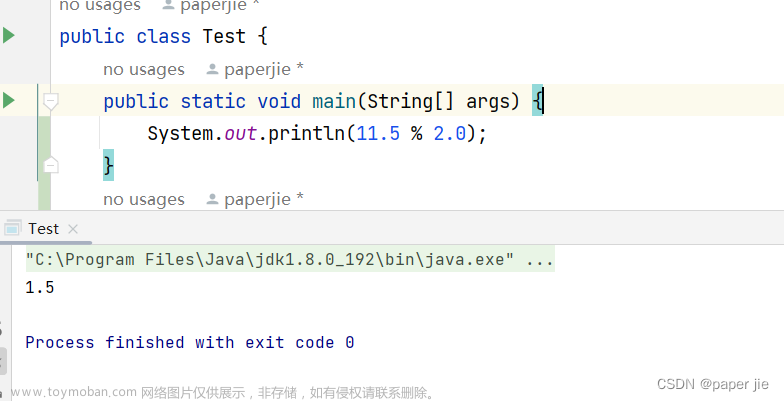

譬如a[2:0] &~ b[2:0],这里便不能将&~整体看做一个单独的运算符了,~作为一元操作,优先级最高,先将b[2:0]做按位取反,再通过&和a[2:0]做位与,|~类似。

再补充HDLBits的一些说明(https://hdlbits.01xz.net/wiki/Reduction):

The reduction operators can do AND, OR, and XOR of the bits of a vector, producing one bit of output:& a[3:0] // AND: a[3]&a[2]&a[1]&a[0]. Equivalent to (a[3:0] == 4'hf) | b[3:0] // OR: b[3]|b[2]|b[1]|b[0]. Equivalent to (b[3:0] != 4'h0) ^ c[2:0] // XOR: c[2]^c[1]^c[0]These are unary operators that have only one operand (similar to the NOT operators

!and~).

You can also invert the outputs of these to create NAND, NOR, and XNOR gates, e.g., (~& d[7:0]).

测试过程

~^、^~作为二元运算符时

reg [1:0] x;

initial

begin

x <= 2'b00 ~^ 2'b00;

#5 x <= 2'b01 ~^ 2'b00;

#5 x <= 2'b10 ~^ 2'b00;

#5 x <= 2'b11 ~^ 2'b00;

#5 $finish;

end

结果如下图所示(^~结果亦如下),为同或

~^、^~作为一元运算符时

reg x;

initial

begin

x <= ~^ 2'b00;

#5 x <= ~^ 2'b01;

#5 x <= ~^ 2'b10;

#5 x <= ~^ 2'b00;

#5 $finish;

end

结果如下图所示(^~结果亦如下),为缩减异或的取反。

~&作为一元运算符时

reg [1:0] x;

initial

begin

x <= ~& 2'b00;

#5 x <= ~& 2'b01;

#5 x <= ~& 2'b10;

#5 x <= ~& 2'b11;

#5 $finish;

end

结果如下图所示,为缩减&取反的结果。

~|作为一元运算符时

reg [1:0] x;

initial

begin

x <= ~| 2'b00;

#5 x <= ~| 2'b01;

#5 x <= ~| 2'b10;

#5 x <= ~| 2'b11;

#5 $finish;

end

结果如下图所示,为缩减|取反的结果。 文章来源:https://www.toymoban.com/news/detail-784188.html

文章来源:https://www.toymoban.com/news/detail-784188.html

吐槽

好想过年前写完龙芯杯初赛,然后PASS掉啊啊啊啊!!!

已经写完的啦,不过是年后写完的 : )文章来源地址https://www.toymoban.com/news/detail-784188.html

到了这里,关于Verilog中的^~、~^、~&、~|运算符的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!