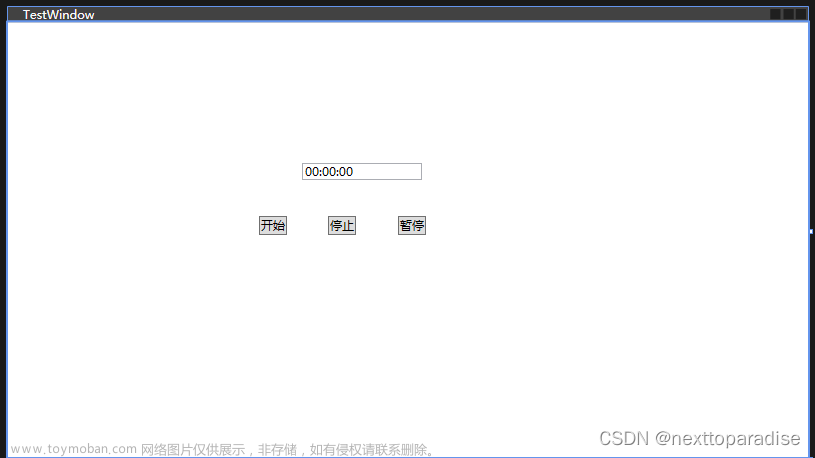

Verilog秒表计时器设计

设计一个基于Verilog的秒表计时器,该计时器可以在嵌入式系统中使用。下面是详细的设计说明和相应的源代码。

设计说明:

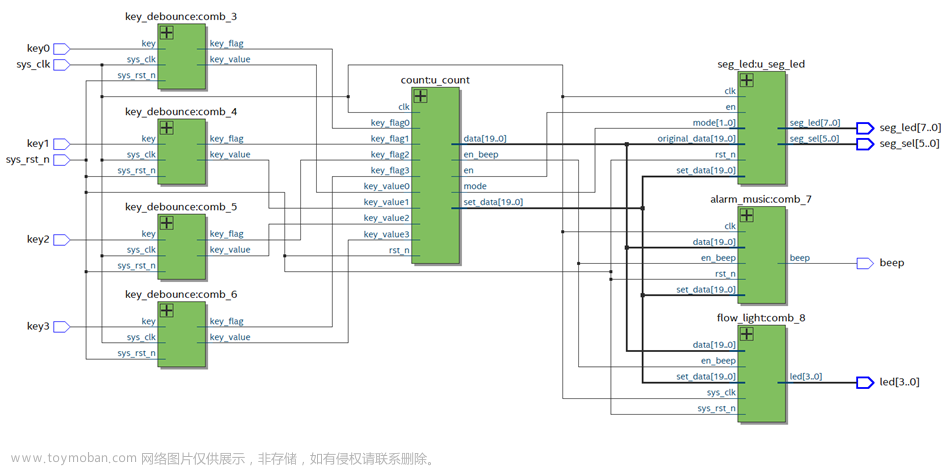

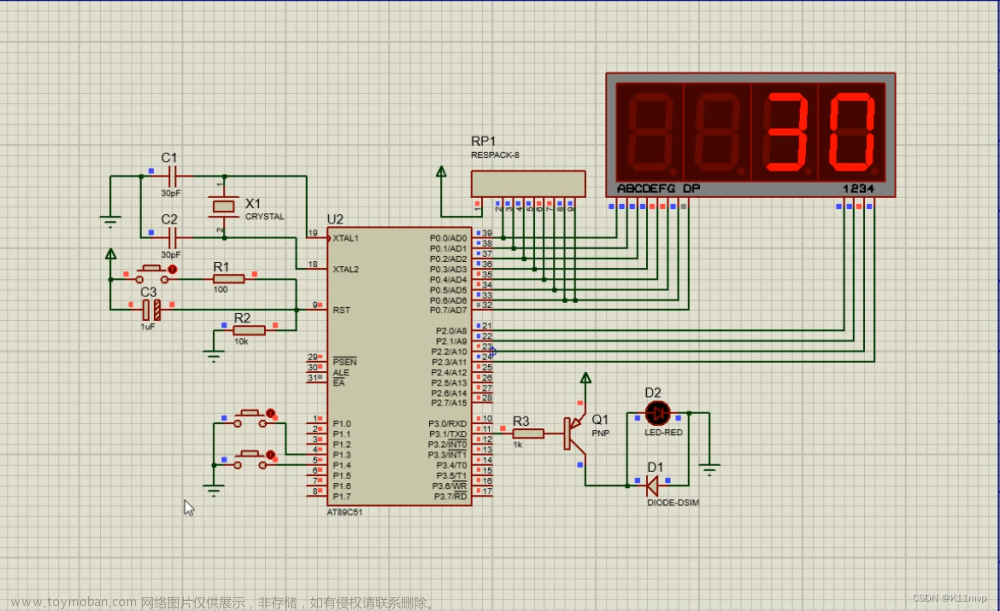

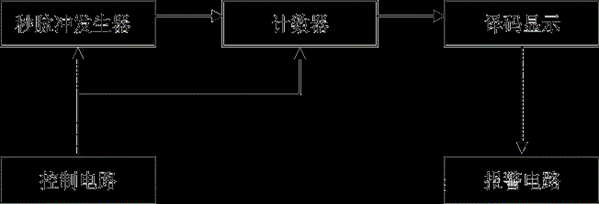

秒表计时器是一种常见的计时工具,可以用于测量时间间隔。在嵌入式系统中,我们可以使用Verilog语言来实现一个简单的秒表计时器。该计时器将使用FPGA或ASIC等硬件设备来实现。以下是秒表计时器的设计要点:

-

输入信号:

- start:开始计时的触发信号

- stop:停止计时的触发信号

- reset:重置计时器的触发信号

-

输出信号:

- seconds:计时器的输出,以秒为单位

-

内部信号:

- clk:时钟信号,用于驱动计时器

- count:计数器,用于保存经过的时钟周期数

-

设计思路:文章来源:https://www.toymoban.com/news/detail-784885.html

- 在计时开始时,计数器开始递增,直到计时停止或重置。

- 计时停止时,计数器的值将被保存为输出信号。

- 在计时重置时,计数器将被清零。

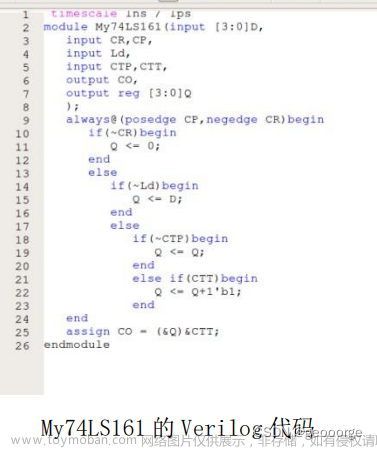

源代码:文章来源地址https://www.toymoban.com/news/detail-784885.html

module Stopwatch(

input wire start,

input wire stop,

input wire reset,

output wire [31:0] seconds

);

reg [31:0] count;

reg clk;

always @(posedge clk) begi到了这里,关于Verilog秒表计时器设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!