jesd204b实战操作笔记

本篇的内容是基于博主设计的jesd204b接口的ADC和FPGA的硬件板卡,通过调用jesd204b ip核来一步步在FPGA内部实现高速ADC数据采集,jesd204b协议和xilinx 的jesd204 IP核相关基本知识已在前面多篇文章中详细介绍,这里不再叙述~

在该篇中,博主试图从一个初学者的视角来记录整个开发流程,力求做到每一个读者阅读完该笔记后都能快速开发基于jesd204b接口的FPGA-ADC数据采集,同时也确保几个月甚至几年后的博主本人已经遗忘了jesd204b开发细节后,通过阅读该笔记能够快速重新上手。

还是老话说得好:好记性不如烂笔头!

硬件工作环境

ADC:ADS52J90。FPGA:kintex7。供电:12V/4A 直流电源。该板卡最多外接32通道2Vpp模拟信号以及20路外部触发信号。数据传输接口方式有千兆以太网接口、高速光纤接口以及低速USB串口。需要用到的工具为万用表、示波器、信号发生器。

逻辑开发环境

Vivado2017.4和jesd204b ip核licence。

好了,接下里的正式进入开发主题:

开发目的:

博主一直致力于开发通用高速、多通道电子学数据采集系统。在ADC芯片的选型过程中发现,TI的ADC芯片-ADS52J90很适合博主的需求:该芯片在9mm x 15mm的面积上可以实现最高32通道/100MHz/14bit的连续波形采样,并且其输出数据的方式除了传统的clock-data-frame(CDF)接口外,还引入了最新的jesd204b接口。

如果博主采用传统的CDF方式,那意味着PCB布线量特别大、FPGA管脚占用非常多、硬件尺寸必然无法太小,因此就选择了结构非常简单的jesd204接口,随之而来的就是大量的研发工作。。。。。。,还好,最后一切顺利~

ADC参数初探

拿到一款jesd204 接口的ADC后,我们首先要看一下它的jesd204链路参数。以本篇的ADS52J90芯片为例,如图2所示:

该款芯片内置了16个ADC(模数变换器),这16个ADC输出的数据通过jesd接口输出。

这16个adc的数据通过2、4、或者8条lane输出,具体选哪种用户是可以选择的。

每条lane的最高线速率是5Gbps。

支持子类0、1和2。

该芯片的采样率、采样精度,采样通道数都有多种模式,用户可选择范围比较大,但必须最终满足每条lane的数据线速率不能高于5Gbps。

我们再来看看ADC数据的传输层数据结构。该ADC手册描述输出数据有“NORMAL PACKING MODE”和“ SINGLE CONVERTER PER OCTET MODE”两种模式,为了提高位传输效率,博主选择了“NORMAL PACKING MODE”,如图3所示:

在实际操作演示时,博主通过ADC配置接口,选择了固定的ADC基本采样参数:即ADC的采样率为80MSPS、采样精度为12bit、采样通道为16,所有数据最终通过4条lane输出到FPGA(4个lane正好对应FPGA的一个GTX quad,比较整齐。。。。技术男强迫症犯了)。因此,在“NORMAL PACKING MODE”模式下,N=12,N’=12,F=6。

具体的传输层数据结构如图4所示:

从图4也可以看出,F=6,采样数据没有control bit 和tail bit填充,这样就保证了输出数据100%有效传输效率。

那么ADC的帧时钟是多少呢?手册上也已经给出了,如图5所示:帧时钟频率和ADC转换频率一样的,这里都为80MHz。

基于以上信息,博主选择的工作模式的lane线速率就可以确定了:

帧时钟×帧字节数×每字节的bit数×8b/10b编码开销即为lane的工作线速率

80MHz×6×8×10/8=4.8Gbps

另外,还有一种更容易理解的线速率确定方式:

我们知道每条lane传输4个ADC的数据,而ADC采样率为80MHz,采样精度12bit,没有控制和tail bit,只要8b/10b编码,因此每条lane的线速率为:

80MHz采样率×12bit采样精度×4个ADC×10/8=4.8Gbps

另外,还有最后一个多帧参数K 需要确认。ADC数据手册给出了K的范围,即:Ceil (17 / Number of Octetsper Frame) ≤ Multiframe Size (In Terms of Number of Frames),即Ceil (17 / 6) ≤ K。因此K必须要大于等于3,小青菜哥哥决定K取4。

到现在为止jesd204的参数就确认完毕了,在这里就不一一介绍该芯片的其它功能了,该芯片的详细中文版介绍可以看博主以前的文章。

接下来我们来打开vivado,一步一步来完成FPGA-ADC数据采集的工程。在工程建立的过程中,博主还会反复提到上述的ADC芯片,因为在建立jesd204链路时,FPGA端的参数必须和ADC的参数保持一致~

如图6所示为新建的vivado工程“jesd204b_ads52j90”,匹配硬件的FPGA型号“xc7k325tffg900-2”,可以看到工程内部还没有任何文件:

图6:新建工程

接下里我们来例化jesd204 IP核,如图7所示:

图7:例化IP核

双击该IP核后打开了jesd204的配置界面,配置界面分成4个子界面:“Configuration”、“Shared Logic”、“Default Link Parameters”以及“JESD204 PHYConfiguration”。我们下面将分别描述:

“Configuration”配置界面

如图8所示为“Configuration”配置界面,该界面有7个地方是需要用户来选择的

图8:“Configuration”配置界面

1:输入IP核名字

2:由于是ADC数据采集,因此FPGA的IP核应该设置成“Receive”

3:设置IP核内部的接收数据缓存器的字节长度。数据缓存器主要用来做lane之间的数据对齐和实现确定性延迟功能。字节长度是用户可选的,选得值越小越节约FPGA逻辑资源,但字节长度必须要超过FK(本篇为64=24),因此选择了64,如果大家不清楚的话,直接选最大长度,绝对没问题。

4:lane数量:本篇为4条lane。

5:jesd204 IP核的AXI4-Lite配置时钟:默认为100MHz。对于ultrascale器件,频率范围为10MHz~200MHz,对于7系列器件,如果IP核的模式为“Include Shared Logic inexample design”,则频率范围为10MHz~200MHz;如果IP核的模式为“Include Shared Logic incore”,则频率范围和Transceiver DRP时钟频率范围相同,本人选择了80MHz(80MHz为FPGA系统时钟,可以省去FPGA另外再提供100MHz时钟)。

6:该选项可以选择sysref信号被core clk的上升沿或下降沿采样,用于jesd204b子类1的确定性延迟功能。一般来说,外界提供的core clock和sysref是同源且上升沿对齐信号,因此在FPGA端最好选择在时钟下降沿采样sysref比较精确,具体描述可参考pg066的page-60。

7:用户决定IP核的core clk是否由glbclk(p/n)管脚输入。当refclk(p/n)频率不等于core clk时,必须外部输入core clk。本篇中的线速率为4.8Gbps,因此core clk为120MHz,所以本人将参考时钟输入频率也调成120MHz,这样IP核只需要一个120MHzd的参考时钟输入接口了。

“Shared Logic” 配置界面

如图9所示为“Shared Logic” 的配置界面:该界面只有两种选择,要么选择“Include Shared Logic in example design”,要么选择“IncludeShared Logic in core”。对于大部分用户来说,选择“Include Shared Logic in core”就可以了,后期使用起来很简单。对于需要使用“transceiversharing”这种高级功能的特殊用户来说,就需要选择“Include Shared Logic in example design”,以便自己可以修改IP核内部的部分代码。我们选择“IncludeShared Logic in core”就可以了。

图9:“SharedLogic” 的配置界面

“Default Link Parameters” 配置界面

如图10所示为“Default Link Parameters” 的配置界面:该界面5个部分需要用户设置:

图10:“DefaultLink Parameters” 的配置界面

1:Default SYSREFAlways:该选项用来配置LMFC计数器是否在每个SYSREF脉冲到来时都复位,或者只在SYSREF的第一个有效脉冲到来时复位,忽略以后的SYSREF信号。这里选择OFF即可。

2:Default SCR:在ADC端我们禁止了扰码功能,因此这里也将扰码功能关闭。扰码功能有利有弊,博主反正一直都不用该功能的~

3:Default F:从前面的ADC部分描述来看,这里F设置成6

4:Default K:从前面的ADC部分描述来看,这里K设置成4

5:Default SYSREFRequired on Re-Sync:该选项用来选择每次链路重新同步时是否需要sysref信号,我们最好关闭它,默认链路同步时不需要该信号,只在SYNC拉高后的下一个LMFC上升沿同步就可以了,这样就方便许多。

“JESD204 PHY Configuration” 配置界面

如图11所示为“JESD204 PHY Configuration” 的配置界面:该界面6个部分,只有其中4个部分需要用户设置:

图11:“JESD204 PHYConfiguration” 配置界面

1:Transceiver Type:这是由所选FPGA型号决定的,这里不能选择

2:Line Rate:前面已经计算过,当前需求的数据线速率为4.8Gbps

3:Reference Clock:由于线速率已确定4.8Gbps,而core clk为其1/40,即120MHz。所以为了不使用glbclk(p/n),减少一路时钟输入,这里将ReferenceClock 也设置成120MHz ,这样外部输入的glbclk(p/n)就可以由Reference Clock代替。

4:这里也没得选:只能是CPLL

5:DRP Clock Frequency:配置页面已经提到过,对于七系列器件,DRP clk和AXI4-Lite clock为同一时钟,所以这里也不可选了,只能为前面定下的80MHz。

6:不需要Transceiver的调试功能

至此,jesd204的IP核就配置完成了。例化该IP核后,其生成的ip核端口信息如下图12所示(带信号注释):

图12:IP核例化代码

再看看博主建立的工程顶层接口文件,如图13所示:(带注释),接口其实真的很简单~

图13:顶层文件接口

博主的FPGA顶层文件主要包括以下8模块,如图14所示:

图14:顶层设计

1:PLL模块

该模块利用外部40MHz晶振和FPGA内部的PLL,产生2路时钟:其中一路10MHz,作为时钟芯片配置模块和ADC配置模块的运行时钟;另一路100MHz,本打算供给AXI4-lite配置模块时钟,后来发现不需要,这里就留着备用了。

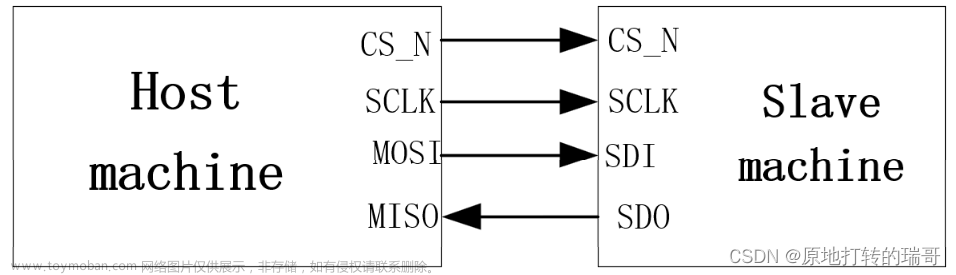

2:时钟芯片配置模块

没啥可说的,就是看lmk04826的数据手册,通过SPI接口协议配置时钟芯片内的寄存器,产生整个系统所需的时钟和sysref信号。以前的文章详细讲述过~

3:ADC配置模块

通过SPI接口协议配置ADC芯片,使其工作在我们需要的jesd204参数状态,本篇中博主将ADC配置成了累加数,便于输出测试。以前的文章详细讲述过~

4:jesd204 IP核模块

调用前面的IP核即可

5:全局时钟模块

IP核会输出一路120MHz的core clk,供给用户使用。我们将该信号引入全局时钟模块,产生120MHz和80MHz全局时钟,作为ADC数据解析模块的时钟。另外80MHz时钟还可以作为AXI4-lite的配置时钟。

6:AXI4配置模块

配置jesd204 IP核的工作参数。这里需要注意的是配置的参数和ADC配置模块的参数要相同,比如F,K,N等参数。

7:ADC数据解析模块

由于IP核输出的数据是128bit位宽,在120MHz的时钟域下工作。而ADC采样时钟是80MHz,所以ADC数据解析模块的功能就是将总共4 lane的这些数据分离,变成16个ADC的12bit精度的连续采样数据。每款ADC芯片的数据组织结构(其实就是JESD204B的传输层数据结构)不一样,所以该模块不具有普适性,只针对本篇的需求~

8:逻辑分析仪

我们通过ILA逻辑分析仪来观察每一路的ADC采样数据,看是否正确。

如下图15所示为博主的jesd204 IP核信号的连接方式,供大家参考:

图15:IP核顶层代码

我们再看看数据解析模块的接口含有哪些信号,如图16:

图:16:数据解析模块顶层

我们再看看逻辑分析仪监测的数据情况,如图17为IP核输出的数据时序,这里我们看不出来ADC数据到底对不对,得到的都是ADC采样数据经过传输层分割后的数据。

图17:jesd IP核数据输出

进一步的我们看看最终还原的ADC数据到底对不对:由于博主将ADC配置成了发送累加数,所以说如果jesd204链路正常工作了,那么观察到的16路ADC采样数据肯定也是累加数,如图18所示:可以看到数据从0累加到4095,然后循环往复,正好对应我们在前面配置的12bit ADC精度。

图18:ADC累加数据

将ADC的累加数配置更改为采集正常输入信号后,我们外接了信号发生器,将信号发生器设置成发送正弦波,下图19是在FPGA内部监测到的一路正弦信号,其他路没有接信号,是噪声基线:

图19:正弦波模拟信号的输入测试

下图20是用该板卡和上面描述的方案在试验现场测试的3种放射源的混合能谱,看上去还可以吧!

图20:实际放射源测试结果

JESD204B IP核与ADC的实际操作就到这里了,其实只要明白了jesd204协议的基本内容和IP核各个端口的含义,开发起来并不复杂。我们主要还是要仔细阅读ADC数据手册,根据手册给出的参数来确定IP核的工作参数即可。希望大家看完以后都能够有所收获~文章来源:https://www.toymoban.com/news/detail-784961.html

参考原文:FPGA动力联盟的《jesd204b实战操作笔记》文章来源地址https://www.toymoban.com/news/detail-784961.html

到了这里,关于FPGA的ADC信号采集ADS52J90-JESD204B接口的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!