名称:弹球游戏Verilog代码Quartus仿真(文末获取)

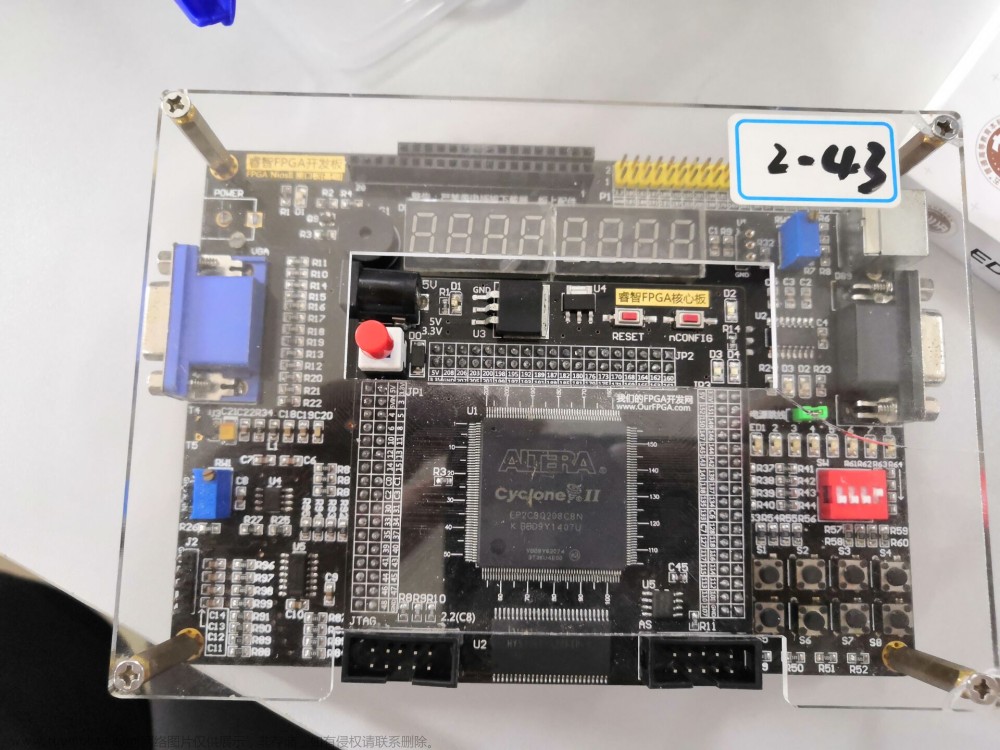

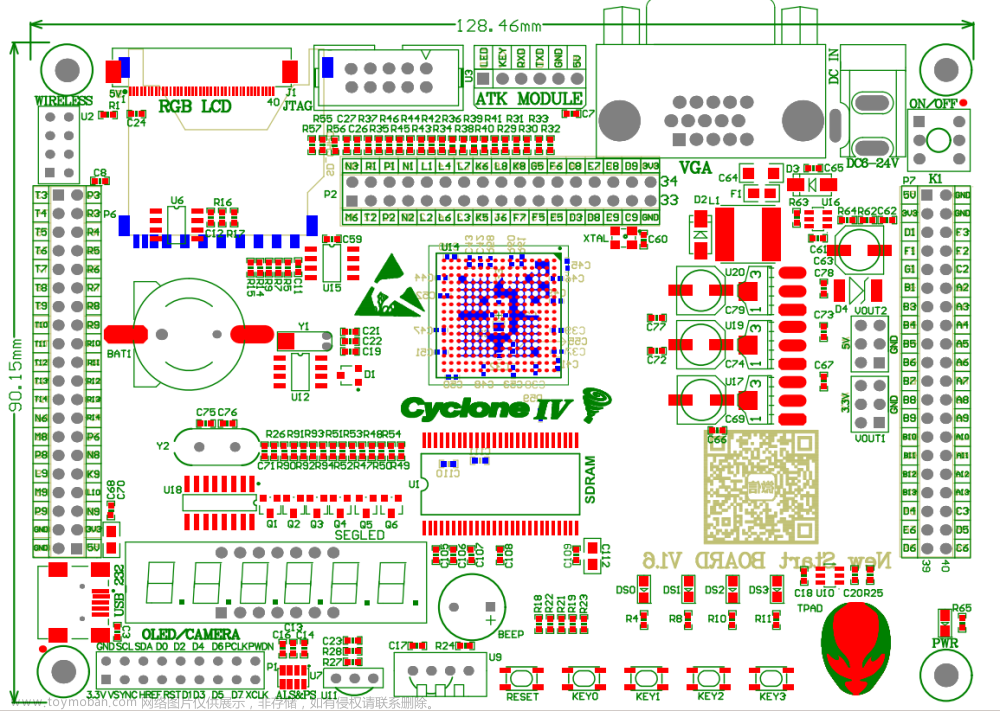

软件:Quartus

语言:Verilog

代码功能:

设计要求

查阅FPGA、VGA接口标准等相关资料文献。

2.编写HDL代码实现νGA显示模块和按键输入模块,并下载到开发板进行测试。

3.图像分辨率不低于1024*768,目标移动方块50*50,移动弹板为20*100。

4.实现一个通过VGA显示器进行游戏显示并通过按键进行控制弹板的弹球游戏。

5.对项目的性价比以及社会经济效益进行分析说明。实验要求

1.完成系统硬件设计

2.完成HDL代码设计及仿真

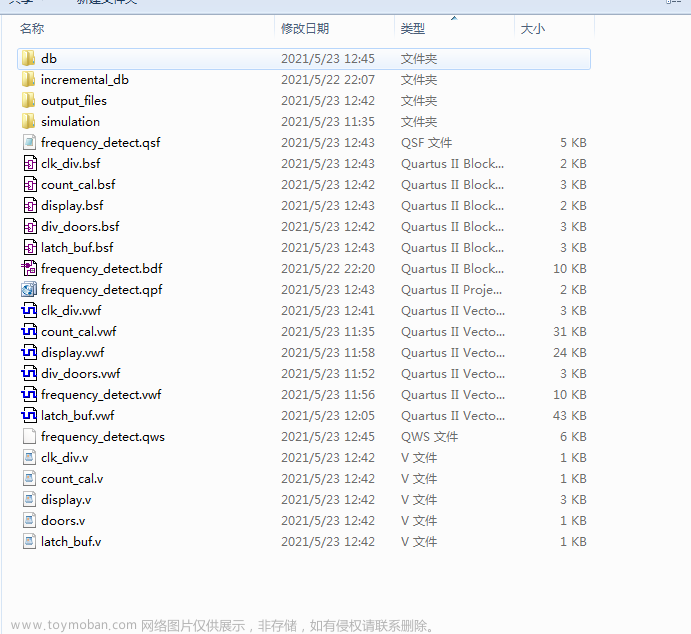

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. Testbench

6. 仿真图

整体仿真图

按键模块

VGA时序控制模块

画面生成模块

部分代码展示:文章来源:https://www.toymoban.com/news/detail-785190.html

//VGA时序控制模块 module vga_controller_1024x768(rst_p, pixel_clk, HS, VS, hcount, vcount, video_enable); input rst_p;//高电平复位 input pixel_clk;//65M output HS;//行同步 output VS;//场同步 output [10:0] hcount;//当前x像素坐标位置 output [10:0] vcount;//当前y像素坐标位置 output video_enable;//显示使能 reg HS; reg VS; //定义1024*768的参数 parameter HMAX = 1344; parameter HLINES = 1024; parameter HFP = 1024; parameter HSP = 1160; parameter VMAX = 806; parameter VLINES = 768; parameter VFP = 771; parameter VSP = 777; reg [10:0] hcounter; reg [10:0] vcounter; assign hcount = hcounter; assign vcount = vcounter; //行计数 always @(posedge pixel_clk) begin if (rst_p == 1'b1) hcounter <= 11'b0; else if (hcounter == HMAX) hcounter <= 11'b0; else hcounter <= hcounter + 1; end //场计数 always @(posedge pixel_clk) begin if (rst_p == 1'b1) vcounter <= 11'b0; else if (hcounter == HMAX) begin if (vcounter == VMAX) vcounter <= 11'b0; else vcounter <= vcounter + 1; end end //行同步 always @(posedge pixel_clk) begin if (hcounter >= HFP & hcounter < HSP) HS <= 0; else HS <= 1; end //场同步 always @(posedge pixel_clk) begin if (vcounter >= VFP & vcounter < VSP) VS <= 0; else VS <= 1; end //输出显示使能信号 assign video_enable = ((hcounter < HLINES & vcounter < VLINES)) ? 1'b1 : 1'b0; endmodule

完整代码

扫描文章末尾的公众号二维码文章来源地址https://www.toymoban.com/news/detail-785190.html

到了这里,关于弹球游戏Verilog代码Quartus仿真的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!