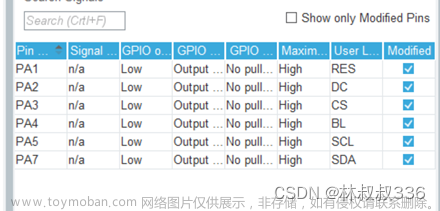

SPI硬件电路

SPI(Serial Peripheral Interface)是一种嵌入式产品常用的板级高速、全双工通信总线。

它采用1主多从的方式进行通信。

整个通信的物理层通常需要(3+N)根线。

3指的是:SCK、MOSI、MISO

N指的是片选线:片选线的数量取决于具体的从机数量及从机配置模式;

1从机时: 只需要1根片选

多从机时:如果支持菊花链模式,也仅需要1根片选;如果不支持菊花链,则每个从机都需要独立的片选。

S\S\ : Slave Select

SCK : Serial Clock

MOSI: Master Output, Slave Input

MISO: Master Input, Slave Output

空闲状态下SCK的电平由CPOL控制、总线运行时的数据采样时刻由CPHA决定,关于CPOL和CPHA的定义在SPI总线标准中的描述如下:

CPOL — SPI Clock Polarity Bit

1 = Active-low clocks selected. In idle state SCK is high.

0 = Active-high clocks selected. In idle state SCK is low.

CPHA — SPI Clock Phase Bit

1 = Sampling of data occurs at even edges (2,4,…,16) of the SCK clock

0 = Sampling of data occurs at odd edges (1,3,…,15) of the SCK clock

简介总结为:

CPOL: Clock POLarity 时钟极性

CPHA: Clock PHAse 时钟相位

CPOL: 决定总线空闲时CLK时钟的极性(0为低电平,1为高电平)

CPHA: 决定数据何时进行采样(0为在时钟的第1个跳变边沿进行采样,1位在时钟的第2个跳变边沿采样)

由此,可以定义出SPI通信时的4种传输模式:

参考原文:《SPI通信的4种传输模式》

SPI时序讲解

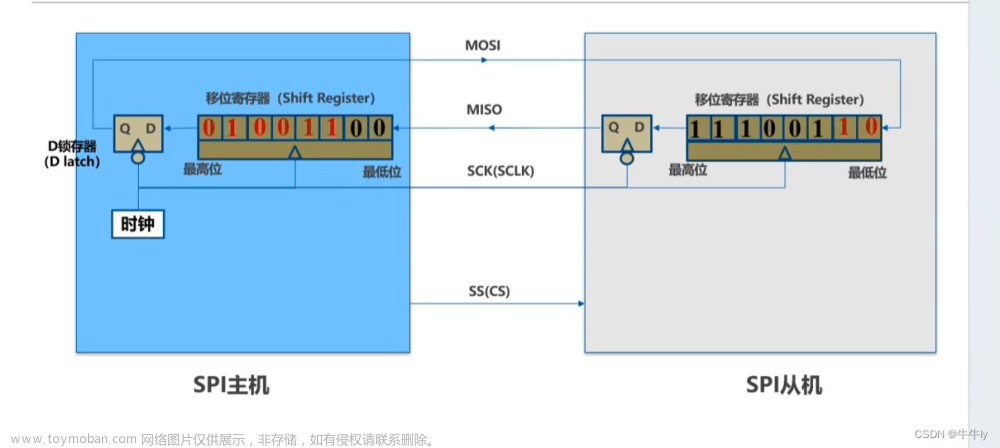

一、SPI主从通信:

SPI的基本结构相当于两个8位移位寄存器的首尾相接,构成16位的环形移位寄存器,从而实现了主机与从机的数据交换;

二、SPI通讯模式

SPI有4种不同的传输时序,取决于时钟极性CPOL和时钟相位CPHA的组合。

CPHA是用来控制数据是在第一个跳变沿还是第二个跳变沿采集的。

通过上图可以看到:

CPHA=0的时候,数据是在第一个跳变沿的时候就会被采集。

CPHA=1的时候,数据是在第二个跳变沿的时候才会被采集。

那问题来了,到底是上升沿还是下降沿采集?

这个就由CPOL来决定了:

CPOL=1的时候是上升沿采集。CPOL=0的时候是下降沿采集。

除此以外,CPOL还决定了我们时钟线SCLK空闲时的状态。

CPOL=0的时候表示SCLK在空闲时为低电平。

CPOL=1的时候表示SCLK在空闲时为高电平。

Ok,明白了这个,我们再分析4种模式的时序图。

1.模式0(CPOL=0 CPHA=0)

CPOL = 0:时钟线空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 0:数据在第1个跳变沿(上升沿)采样

时序图如下:

2.模式1(CPOL=0 CPHA=1)

CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿

CPHA = 1:数据在第2个跳变沿(下降沿)采样

时序图如下:

3.模式2(CPOL=1 CPHA=0)

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 0:数据在第1个跳变沿(下降沿)采样

时序图如下:

4.模式3(CPOL=1 CPHA=1)

CPOL = 1:空闲时是高电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿

CPHA = 1:数据在第2个跳变沿(上升沿)采样

时序图如下:

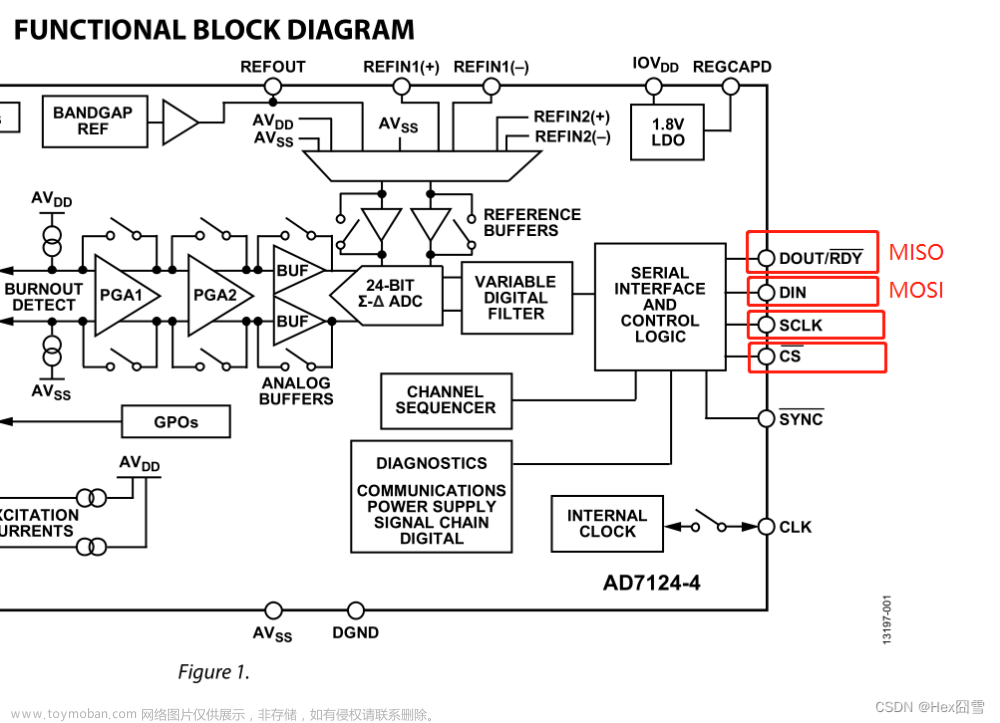

三、示例分析

实际芯片的Datasheet中,大部分是不会给出SPI时序图工作模式,此时需要根据时钟和数据读取方式判断工作模式。

从CLK看支持Mode 0,空闲时低电平,第一个上升沿采样。

时序分析如下:

-

CS拉低,开始通信;

-

CLK引脚上出现脉冲,在脉冲的边沿上,I/O引脚开始脱离高阻态,最多占用一个时钟周期;

-

MOSI引脚发送指令0x0Bh,MISO引脚处于高阻态,占用八个时钟周期;

-

MOSI引脚按照大端序发送24位地址,先发送高字节,MISO引脚处于高阻态,共占用24个时钟周期;

-

MOSI和MISO均进入高阻态,等待八个时钟周期;

-

MOSI进入空闲,MISO上开始出现数据脉冲,在该芯片上,数据按照写入的顺序读出,读出N个字节,占用N*8个时钟周期;

-

CS拉高,MOSI/MOSI进入高阻态,CLK引脚回到空闲电平,通信结束。

本文来源于网络,参考原文:《SPI时序,看不懂你打我》

补充知识1-多从机配置模式

SPI多从机配置模式

菊花链模式

参考原文:《深入剖析 SPI 通信原理及应用》

补充知识2-SPI通信速率

SPI通信速率

SPI的作为master或者slave时可以达到的最大传输速率是多少呢?

I2C协议v2.1规定了100K,400K和3.4M三种速率(bps)。

SPI是一种事实标准,由Motorola开发,并没有一个官方标准。已知的有的器件SPI已达到50Mbps。具体到产品中SPI的速率主要看主从器件SPI控制器的性能限制。文章来源:https://www.toymoban.com/news/detail-785549.html

因此SPI的最大传输速率主要受到以下几个条件影响:

1.SPI的最大时钟频率

2.CPU处理SPI数据的能力

3.输出端驱动能力(PCB所允许的最大信号传输速率)

参考原文:《SPI通信介绍》文章来源地址https://www.toymoban.com/news/detail-785549.html

到了这里,关于SPI硬件设计、协议、速率全解析的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!