一、实验目的

(1)学习并掌握Quartus II的使用方法

(2)学习简单时序电路的设计和硬件测试。

(3)学习使用VHDL 语言方法进行逻辑设计输入

(4)进一步熟悉QuartusⅡ及其 LPM_ROM 与 FPGA硬件资源的使用方法,学习较复杂的数字系统设计方法,并在实验开发系统上熟悉运行输入及仿真步骤原理

二、实验仪器设备

(1) PC机一台。

(2)Quartus Ⅱ开发软件一套

(3)EDA实验开发系统一套(EP1C12Q240C8)

三、实验原理

正弦信号发生器的结构由4部分组成:数据计数器或地址发生器、波形数据ROM、D/A和滤波电路。性能良好的正弦信号发生器的设计要求此4部分具有高速性能,且数据 ROM在高速条件下,占用最少的逻辑资源,设计流程最便捷,波形数据获取最方便。

数据计数器或地址发生器产生控制ROM波形数据表的地址,输出信号的频率由ROM地址的变化速率决定,变化越快,输出频率越高。

波形数据表ROM用于存放波形数据,可以存放正弦波、三角波或者其他波形数据。

D/A转换器将ROM 输出的数据转换成模拟信号,经过滤波电路后输出。

四、实验内容

在Quartus Ⅱ上完成正弦信号发生器设计,包括仿真和资源利用情况(假设利用Cyclone器件)。然后在实验系统上实测,包括Quartus Ⅱ测试、FPGA中 ROM在系统数据读写测试和利用示波器测试。最后完成配置器件的编程。

五、实验步骤

(1)启动Quartus II建立一个空白工程,然后命名为 rom.qpf。

(2)新建VHDL 源程序文件rom.bdf,输入程序代码并保存,进行综合编译,若编译过程中发现错误,则找出并更正错误,直至编译成功为止。

(3)5位计数器生成方法,选择工具栏的File→New→Device Dising→VHDL File→OK,在原程序输入窗口输入以下程序,后保存并编译。编译成功后单击工具栏的File→Credte Update→ Create Symbol Files for Current File

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED. ALL;

ENTITY CNT6b IS

PORT (CLK: IN std_logic;

CQ: OUT std_logic_vector(5 downto 0));

END CNT6b;

ARCHITECTURE behav OF CNT6b IS

BEGIN

PROCESS(CLK)

variable CQI :std_logic_vector(5 downto 0);

BEGIN

IF CLK'EVENT AND CLK='1'THEN

IF CQI<4 THEN CQI:=CQI + 1;

END IF;

END IF;

CQ<= CQI;

END PROCESS;

END behav;

编译成功后双击已创建的rom.bdf原理图窗口弹出如下图窗口,单击窗口左上脚Project即可看到刚才建好的CNT6b工程文件,用鼠标左键选择CNT6b,再单击ok即可将cnt6原理图模块调入原理图窗口。

(4)设计LPM_ROM相关元件,打开Mif任意波编辑器Mif_Maker2010,选择“设定波形”-“全局参数”,修改数据长度为64,数据宽度为8,如图所示。

打开Tools菜单,选择MegaWizard Plug-In Manager,操作如下:

点击“Next”,输出文件信息(文件类型:VHDL;文件地址:D:/Users/DELL/Desktop/sinve/;文件名称:data_rom)

点击Next后,导入设计的.mif文件,如下图所示:

选择产生文件类型,默认产生data_rom.vhd,可以自由选择产生更多的文件

首先在文件夹D:/Users/DELL/Desktop/sinve/中找到生成的文件data_rom.v;将data_rom.v设为当前工程,并对其编译;选择File-Create/Update-Create Symbol Files for Current File,生成data_rom元件

(5)选择目标器件并对相应的引脚进行锁定,在这里所选择的器件为Altera公司 Cyclone系列的EPIC12Q240C8芯片。将未使用的管脚设置为三态输入。则找出并更正错误,

(6)对该工程文件进行全程编译处理,若在编译过程中发现错误直至编译成功为止。接到PC机的打印机并口

(7)拿出 Altera Byte Blaster II下载电缆,并将此电缆的两端分别接到PC机的打印机并口和实验箱的JTAG下载口上,打开电源,执行下载命令,把程序下载到 FPGA器件中,观察示波器显示状态。

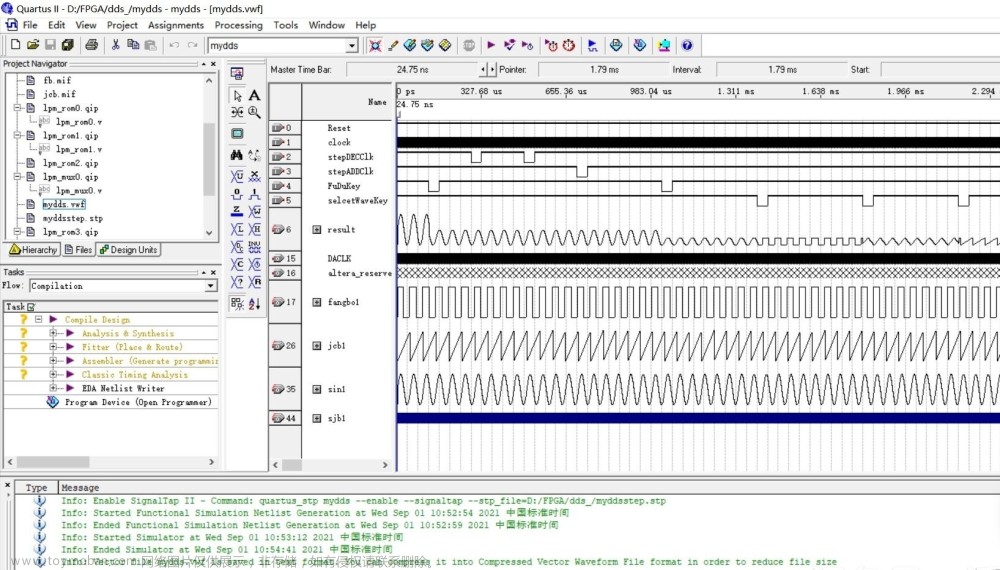

QUARTUS II效果展示图:

(注:此图中三个data_rom从上到下依次是方波,正弦波,三角波具体做实验时接其一即可)

成果展示图:

引脚配置:

六、实验要求

(1)选择实验电路模式5

(2)设计仿真文件,进行软件验证

(3)用VHDL程序设计方法实现信号发生器设计

(4)通过下载线下载到实验系统上进行硬件测试验证文章来源:https://www.toymoban.com/news/detail-785606.html

七、实验扩展

工程文件下载:

正弦,方波,三角波信号发生器设计源工程代码文章来源地址https://www.toymoban.com/news/detail-785606.html

到了这里,关于正弦信号发生器设计——VHDL的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!