资源下载地址:https://download.csdn.net/download/sheziqiong/85628810

资源下载地址:https://download.csdn.net/download/sheziqiong/85628810

数字逻辑与数字系统设计之电梯控制器设计

一、设计目的及要求

设计要求

-

电梯最少可以往返于0—9层楼。

-

乘客要去的楼层数A可手动输入并显示,按取消键可清除本次输入。

-

可自动显示电梯运行的楼层数B

-

当A>B时,电梯上升;

当A<B时,电梯下降;

当A=B时,电梯停止运行并开门;

-

可以自动显示电梯每一次启停之间的运行时间

-

任何时候按下复位键,电梯回到1层。

设计目的

目的是对“数字逻辑”课程内容全面、系统的总结、巩固和提高。根据数字逻辑的特点,选择相应的题目,在老师的指导下,由学生独立完成。通过实验使我们掌握数字逻辑电路设计的基本方法和技巧,正确运用vivado软件及实验室多功能学习机硬件平台,完成所选题目的设计任务,并掌握数字逻辑电路测试的基本方法,训练学生的动手能力和思维方法。通过实验,一方面提高运用数字逻辑电路解决实际问题的能力,另一方面使学生更深入的理解所学知识,为以后的计算机硬件课程的学习奠定良好的基础。

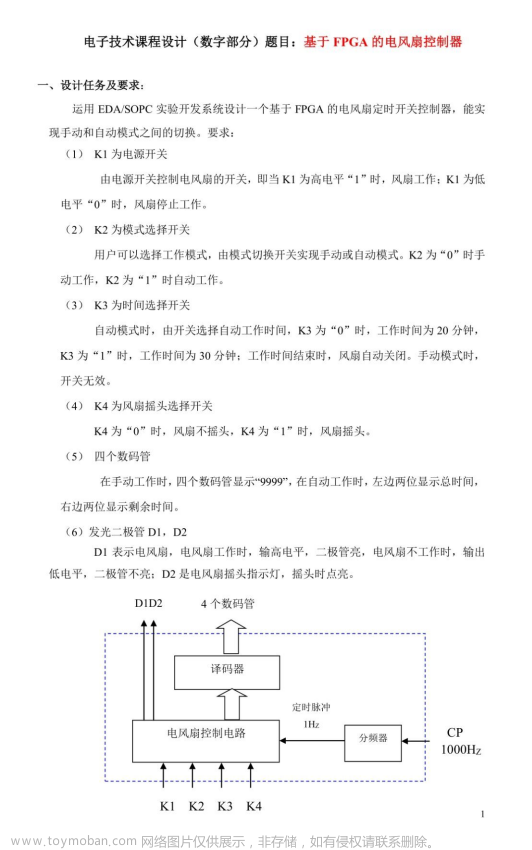

二、工作原理和系统框图

工作原理

本实验使用板上的四个开关来模拟电梯的叫梯按键,其中每个按钮有两个状态0和1,4个组成了电梯的叫楼层,将这4位二进制数字看成8421BCD码,转换成十进制数字。

对于电梯按键,当没用用户叫梯时,叫梯的数码管BIT5(G1)显示为0;当有用户叫梯时,控制叫梯的数码管显示为用户所叫的电梯楼层。

电梯运行时,显示电梯运行层数的数码管BIT1(G2)显示电梯运行的层数,假设电梯每运行一层的时间为1s,则该数码管BIT1(G2)数码管在转变为“0”之前显示的数字即为电梯运行的时间。

当SW1-N4 为1时,电梯回到0层。

系统框图

三、各部分模块具体功能及设计思路

各部分选定方案

1.目的:电梯可以往返于0~9层楼,显示当前电梯的楼层B

实现方法:用计数器来实现0~9之间的变化,并通过译码器接到数码管(BIT8)上显示

2.目的:手动输入要去的楼层A ,按取消键可清除本次输入。

实现方法:A 用四个开关来表示,通过译码器接到7段数码管(BIT5)上显示相应的楼层数A。

3.目的:当A>B 时,电梯上升;当A<B 时,电梯下降;当A=B 时,电梯停止运行。

实现方法:通过比较器来比较A 与B 的大小,若A>B 电梯上升,否则电梯下降,

4.目的:可以自动显示电梯每一次启停之间的运行时间。

实现方法;继承3)的实现方法,若A>B 则计数器正向计数,若A<B 则计数器逆向计数。

5.目的:按下复位键时,电梯回到0层

实现方法:当复位启动时,则不论A 怎么输入,电梯都停在第0层。

相关模块

比较器(Compare)

输入电梯所在楼层B ,乘客要去的楼层 A ,输出O1O2,当A>B 时,输出01;当A<B 时,输出10;当A=B 时,输出00;

代码:

module Compare(A,B,O1,O2);

input [3:0]A;//要去的楼层A

input [3:0]B;//电梯所在楼层B

output O1;

output O2;

assign O1 = (A>B);//A>B 输出01

assign O2 = (A<B); //A<B 输出10

endmodule

复位模块(IfReset)

输入reset 和In ,In 是一个4位的数组。当reset=1时,Out=0,电梯无论在几楼都会回到0楼;当reset==0时,输出Out=In ,接着运行下面的功能。

代码:

module IfReset (In, Out, reset);

input [3:0] In;

input reset;

output reg [3:0]Out;

always begin #2

if(reset)

Out = 0;//如果reset = 1 则清零

else

Out = In;//如果reset!=1 则输入即为输出

end

endmodule

节拍发生器(BeatGenerator)

由于数码管只有七个管脚,AB 不能同时显示在同一个数码管上,所以通过节拍发生器来选择显示。因为时钟频率高达100MHz,所以肉眼所见的是A 和B 同时显示。

代码:

module BeatGenerator(in1,in2,clk,sec,Out);

input [6:0]in1;//输入A

input [6:0]in2;//输入B

input clk;//时钟信号

output reg [1:0]sec;

output reg [6:0]Out;

reg [7:0]ControlLED;//七段数码管

initial //初始化变量

begin

sec = 1;

Out = in1;

ControlLED = 0;

end

always @(posedge clk)

begin

ControlLED = ControlLED + 1;

if(sec==1) //分频显示

begin

Out =in2;

end

else

begin

Out=in1;

end

end

always @(negedge ControlLED)

begin

if(sec==1)

begin

sec=2;

end

else

begin

sec=1;

end

end

endmodule

分频模块(FrequenceDivide)

将100MHz的时钟信号转换为肉眼可见的信号

代码:

module FrequenceDivide(inClk, outClk);

input inClk; //输入时钟信号

output outClk;//输出时钟信号

reg [31:0]timeClk;//暂存时钟信号(32位)

assign outClk = timeClk[19];//每2^20ns 时钟沿变化一次

initial begin

timeClk = 0;

end

always@(posedge inClk)

begin

timeClk = timeClk + 1;

end

endmodule

译码器(Decoder)

将4位的A和B转换为七段数码管显示对应的数字

代码:

module Decoder(floor, outLED, on);

input [3:0]floor;//楼层

input on;//运行状态 运行on=1,未运行on=0

output reg[6:0]outLED;//输出的显示

always @(*)

begin

if(!on)

outLED=7’b0000001;//未运行状态

else

case(floor)

4’b0000:outLED=7’b1111110; //0

4’b0001:outLED=7’b0110000; //1

4’b0010:outLED=7’b1101101; //2

4’b0011:outLED=7’b1111001; //3

4’b0100:outLED=7’b0110011; //4

4’b0101:outLED=7’b1011011; //5

4’b0110:outLED=7’b1011111; //6

4’b0111:outLED=7’b1110000; //7

4’b1000:outLED=7’b1111111; //8

4’b1001:outLED=7’b1111011; //9

default: outLED= 7’b1001111; /E(error) endcase

end

endmodule

计时器(clock)

计时器有一个暂停键与计数器的使能端相连,当switch1=switch0=0时,计时器的暂停键有效,计时器不计时;当switch1=1或switch0=1,计时器工作,且每次计时完成后归零,并从下一次电梯开始工作时计时。

代码:

module clock(

input show,

input clk,

input pause,

input rst,

output reg sm_bit,

output reg[6:0]sm_seg

);

reg [3:0]timesec0;

initial

begin

sm_bit=1;

sm_seg=1;

timesec0=0;

end

always @(posedge clk)

begin

if(pause)

begin

if(timesec0==9)

timesec0=0;

else

timesec0=timesec0+1;

end

end

always@(posedge show)

begin

case(timesec0)

0:sm_seg= 7’b1111110; //0

1:sm_seg= 7’b0110000; //1

2:sm_seg= 7’b1101101; //2

3:sm_seg= 7’b1111001; //3

4:sm_seg= 7’b0110011; //4

5:sm_seg= 7’b1011011; //5

6:sm_seg= 7’b1011111; //6

7:sm_seg= 7’b1110000; //7

8:sm_seg= 7’b1111111; //8

9:sm_seg= 7’b1111011; //9

default: sm_seg= 7’b0000000; //空白

endcase

end

endmodule

可逆计数器

module counter(

input clk,

input switch0,

input switch1,

output reg[3:0] sl_reg

);

initial begin

sl_reg = 0;

end

always @(posedge clk)

begin

case({switch0,switch1})

2’b01:sl_reg=sl_reg-1;

2’b10:sl_reg=sl_reg+1;

default:;

endcase

end

endmodule

四、调试过程

- 检查Verilog 代码是否有语法错误(由vivado 自动检测)

- 检查各个IP 核的功能是否正确,看它的仿真波形图是否正确

- 检查逻辑图中的IP 核连线是否正确,人工代特值进入电路看是否有输出错误。

- 至此调试过程结束

附录:各模块仿真结果

1比较器

2复位模块

3节拍发生器

4译码器

5计时器

6可逆计数器文章来源:https://www.toymoban.com/news/detail-785705.html

资源下载地址:https://download.csdn.net/download/sheziqiong/85628810

资源下载地址:https://download.csdn.net/download/sheziqiong/85628810文章来源地址https://www.toymoban.com/news/detail-785705.html

到了这里,关于基于FPGA和Verilog实现的9层电梯控制器仿真设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!