一、实验目标

能够熟练的进行可编程逻辑器件开发,能够通过具体工程需求进行需求分析、模块划分、代码编写、功能仿真、综合分析、板级验证,能够独立正确的进行实验操作,培养学生的工程实践研究能力和动手实践能力,具备借助可编程逻辑器件开发平台和仿真工具科学的获取实验数据或实验现象,并能够对采集到的数据或实验现象进行合理的分析与解释的能力。

二、实验内容

数码管成本低廉、稳定性好、容易控制,在汽车电子中具有广泛的应用,例如汽车仪表盘、显示屏等。本实验是一个汽车数码管显示系统设计,模拟汽车仪表盘各类数据的数码管显示。

三、实验要求

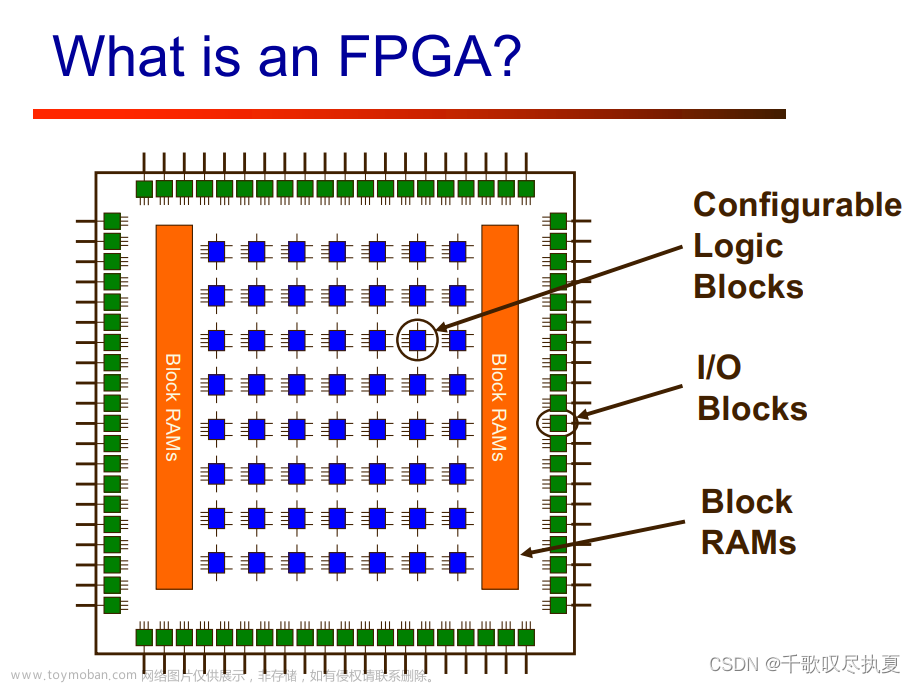

1、 使用 FPGA 开发工具 Quartus II 及仿真工具 Modelsim 打开对应工程,记录工程占用资源,说明仿真信号波形与硬件对应关系或作用;

2、 说明数码管动态扫描显示原理;

3、 分析八段式数码管显示原理及 0-9 数字显示对应关系;

4、 将给定的程序上板验证,验证是否正确,并描述正确实验现象。

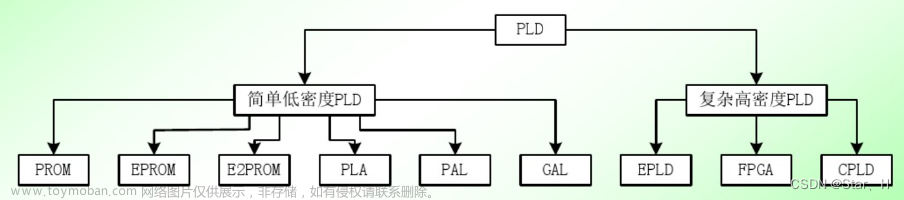

四、实验预习(实验原理、整体设计方案等)

(一)、实验基本原理:

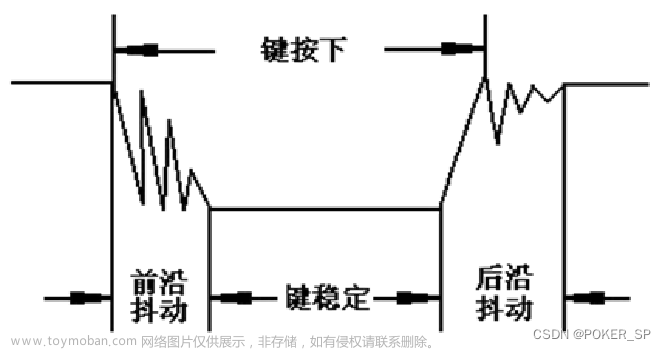

本次实验是设计一个汽车数码管显示系统,其基本设计原理为:通过控制MINI_FPGA开发板上配有的6个七段数码管 DIG1-DIG6(当正放 MINI_FPGA 开发板时,从左至右依次数过去)模拟显示汽车仪表盘上的各类数据。具体为先设置数码管的动态扫描周期,然后产生片选信号,再对片选信号进行译码使得6个数码管中所需的对应数码管启用,最后通过由Testbench设计的对应输入信号,在对应的数码管上显示出对应的数字。

(二)、整体设计方案:

1.启用所需的数码管

先确定控制动态扫描的周期为:Timex =8'd200 ,然后通过Count变量重复在动态扫描周期内重复计数、清零产生片选信号cs(由于本次实验仅启用了两个数码管,所以cs的值在0和1之间变换),再将片选信号进行译码,使得所需的对应数码管启用,由此完成数码管的启用。

2.数码管显示对应的数字

首先将待显示的数据变量SingleNum初始化为零,然后通过片选信号的不断变化,控制由Testbench上的测试文件数据赋给待显示的数据变量SingleNum,再将待显示的数据变量SingleNum译码成共阴极数码管驱动格式,使得启用的数码管显示出对应的数字。

五、测试验证(仿真、硬件测试)

仿真测试文件:

仿真结果图:

通过将仿真文件与仿真结果可以看到,当按键RST_N为0时(按键复位时),数码管启动信号DigitronCS_Out<= 6'd0 (所有数码管均不启用),且待显示数也初始化为0,同时测试文件设计的复位时间1ns与仿真结果图上现实的结果一致。

当按键RST_N为1时,在由仿真文件输入数据为Result = 8'h23 期间,对应的数码管DigitronCS_Out <= 6'b11_1110(十位)显示为Digitron_Out<= N_3(数字3);对应的数码管DigitronCS_Out<= 6'b11_1101(个位)显示为Digitron_Out <= N_5(数字5),时测试文件设计的Result = 8'h23时间区间10ns,两个数码管各自扫描一次的时间4ns与仿真结果图上现实的结果一致,测试文件与仿真结果完全一致,实验仿真成功。

六、实验小结

本次实验是通过控制MINI_FPGA开发板上配有的6个七段数码管 DIG1-DIG6模拟显示汽车仪表盘上的各类数据。我在本次实验课程中懂得了Quartus以及modelsim软件的基本使用,能够创建新的项目文件,同时也可以利用modelsim软件进行仿真。也学会了如何编写实验你代码以及测试文件,充分了解到了实验代码编写的基本结构,以及一些常用的数据类型,同时也了解到了测试代码的基本结构,以及测试代码的功能作用,并且能够编写简单的测试代码用于实验代码的测试。

我对于实验设计的过程也有了进一步的了解,能够仿照着写出一些功能简单的代码,诸如基于本次实验使得相应的数字在数码管上显示,我可以在这个功能的基础上添加按键功能,使得测试代码能够上板进行测试,通过按一个按键,使得数码管显示一个特别的数字或者符号。

本次的实验虽然简单,但是也是重要的基础,FPGA的很多项目中都需要利用数码管进行显示,用于上板测试代码是否符合自己的需求或者是显示出需要的数字符号给他人看。所有的学习都需要从基础开始,正所谓“万丈高楼平地起”,只要努力去学习提高自己,我们终会有所提高、有所进步。

七、实验代码

module sy1(

CLK ,

RST_N ,

Result ,

Digitron_Out ,

DigitronCS_Out

);

input CLK ;//外部时钟50M

input RST_N ;//复位信号

input [7:0]Result ;//输入待显示数据

output [7:0]Digitron_Out ;//数码管译码显示数据

output [5:0]DigitronCS_Out;//数码管片选

//------------信号类型申明+中间变量------------

reg [7:0]Digitron_Out ;

reg [5:0]DigitronCS_Out;

reg [7:0]Count ;//控制动态扫描周期

reg [3:0]SingleNum ;//待显示数据

reg [2:0]cs ;//片选相关中间信号

parameter Timex = 8'd200 ;//控制动态扫描周期

parameter CS_NUM= 3'd2 ;//需要用到的数码管个数

parameter N_0 = 8'b0011_1111, N_1 = 8'b0000_0110, N_2 = 8'b0101_1011,

N_3 = 8'b0100_1111, N_4 = 8'b0110_0110, N_5 = 8'b0110_1101,

N_6 = 8'b0111_1101, N_7 = 8'b0000_0111, N_8 = 8'b0111_1111,

N_9 = 8'b0110_1111;

//-----设置动态扫描周期-------------------

always @( posedge CLK )

begin

if(!RST_N)

Count <= 8'd0 ;

else if(Count == Timex)

Count <= 8'd0 ;

else

Count <= Count + 8'd1 ;

end

//---根据扫描周期产生片选信号----------

always @ ( posedge CLK )

begin

if(!RST_N)

cs <= 3'd0 ;

else if(Count == Timex)

begin

if(cs == CS_NUM - 3'd1)

cs <= 3'd0 ;

else

cs <= cs + 3'd1 ;

end

end

//------结合电路将片选信号译码---------

always @ ( posedge CLK )

begin

if(!RST_N)

DigitronCS_Out <= 6'd0 ;

else

begin

case(cs)

3'd0: DigitronCS_Out <= 6'b11_1110;

3'd1: DigitronCS_Out <= 6'b11_1101;

3'd2: DigitronCS_Out <= 6'b11_1011;

3'd3: DigitronCS_Out <= 6'b11_0111;

3'd4: DigitronCS_Out <= 6'b10_1111;

3'd5: DigitronCS_Out <= 6'b01_1111;

default: DigitronCS_Out <= 6'b11_1111;

endcase

end

end

//---------根据输入将待显示分配到个位、十位----------------

always @ ( posedge CLK )

begin

if(!RST_N)

SingleNum <= 4'd0 ;

else

begin

case(cs)

3'd0: SingleNum <= Result[3:0];//个位

3'd1: SingleNum <= Result[7:4];//十位

default: SingleNum <= 4'd0;

endcase

end

end

//---待显示数据译码成共阴极数码管驱动格式-------

always @( posedge CLK )

begin

if(!RST_N)

Digitron_Out <= 8'd0 ;

else

begin

case(SingleNum)

4'd0: Digitron_Out <= N_0;//个位

4'd1: Digitron_Out <= N_1;//十位

4'd2: Digitron_Out <= N_2;//个位

4'd3: Digitron_Out <= N_3;//十位

4'd4: Digitron_Out <= N_4;//个位

4'd5: Digitron_Out <= N_5;//十位

4'd6: Digitron_Out <= N_6;//个位

4'd7: Digitron_Out <= N_7;//十位

4'd8: Digitron_Out <= N_8;//个位

4'd9: Digitron_Out <= N_9;//十位

default: Digitron_Out <= 8'd0;

endcase

end

end

endmodule

八、测试文件

// Copyright (C) 1991-2013 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

// *****************************************************************************

// This file contains a Verilog test bench template that is freely editable to

// suit user's needs .Comments are provided in each section to help the user

// fill out necessary details.

// *****************************************************************************

// Generated on "04/08/2022 11:33:50"

// Verilog Test Bench template for design : sy1

//

// Simulation tool : ModelSim-Altera (Verilog)

//

`timescale 1 ps/ 1 ps

module sy1_vlg_tst();

// constants

// general purpose registers

//reg eachvec;

// test vector input registers

reg CLK;

reg RST_N;

reg [7:0] Result;

// wires

wire [5:0] DigitronCS_Out;

wire [7:0] Digitron_Out;

// assign statements (if any)

sy1 i1 (

// port map - connection between master ports and signals/registers

.CLK(CLK),

.DigitronCS_Out(DigitronCS_Out),

.Digitron_Out(Digitron_Out),

.RST_N(RST_N),

.Result(Result)

);

initial

begin

CLK = 0 ;

RST_N = 0 ;

Result = 8'h12 ;

#1000;

RST_N = 1 ;

Result = 8'h23 ;

#10000;

Result = 8'h48 ;

#10000;

Result = 8'h51 ;

#10000;

Result = 8'h64 ;

#10000;

Result = 8'h73 ;

#10000;

Result = 8'h26 ;

#10000;

$stop;

end

always #10 CLK = ~CLK ; 文章来源:https://www.toymoban.com/news/detail-785708.html

endmodule文章来源地址https://www.toymoban.com/news/detail-785708.html

到了这里,关于可编程逻辑器件之数码管显示实验的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!