前言

本文共6个应用题, 8个计算题, 12个简答题, 均是根据我们学校往年考试重点挑出来的, 看的快的话大概1个小时就能看完, 计算机组成原理突击复习的话看课程和课本已经不现实了, 知识点太多太杂, 看不过来的, 最好就是直接做题, 因为着重的考点就那几种题目, 记住怎么做就行了, 不用知道为什么, 看完再对着题目过一遍及格绝对没问题.

题目总结:

三 应用题:

1.CPU与存储器的连接

-

根据题目确定系统程序区和用户程序区的容量

- 一般CPU的规格不会变, 就是16根地址线(代表画图时CPU的A0~A15端口), 8根数据线(代表画图时CPU的D0~D7端口), 8根数据线代表数据是8位的, 我们在选择ROM和RAM芯片也要尽量选择相应位数.

- 入手点是根据题目的要求(一般会有三点, 第一点就是两种芯片的容量, 对应地址线, 也就是数据的地址)选择合适的芯片, 系统程序区只能用ROM, 用户程序区只能用RAM. 例如本题中要求我们最小4k为系统程序区, 联系上面的CPU8根数据线, 那么就是要求我们用ROM芯片组成一个4k×8位的ROM芯片. 4096~16383地址对应(16383-4096+1)也就是12k的地址, 那么就是要求我们设计一个12k×8位的RAM芯片.

-

选择合适的芯片

-

注意, 题目不会直接给我们正好合适的芯片, 需要我们自己去扩展, 有字扩展和位扩展两种. 两个2k×8位可以合成一个4k×8位, 这就是字扩展. 两个4k×4位可以合成一个4k×8位, 这就是位扩展. 字扩展和位扩展的区别体现在画图上, 位扩展则芯片连接CPU对应的数据线, 比如两个4k的芯片合成一个8k的芯片, 那么这两个4k芯片分别连接CPU的D0D3端口和D4D7端口. 字扩展则对应74138译码器的输出端(不必知道74138译码器是什么, 只要记住怎么画和分清输入端输出端即可).

-

如图:

-

-

将十六进制的容量用二进制写出来, 分别对应ROM和RAM的芯片的容量.

-

比如该题中要求系统程序区4k容量, 对应的十六进制应该是1000H, 但是因为地址是从0开始计数, 所以系统程序区地址对应的十六进制就是0000H~0FFFH. 用户地址区则是409616383也就是1000H3FFFH.

-

注意两片ROM对应1个4k容量. 三个RAM对应12K容量, 也就是1个RAM对应1个4k容量, 写成二进制:

-

-

最关键的一步, 根据二进制地址分配的表画出逻辑图.

-

这一部分是拿分的关键, 首先CPU和74138译码器的图要自己记住, 考试时直接画上去. 画上对应芯片数量的矩形并注明是哪种芯片

注意布局, 合适的布局会让等下连接芯片更加清晰好看. -

根据芯片的容量来选择连接CPU的几根地址线, 例如本题中两种芯片的容量都是4k的(这里不看位数), 4k=2^12次方, 也就是连接12根地址线, 注意从A0开始.

-

没有用到的最低三位地址线去和74138的CBA输入端连接. 注意地址线从低到高依次和74138输入端的ABC连接.

-

G2B非和G2A非均和CPU地址线中没有用到的且恒为0的端口连接.

-

G1和恒为1的端口连接, 没有的话可以画一条线并注明5V, 表示外部连接.

-

根据CBA三个输入连接的CPU地址线的二进制数, 来确定输出(Y0~Y7), 并连接到对应的芯片上. 有时需要注意

-

最后将RAM芯片连接到W/R非上即可.

-

如图:

-

参考连接: 存储器与CPU的连接_yrdelft的博客-CSDN博客_存储器与cpu的连接

2.设计主存地址

统一块长, Cache容量, 主存容量三者的单位, 最好都换算成B的单位(1B代表1个字节, 1B=8b. 1b代表1位).

全相联有两部分: 主存字块标记, 字块内地址

-

首先确定块长, 也就是每个字块有多少字节, 然后将该数字换算成2^X的形式, 那么字块内地址就是x.

-

主存字块标记等于将主存容量换成2^z的形式后, z - x即为主存字块标记大小.

- 全相联是最简单的一种, 出题时大概率会放在第一问.

直接映射有三部分: 主存字块标记, Cache字块地址, 字块内地址

- 字块内地址不变.

- Cache字块地址等于将Cache容量换成2^y的形式后, y - x即为Cache字块地址大小.

- 主存字块标记等于将主存容量换成2^z的形式后, z - y - x即为主存字块标记大小.

二路组相联: 主存字块标记, 组地址, 字块内地址

- 首先字块内地址不变.

- 2^(y-x)除n路组相联(这里是二路, n = 2)然后换算成2^m次方即为组地址.

- 主存字块标记等于将主存容量换成2^z的形式后, z - x - m即为主存字块标记大小.

3.磁盘的技术指标

磁盘计算题一般都是改改数, 记住计算公式就可以. 计算磁道周长时π视为3.14.

例题: 磁盘组有 6 片磁盘, 每片有两个记录面, 最上最下两面不用. 存储区域内直径 20cm, 外直径 40cm, 道密度为 20 道/cm, 内层位密度 400 位/cm, 转速 2400 转/分.

-

共有多少存储面可用?

-

一共6片, 每片有上下两个记录面, 最上最下两面不用. 则一共有6*2-2=10

-

共有多少个柱面?

-

柱面数量 = 有效存储区域(存储区域外半径 − 存储区域内半径) ∗ 道密度

-

柱面数量即为一个盘面上的磁道数量, 和有多少可用存储面无关.

-

注意, 题目所给的内 / 外径为直径.

-

本题中: 有效存储区域长度 = 40/2 - 20/2 = 10 (cm)

柱面数 = 10 × 20 = 200 (道), 即200个柱面.

-

-

盘组总存储容量是多少?

-

盘组总容量 = 存储面数 * 柱面数 * 每道信息量(每条磁道容量)

-

每道信息量 = 位密度 * 对应磁道周长

-

磁道长度就是题目中所给的位密度所对应的内层或外层周长.

-

本题中给的是内层位密度, 所以先算内层磁道周长 = 2 * r * π = 62.8 cm

每道信息量 = 400 * 62.8 = 25120 位. 单位可以转成字节, 也可以不转, 25120b = 3.14KB

盘组总容量 = 10 * 200 * 3.14KB = 6280KB = 6.28 MB

-

-

数据传输率多少?

-

数据传输率 = 转速(单位要转化为多少转每秒) * 每道信息量

-

本题中: 转速 = 2400转 / 分 = 40转 / 秒

数据传输率 = 40 * 3.14KB = 125.6 KB / 秒 = 0.1256 MB / 秒

-

-

如果某文件长度超过一个磁道的容量, 应将它记录在同一个存储面上, 还是记录在同一个柱面上, 为什么?

- 记录在同一个柱面上, 因为不需要重新寻找磁道, 数据读写速度快.

- 没有为什么, 记住就行了.

4.虚拟存储器的工作原理

虚页号 = 页号, 主存实页面号 = 页框号 = 物理块号, 有效位=该页面当前是否存在于内存中

这种题把握好三个数字即可.

例题: 某存储器按字节编址, 虚拟地址空间大小为 16MB, 主存地址空间大小为1MB, 页面大小为 4KB.

-

虚拟地址共有几位, 哪几位表示页号? 物理地址共有几位, 哪几位表示物理页号?

-

虚拟地址空间大小为16MB = 2 ^ 24 B, 所以虚拟地址有24位, 因为页面大小为4KB = 2 ^ 12 位, 所以页内地址12位.

24 - 12 = 12 所以高12位表示页号(虚页号). 因为主存地址空间大小为1MB = 2 ^ 20 位, 所以物理地址有20位, 20 - 12 = 8 所以高8位表示物理页号(页框号).

-

-

虚拟地址010C60H所在的页面是否在主存中? 若在主存中, 则该虚拟地址对应的物理地 址是什么? (页表如下图所示)

-

虚页号 有效位 页框号 0 1 06 1 1 04 2 1 15 3 1 02 4 0 - 5 1 2B 6 0 – 7 1 32 - 由第一问已知虚拟地址010C60H的低12位C60H为页内地址, 高12位010H为页号, 查询表格发现虚页号为2(010视为二进制则表示十进制的2)的有效位是1, 所以已经存入主存中, 对应页框号是15H, 所以对应的物理地址是15C60H.

5.中断和 I/O系统

CPI 为5(即执行每条指令平均需5个时钟周期). 在做I/O系统的题时要注意, 这里的1M与1B的换算关系是1M = 1000KB = 10^6B .

例题: 某计算机的 CPU 主频为 400MHz, CPI 为 5. 假设某外设的数据传输率为 0.5MB/s, 采用中断方式与主机进行数据传送, 以 32 位为传输单位, 对应的中断服务程序包含 18 条指令, 中断服务的其他开销相当于 2 条指令的执行时间. 请回答下列问题, 要求给出计算过程.

- 在中断方式下, CPU 用于该外设 I/O 的时间占整个CPU时间的百分比是多少?

- CPU用于外设I/O的时间占整个CPU时间的百分比 = 1秒钟内用于中断的开销 / CPU 主频

- 1秒钟内用于中断的开销 = CPU每次用于数据传送的时钟周期数 * 外设每秒申请中断次数

- 外设每秒申请中断次数 = 外设的数据传输率 / 传输单位(转化为B)

- CPU每次用于数据传送的时钟周期数 = (中断服务程序 + 中断服务的其他开销) * CPI

- 第一问要牢牢记住这4个式子

- 本题中: 外设的数据传输率为 0.5MB/s, 以 32 位为传输单位, 32b = 4B, 外设每秒申请的中断次数 = 0.5MB / (4B) = 5 * 10^5 / 4 = 125000. 中断服务程序包含 18 条指令, 中断服务的其他开销相当于 2 条指令的执行时间, CPI 为5, CPU每次用于数据传送的时钟周期数 = 5 * (18 + 2) =100. 1秒钟内用于中断的开销 = 100 * 125000 = 12.5M个时钟周期. CPU 主频为 400MHz, CPU 用于该外设 I/O 的时间占整个CPU时间的百分比 = 12.5M / 400MHz = 3.125%.

- 当该外设的数据传输率达到 5MB/s 时, 改用 DMA 方式传送数据. 假定每次 DMA 传送块大小为 5000B, 且 DMA 预处理和后处理的总开销为 500 个时钟周期, 则 CPU 用于该外设 I/O 的时间占整个 CPU 时间的百分比是多少? (假设 DMA 与CPU 之间没有访存冲突)

- CPU用于外设I/O的时间占整个CPU时间的百分比 = CPU用于DMA处理的总开销 / CPU 主频

- CPU用于DMA处理的总开销 = 1秒钟内需产生的DMA次数 * DMA 预处理和后处理的总开销

- 1秒钟内需产生的DMA次数 = 外设的数据传输率 / 每次 DMA 传送块大小

- 第二问只需要三个式子, 两问的式子大致相同.

- 本题中: 该外设的数据传输率达到 5MB/s, 改用 DMA 方式传送数据, 假定每次 DMA 传送块大小为 5000B, 1秒钟内需产生的DMA次数 = 5MB / 5000B = 1000. DMA 预处理和后处理的总开销为 500 个时钟周期, CPU用于DMA处理的总开销 = 1000 * 500 = 0.5M个时钟周期. CPU用于外设I/O的时间占整个CPU时间的百分比 = 0.5M / 400MHz.

6.指令系统

这道题能领悟多少全看造化…

例题: 某计算机字长为16位, 主存地址空间大小为128KB, 按字编址. 采用字长指令格式, 指令名字段定义如下:

| *OP(4位)* | *Ms(3位)* | *Rs(3位)* | *Md(3位)* | *Rd(3位)* |

|---|---|---|---|---|

| 操作码 | 源操作数寻址方式 | 源寄存器 | 目的操作数寻址方式 | 目的寄存器 |

转移指令采用相对寻址, 相对偏移用补码表示, 寻址方式定义如下:

| Ms/Md | 寻址方式 | 助记符 | 含义 |

|---|---|---|---|

| 000B | 寄存器直接 | Rn | 操作数=(Rn) |

| 001B | 寄存器间接 | (Rn) | 操作数=((Rn)) |

| 010B | 寄存器间接、自增 | (Rn)+ | 操作数=((Rn)), (Rn)+1->Rn |

| 011B | 相对 | D(Rn) | 转移目标地址=(PC)+(Rn) |

注: (X)表示有存储地址X或寄存器X的内容, 请回答下列问题:

- 该指令系统最多可有多少指令? 该计算机最多有多少个通用寄存器? 存储地址寄存器(MAR)和存储数据寄存器(MDR)至少各需多少位?

- 指令数 = 2^OP位数 OP表示操作码, 操作码有4位, 则该指令系统最多可有2 ^ 4 = 16条指令.

- 通用寄存器数量 = 2^寄存器位数 寄存器有3位, 则寄存器最多有2 ^ 3 = 8个寄存器.

- MDR的位数等于计算机的字长 计算机字长为16位, 所以MDR最少需要16位.

- MAR的位数 = log 2 (主存地址空间大小 / 计算机字长(单位转化为B)) 主存地址空间大小为128KB, 计算机字长16位 = 2B, 128KB / 2B = 2^16, 所以至少需要16位的MAR.

- 若操作码 0001B 表示加法操作(助记符为 add), 寄存器R4和R5 的编号分别为100B和101B, R4 的内容为 1234H, R5 的内容为 5678H, 地址1234H中的内容为 5678H, 地址5678H中的内容为 1234H, 则汇编语句 “add (R4), (R5)+” (逗号前为源操作数, 逗号后为目的操作数)对应的机器码是什么(用十六进制表示)? 该指令执行后, 哪些寄存器和存储单元的内容会改变? 改变后的内容是什么?

- 对应的机器码 = 操作码 + R4的寻址方式位 + R4的编号二进制表示 + R5的寻址方式位 + R5的编号二进制表示 本题中: 操作码给出: 0001B, R4和R5的寻址方式位分别为001B和010B, R4和R5的编号分别为4和5, 所以语句 “add (R4), (R5)+”对应的机器码二进制表示 = 0001001100010101B, 转化为十六进制 = 1315H

- 因为R4和R5对应的寻址方式是寄存器间接寻址, 语句 “add (R4), (R5)+”的意思是将(R4)和(R5)指向的内容相加并放到目的操作数中, 然后R5的内容自增, 目的操作数是R5, R4 = 1234H, (1234H) = 5678H. R5 = 5678H, (5678H) = 1234H. 1234H + 5678H = 68ACH. 指令执行后, R5和存储单元5678H的内容会改变, R5变为5679H, 存储单元5678H的内容变为68ACH.

参考链接:

题目来源于王道论坛 某计算机字长为16位,主存地址空间__牛客网 (nowcoder.com)

指令执行大题:寄存器间接寻址+执行过程(王道计组)_哔哩哔哩_bilibili

二 计算题

1.计算机性能

1G = 10^3M = 10^6KB = 10^9B

例题: 某计算机主频为1.5GHz,其指令分为 4 类,它们在基准程序中所占比例及 CPI 如下表所示。求出该机的 MIPS。

| 指令类型 | 所占比例 | CPI |

|---|---|---|

| A | 50% | 2 |

| B | 20% | 3 |

| C | 10% | 4 |

| D | 20% | 5 |

- MIPS = 计算机主频(换算成M) / 平均CPI(将不同CPI × 对应比例并汇总求和)

- 本题中: MIPS = 1500 M / (2 * 0.5 + 3 * 0.2 + 4 * 0.1 + 5 * 0.2) = 500

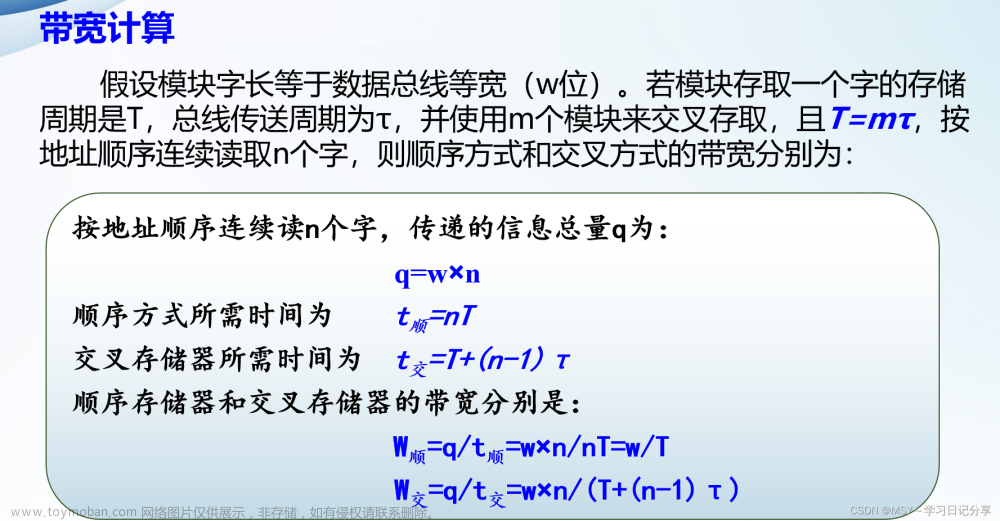

2.计算总线带宽

例题: 设总线的时钟频率为 8MHz, 一个总线周期等于两个时钟周期. 如果一个总线周期中并行传送 32 位数据, 则计算总线宽度和总线的带宽各是多少?

- 总线宽度 = 总线位宽 = 一个总线周期中并行传送多少位数据

- 总线的传输速率 = 总线带宽 = (总线位宽 / 8位) * (总线工作频率 / 总线周期时钟数). 通常单位: MB / s (MBps)

- 本题中: 总线宽度 = 32位 = 4B. 总线的时钟频率为 8MHz, 一个总线周期等于两个时钟周期, 总线带宽 = 4B * (8 MHZ / 2) = 16MB / s.

3.计算CRC码

例题: 有一个 (7, 4) 码 (即CRC码为7位, 信息码为4位), 已确定生成多项式为: 1011. 被传输的信息C(x) = 1000, 求C (x) 的CRC码 (写出具体步骤).

- CRC码很简单, 先看被传输的信息是否满足n位(也即CRC码的位数), 如果不满足就在后面补零. 然后用得到的n位CRC码 (这里是1000 000) 去除所确定的多项式, 这里是1011, 最后所得的余数取n - m (m是被传输的信息的位数) 位补在被传输的信息后面即可. 注意, 这里的除其实是逐位异或的意思, 只是形式上很像除法.

- 本题中: 被传输的信息C(x) = 1000, CRC码为7位, 可暂得CRC码1000000, 然后如图所示可得余数101, 最终所得CRC码即为: 1000101

4.海明码

参考链接:

看明白什么是海明码: 可能是最详细的海明校验码(汉明码)解法_1橘猫的博客-CSDN博客_海明校验码例题

两种题型怎么做: 计算机组成原理速成、不挂科、搞定期末考试大题(横屏版)_哔哩哔哩_bilibili

注意: 第一个链接所给出的海明码求法是将校验位从后向前插入的, 当然从前面还是后面开始都可以, 但是大部分题目都是从前向后插入, 所以习惯上最好也是从前向后插入.

例题: 已知八位数据11001100采用4位校验位, 偶校验方式, 求出海明校验码. (总结海明校验码具体步骤).

- 做法在上方链接, 讲的很好, 这里只给出答案.

5.IEEE754浮点数

知识点涉及面比较广, 但是只要求会做题的话很简单.

例题: 已知x = 8.25, 求IEEE754单精度浮点数格式机器数十六进制表示形式(写出具体步骤).

-

机器数就是一个数在计算机中的二进制表示.

-

这种题就是要我们将一个十进制的数转化成一个32位的二进制数, 至于十六进制和八进制都是在二进制的基础上处理一下结果.

-

32位的二进制数由三部分组成: 1位的符号位, 8位的阶码, 23位的尾数码组成. 不用管这些名词, 只要记住位数和怎么求就可以了.

-

符号位看给定的数是正还是负, 0正1负.

-

将所给的数转化成二进制后, 再转化成1.xxx的形式, 例如8.25 = 1000.01B = 1.00001 * 2^3 B.

-

2的幂 + 127再转化为二进制就是我们要求的阶码, 不足8位在前面补零. 所得到的1.00001小数点后面的00001就是尾数码, 不足23位就在后面补零. (不要管为什么加127, 记住就行了).

-

本题中: x = 8.25 = (1000.01)B = ( 1.000 01×2^3 )B, E(阶码) = e(我们得到的3) + 127 = 130 = (1000 0010 )B,

单精度浮点数格式: 1位数符, 8位阶码 (含阶符), 23位尾数. 故IEEE 754单精度浮点数表示为:

0 1000 0010 000 0100 0000 0000 0000 0000 即0100 0001 0000 0100 0000 0000 0000 0000 即41040000H

参考连接:

【计算机组成原理】十进制转IEEE754单精度浮点数格式_哔哩哔哩_bilibili

【计算机组成原理】IEEE754单精度浮点数转十进制_哔哩哔哩_bilibili

6.流水线的基本运算和流水线的相关性处理

单位换算:

- 1s = 1* 10^3 ms = 1 * 10^6 μs = 1 * 10^9 ns. 1G = 1 * 10^3 MB = 1 * 10^6 KB = 1 * 10^9 B

明确公式:

-

CPU时钟周期为△t, m阶指令流水线, 连续处理n条指令

-

吞吐率: TP = n / ((m + n − 1) ∗ △t) 加速比: Sp = (n * m * △t) / ((m + n - 1) * △t)

-

CPU时钟频率(主频) = 1 / 时钟周期

-

执行n条指令需要m + ( n − 1 )个时钟周期

例题: 计算机采用 5 段流水方式, 每段执行需1个时钟周期T, 若连续执行 30 条指令, 则流水线所需的时钟周期数是多少? 求出流水线的加速比Sp和吞吐率 TP(写出简要步骤).

- m段流水方式 = m级指令流水线.

- 本题中: 时钟周期数 = (5 + 30 - 1) * T = 34T. TP = 30 / ((5 + 30 - 1) * T) = 17 / (15 * T). Sp = (5 * 30 * T) / (34 * T) = 75 / 17.

参考链接: (5条消息) 流水线性能吞吐率、加速比、效率计算_海绵泡泡~的博客-CSDN博客_流水线吞吐率加速比

7.Cache命中率问题

例题: 假设CPU执行某段程序时, 共访问Cache命中950次, 访问主存50次. Cache的存取周期为50ns, 主存的存取周期为300ns. 求Cache - 主存系统的命中率, 平均访问时间和效率.

- 命中率 = (共访问Cache命中次数 / (共访问Cache命中次数 + 访问主存次数) ) * 100%.

- 平均访问时间 = 命中率 * Cache的存取周期 + (1 - 命中率) * 主存的存取周期.

- 效率 = Cache的存取周期为50ns / 平均访问时间.

- 性能提高 = (主存的存取周期 / 平均访问时间) - 1.

- 本题中: 命中率 = 950 / (950 + 50) * 100% = 95% 平均访问时间 = 0.95 * 50 + 0.05 * 300 = 62.5 效率 = 50 / 62.5 = 80% 性能提高 = 300 / 62.5 - 1 = 4.8 - 1 = 3.8 倍

8.机器数的最大值最小值

基础知识点.

例题: 设机器字长为n = 8位(其中1位为符号位), 求出对于整数, 当机器数分别代表无符号数, 原码, 补码和反码时, 对应真值的最大值和最小值为多少?(先写机器数, 再求真值).文章来源:https://www.toymoban.com/news/detail-785920.html

-

无符号数 原码 补码 反码 最大值机器数 1,1111111 0,1111111 0,1111111 0,1111111 最大值真值 255 127 127 127 最小值机器数 0,0000000 1,1111111 1,0000000 1,0000000 最小值真值 0 -127 -128 -127 -

说明一下 -128, -128是由反码1, 1111111 + 1得到的, 他的原码是1, 0000000, 显然这是 -0, 而 -0是没有意义的, 所以就拿来给 -128用了.文章来源地址https://www.toymoban.com/news/detail-785920.html

一 简答题

名词解释: 总线带宽, 总线宽度, 总线工作频率, 总线复用.

- 总线宽度: 通常指数据总线的根数.

- 总线带宽: 总线的数据传输率, 指单位时间内总线上传输数据的位数;

- 总线频率: 指总线信号的时钟频率(工作频率)

- 总线复用: 指同一条信号线可以分时传输不同的信号.

计算机中引入Cache-主存和主-辅存层次的目的分别是什么?Cache-主存层次常用的地址映像方法和替换算法分别是什么?

- Cache(高速缓冲存储器)是为了解决主存与CPU的速度差异而采用的技术, 引入主-辅存层次的目的是弥补主存容量不足.

- Cache-主存层次常用的地址映像方法是组相联映像, 替换算法是LRU替换算法.

主存单元的地址分配: 大端, 小端; 按整数边界存放

- 大端模式: 是指将数据的低位(比如 1234 中的 34 就是低位)放在内存的高地址上, 而数据的高位(比如 1234 中的 12 就是高位)放在内存的低地址上.

- 小端模式: 是指将数据的低位放在内存的低地址上, 而数据的高位放在内存的高地址上. 这种存储模式将地址的高低和数据的大小结合起来, 高地址存放数值较大的部分, 低地址存放数值较小的部分, 这和我们的思维习惯是一致, 比较容易理解.

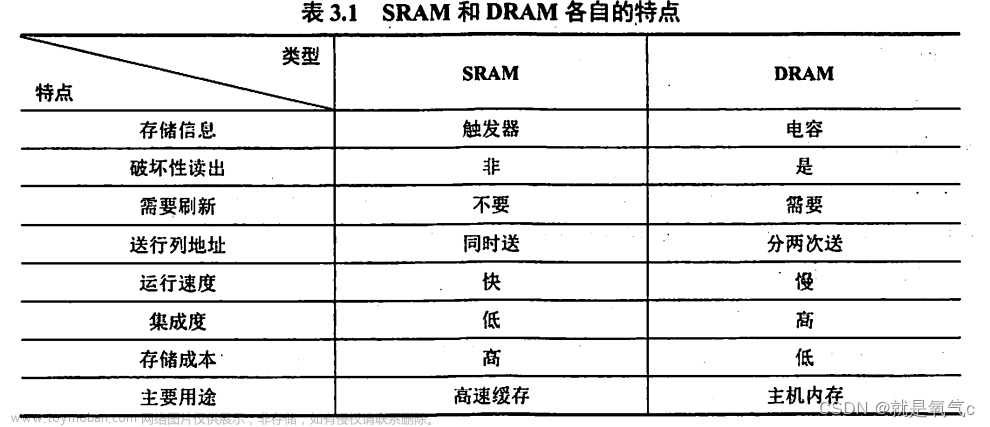

总结SRAM和DRAM的区别.

- SRAM: 读写速度快, 生产成本高, 多用于容量较小的高速缓冲存储器.

- DRAM: 读写速度较慢, 集成度高, 生产成本低, 多用于容量较大的主存储器.

动态半导体存储器(DRAM)为什么要刷新? 如何刷新?主要包含哪三种刷新方式?

- 因为动态存储器信息的存储是靠充电电容存储的, 电荷会慢慢泄漏, 所以要经常性, 周期性地充电, 这就是刷新.

- 读出的过程就是刷新的过程.

- 三种刷新方式: 集中刷新, 分散刷新, 异步刷新.

分辨率和灰度级.

- 分辨率是显示器所能显示的像素个数, 屏幕上的每一个光点就是一个像素. 以宽, 高的像素表示, 例如800 * 600 等. 像素越密, 分辨率越高, 图像越清晰.

- 灰度级: 灰度级是指黑白显示器中所显示的像素点的亮暗差别, 在彩色此案时期中测表现为颜色的不同, 灰度级越多, 图像层次越清楚逼真.

计算机内部如何判断补码加/减运算的结果是否发生溢出?

- 双符号位, 最高位进位, 符号相同操作数的运算后与原操作数的符号不同则溢出.

浮点数加减运算的步骤有哪些?

- 1.对阶. 2.尾数求和. 3.规格化. 4.舍入. 5.溢出判断.

两个浮点规格化数相乘, 是否可能需要右规? 为什么? 是否可能需要左规? 为什么? 其规格化次数可否确定?

- 两个浮点规格化数相乘, 不可能需要右规. 可能需要左规, 因为规格化的尾数是纯小数, 两个纯小数相乘不会得到整数, 但会变得更小.

- 左规最多只需一次.

简述微程序的基本思想.

- 一条微指令包含若干微命令, 控制一步操作; 一段微程序包含若干微指令, 解释执行一条机器指令; 微程序事先存放在控存中.

影响指令流水线性能的因素有哪三个?

- 1.结构相关. 2.数据相关. 3.控制相关.

简述串行总线和并行总线的特点. 现代计算机主要采用什么类型的总线.

- 串行总线数据传输时, 数据是一位一位地在通信线上传输的; 并行总线数据传输时有多个数据位同时在两个设备之间传输.

- 串行方式.

到了这里,关于【期末考试】计算机组成原理突击复习的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!