CAN总线讲解

1.基本概念:

**CAN,Controller Area Network,控制器局域网是用于解决汽车众多控制部件之间的数据交换而开发的一种串行数据通信总线。 **

2.CAN总线电平:

can总线采用差分电压传输数据,分别是CANH和CANL两根总线。总线上的信号电平分为这两条线之间的差分电压。

隐形电平:两条线静态时均为2.5V左右,压差为0,此时状态表示为逻辑1,也被称作隐性。

显形电平:当两条线电压值出现差异时,通常CAN_H=3.5V和CAN_L=1.5V,压差2-3V时,此时状态表示为逻辑0,也称作显性。

CAN总线上的逻辑是“线与”的形式,显性电平可以覆盖隐性电平,因此0可以覆盖1。

3.CAN数据帧:

CAN通信是通过以下5种类型的帧进行的:数据帧(标准格式和扩展格式,两种各式,分为:帧起始、仲裁段、控制段、数据段、CRC段、ACK段、帧结束)、遥控帧(标准格式和扩展格式)、错误帧、过载帧、帧间隔

数据帧——标准格式:

1)起始帧:SOF仅由一个显性位构成,标志数据帧和远程帧的起始,在总线空闲时才允许节点发SOF。

2)标识符:ID网络中识别某一点的信息,标准帧是11位,扩展帧的ID是29位

3)标志符扩展:IDE, IDE位为显性,表示数据帧为标准格式;IDE位为隐性,表示数据帧为扩展帧格式。

4)远程发送请求:RTR位在数据帧里必须为“显性”,而在远程帧里必须为“隐性”。 它是区别数据帧和远程帧的标志。

5)数据场:DLC,数据长度位

6)CRC段:该段用于检查帧传输错误,由15个位的CRC顺序和1个位的CRC界定符(用于分隔的位)组成

7)ACK段:此段用来确认是否正常接收,ACK段是由ACK槽(ACK Slot)和ACK界定符2个位组成,发送单元ACK段:发送2个隐性位,接收单元ACK段:接收到正确消息的单元,在ACK槽发送显性位,通知发送单元,正常接收结束, 称之为发送ACK/返回ACK

8)帧结束:End of frame,帧结束段表示该帧报文的结束,当接收到EOF 字段的最后一位且全为隐性位时,该消息被认为是有效的。 若 EOF 字段中出现显性位将会使发送器重复发送信息。

9)标准帧与扩展帧框图:

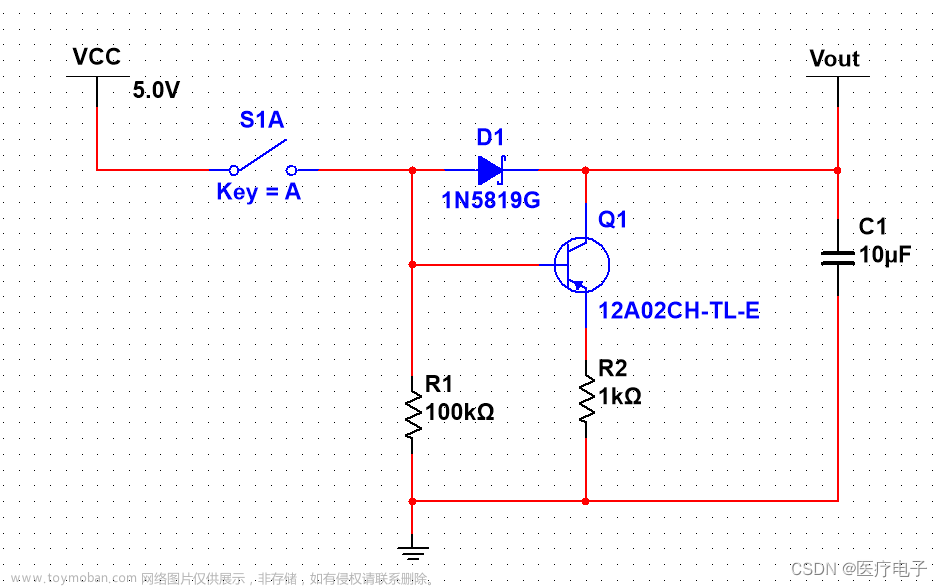

4.CAN 的原理图设计:

单片机引出接到CAN收发器,在经过防护器件,连接到端子上,如下图所示:

5.PCB设计:

can差分走线可以控120阻抗,也可以不控阻抗,丹药加粗走线就可以 ,做好隔地处理。

6.CAN电路硬件测试波形:

1)通过CAN卡接收到的数据:

2)通过示波器测量到CAN高、CAN低、CAN差分波形:

7.通过DSView逻辑分析仪查看CAN波形:

1)DSView逻辑分析仪逻辑分析接法:

0通道的地接PCB单板上的GND,0通道正接CANL,因为DSView的解码是依据逻辑上的高低电平,CANL对地的高低变化与逻辑"相符"。

2)DSView逻辑分析仪逻辑分析设置:

阈值电压设为2V, 采样时间至少要大于发送周期,采样频率设为默认的500KHz。然后点击开始进行解析,有了波形之后,再进行解码,如下图所示: 文章来源:https://www.toymoban.com/news/detail-786361.html

文章来源:https://www.toymoban.com/news/detail-786361.html

3)CAN波形解码:

按照上诉完成之后,就会出现如下的数据,对应的不同数据帧。从这里看到的是和示波器测量、CAN卡接受的数据是一样的。

以上资料主要是本人在PCB设计中和网络搜索整理而成

如有雷同或错误,希望各位大神留言指正,感谢!!! 文章来源地址https://www.toymoban.com/news/detail-786361.html

文章来源地址https://www.toymoban.com/news/detail-786361.html

到了这里,关于硬件设计 之 CAN通信-DSView逻辑分析仪使用-CAN波形测试的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!