(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

均值滤波,是图像处理中常用的手段,从频率域观点来看均值滤波是一种低通滤波器,高频信号将会去掉。均值滤波可以帮助消除图像尖锐噪声,实现图像平滑,模糊等功能。理想的均值滤波是用每个像素和它周围像素计算出来的平均值替换图像中每个像素。

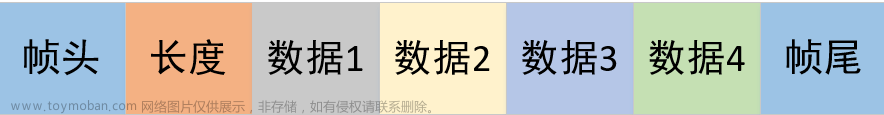

均值滤波的实现方式就是用N个点的值相加再求平均,用这个平均值代替一个点的值,思路是非常简单的,用FPGA如何实现呢?如下所示,假如我们每次用4个点求均值,那就可以选择4个时钟周期的滑窗向右滑动1个时钟周期滑动1次。开始时滑窗是在数据1,2,3,4的位置,累加后除4得到结果;下个时钟周期滑窗在数据2,3,4,5的位置,累加后除4得到结果;再下个周期滑窗在数据3,4,5,6的位置......N值比较小的时候还好处理,但是N比较大的时候,比如64个值求均值,应该如何实现呢?总不能在每个时钟周期完成64次累计吧?我们仔细观察一下,当第1个滑窗完成累加得到结果x,到第2个滑窗的时候2,3,4,5的累加值其实可以用x-d1+d5这样求出来,所以一个时钟周期完成一次加法和减法即可。

所以要计算N个值的均值,就要至少有N个寄存器用于缓存这N个数据,如果再有新的数据,那就将这N个寄存器统一移动,进来新的数据,出去旧的数据。这个操作其实就是RAM或者FIFO的功能。我们可以用数组搭建一个简单的RAM,如下所示。参数N就是数组的个数,通过wr_en,wr_addr和wr_data将数据写入数组,通过rd_en,rd_addr,rd_vld,rd_data等将数据读出数组。

在mean_filter模块中,定义了参数FILTER_CNT,用来指示多少个数据进行均值滤波,BIT_CNT是FILTER_CNT个8位数据相加,结果最大需要扩展多少位。本设计为了简单起见,避免了除法的使用,那FILTER_CNT取2,4,8,16,32......等2的BIT_CNT次幂。

计数器cnt用来控制开始的FILTER_CNT次的累加,当有新的数据要写入时,产生写使能wr_en,写地址wr_addr和写数据信号wr_data。

当已经有FILTER_CNT个数据写入RAM后,开始从RAM中读出写入时间最长的数据。在rd_domain拉高可以读取数据,这儿需要注意一下,写RAM的地址和读RAM的地址在同一个时刻是完全一样的。因为读写RAM用的都是时序逻辑,写x地址,数据在下个系统时钟才写进去,读x地址,下个时钟周期读出来的是当前时刻x地址内数据。

例化mean_ram,在RAM内数据小于FILTER_CNT时进行累加,当RAM内数据等于FILTER_CNT后进行新数据累加,同时旧数据减操作,最后输出取BIT_CNT+7到BIT_CNT位即为均值。

新建仿真tb文件来产生随机数,双击sim目录下的top_tb.bat文件,完成系统的自动化仿真。

modelsim的仿真结果如下所示,首先取8个点进行均值滤波,滤波后的输出波形随机性降低。

再取64个点进行均值滤波,滤波后的输出波形随机性进一步降低。所以可以看出,均值滤波能够抑制系统的随机噪声,点数越多,一致程度也越高。文章来源:https://www.toymoban.com/news/detail-786481.html

文章来源地址https://www.toymoban.com/news/detail-786481.html

文章来源地址https://www.toymoban.com/news/detail-786481.html

到了这里,关于孩子都能学会的FPGA:第三十课——用FPGA实现均值滤波的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!