目录

1、RGMII 接口概要

2、RGMII 接口介绍

2.1 MII接口

2.2 RMII接口

2.3 GMII接口

2.4 RGMII接口

1、RGMII 接口概要

以太网的通信离不开物理层 PHY 芯片的支持,以太网 MAC 和 PHY 之间有一个接口,常用的接口有MII、 RMII、 GMII、 RGMII 等。

MII(Medium Independent Interface, 媒体独立接口): MII 支持 10Mbps 和 100Mbps 的操作,数据位宽为 4 位

- 在 100Mbps 传输速率下,时钟频率为 25Mhz

- 在 10Mbps 传输速率下,时钟频率为 2.5Mhz

RMII(Reduced MII): RMII 是 MII 的简化版, 数据位宽为 2 位

- 在 100Mbps 传输速率下,时钟频率为 50Mhz

- 在 10Mbps 传输速率下,时钟频率为 5Mhz

GMII(Gigabit MII): GMII 接口向下兼容 MII 接口, 支持 10Mbps、 100Mbps 和 1000Mbps 的操作,数据位宽为 8 位

- 在 1000Mbps 传输速率下,时钟频率为 125Mhz

- 在 100Mbps 传输速率下,时钟频率为 25Mhz

- 在 10Mbps 传输速率下,时钟频率为 2.5Mhz

RGMII(Reduced GMII): RGMII 是 GMII 的简化版,数据位宽为 4 位

- 在 1000Mbps 传输速率下,时钟频率为 125Mhz,在时钟的上下沿同时采样数据

- 在 100Mbps传输速率下,时钟频率为25MHz,为单个时钟沿采样

- 在 10Mbps传输速率下,时钟频率为2.5MHz,为单个时钟沿采样

在千兆以太网中,常用的接口为 RGMII 和 GMII 接口。 RGMII 接口的优势是同时适用于10M/100M/1000Mbps 通信速率,同时占用的引脚数较少。但 RGMII 接口也有其缺点,就是在 PCB 布线时需要尽可能对时钟、控制和数据线进行等长处理,且时序约束相对也更为严格。

2、RGMII 接口介绍

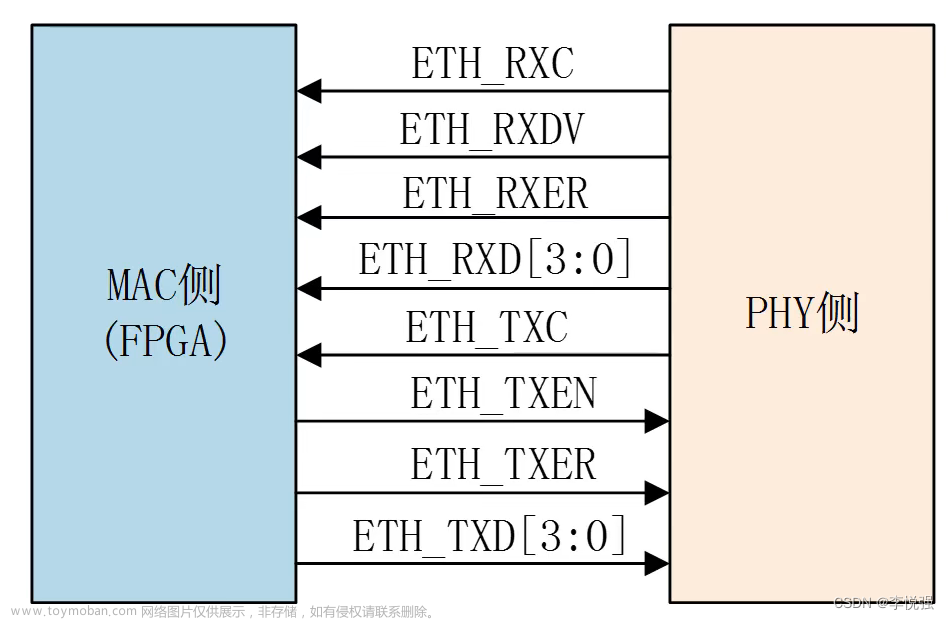

2.1 MII接口

即媒体独立接口,数据位宽为 4 位,100Mbps 速率下,时钟频率为 25MHz; 10Mbps 速率下,时钟频率为 2.5MHz

ETH_RXC:接收数据参考时钟, ETH_RXC 由 PHY 侧提供。

ETH_RXDV:接收数据有效信号,高电平有效。

ETH_RXER:接收数据错误信号,高电平有效。

ETH_RXD:四位并行的接收数据线,在ETH_RXDV为高电平,ETH_RXER为低电平数据有效。

ETH_TXC:发送参考时钟, ETH_TXC 由 PHY侧提供。

ETH_TXEN:发射数据有效信号,高电平有效。

ETH_TXER:发射数据错误信号,高电平有效。

ETH_TXD:四位并行的发送数据线,在ETH_TXEN为高电平,ETH_TXER为低电平数据有效。

2.2 RMII接口

即简化媒体独立接口,数据位宽为2位,100Mbps 速率下,时钟频率为 50MHz; 10Mbps 速率下,时钟频率为 5MHz

REF_CLK:参考时钟

CRS_DV:CRS与DV复用接口

ETH_RXER:接收数据错误信号,高电平有效。

ETH_RXD:二位并行的接收数据线。

ETH_TXEN:发射数据有效信号,高电平有效。

ETH_TXD:二位并行的发送数据线

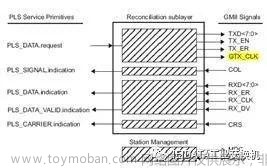

2.3 GMII接口

即千兆比特媒体独立接口,数据位宽为 8 位,1000Mbps 速率下,时钟频率为 125MHz; 100Mbps 速率下,时钟频率为 25M; 10Mbps 速率下,时钟频率为 2.5MHz

ETH_RXC:接收数据参考时钟, ETH_RXC 由 PHY 侧提供。

ETH_RXDV:接收数据有效信号,高电平有效。

ETH_RXER:接收数据错误信号,高电平有效。

ETH_RXD:八位并行的接收数据线,在ETH_RXDV为高电平,ETH_RXER为低电平数据有效。(4位数据有效)

ETH_TXC:发送参考时钟, ETH_TXC 由 PHY侧提供。

ETH_TXEN:发射数据有效信号,高电平有效。

ETH_TXER:发射数据错误信号,高电平有效。

ETH_TXD:八位并行的发送数据线,在ETH_TXEN为高电平,ETH_TXER为低电平数据有效。(4位数据有效)

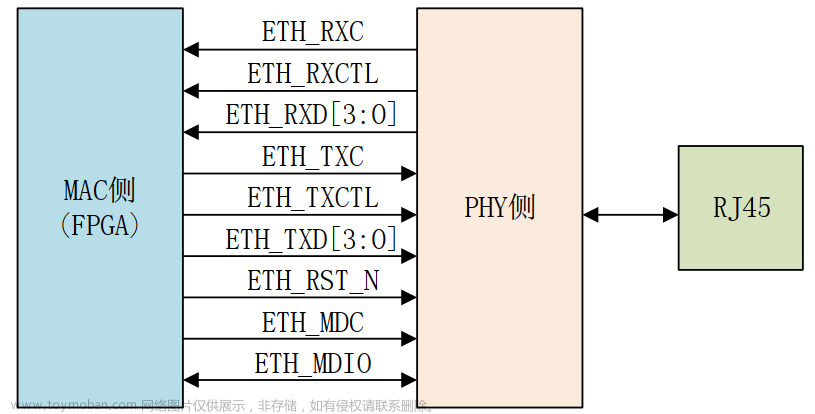

2.4 RGMII接口

即简化千兆比特媒体独立接口,数据位宽为4 位,1000Mbps 速率下,时钟频率为 125MHz; 100Mbps 速率下,时钟频率为 25M; 10Mbps 速率下,时钟频率为 2.5MHz

REF_CLK:参考时钟

ETH_RXCTL(ETH_RX_DV):接收数据控制信号。

ETH_RXD:四位并行的接收数据线。

ETH_TXCTL(ETH_TXEN):发送数据控制信号。

ETH_TXD:四位并行的发送数据线文章来源:https://www.toymoban.com/news/detail-787453.html

ETH_TXCTL 和 ETH_RXCTL 控制信号同样采用 DDR 的方式在一个时钟周期内传输两位控制信号,即上升沿发送/接收数据使能(TX_EN/RX_ DV)信号,下降沿发送/接收使能信号与错误信号的异或值(TX_ERR xor TX_EN、 RX_ERR xor RX_DV)。

文章来源地址https://www.toymoban.com/news/detail-787453.html

到了这里,关于【FPGA】RGMII接口的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!