Cadence OrCAD: 层次化设计 Hierarchical Design

为什么层次化设计

Flat versus hierarchical PCB design - which is best? - EE Times

看一篇2011年的的文章,有个2019年的评论,挺有意思的,大意是所有人都应该学会正确地做层次化设计。对newbie engineer的定义也挺有意思(退休前一直都是newbie?):

I am always amazed when I hear newbie engineers (less than 35 years’ experience) attempt to justify doing electronic schematics in Flat Sheet format.

做层次化的理由有:

- 直观地看到整个系统的信号走向,读原理图更方便。

- 成熟的模块便于复用。(扁平化设计中,每复制一个模块,可能有好多个data1要改成data2,还容易改错。)

- 便于多人合作,因为网络名称不会冲突,等等。

但其实我接触到的使用层次化设计不多,可能原因是原理图规模比较小、层次化处理操作比较麻烦、或者是公司的设计习惯和规范。比如看到Xilinx的好多板子都采用了扁平化设计,有些原理图都上百页了(当然也可能是后面用软件摊开的)。

但是做层次化设计也是有好处的,我觉得有助于理解系统结构和功能划分等等。所以花了点时间来学习,然后把一个现有的扁平原理图的做成层次化。当然写博文还是只能用下之前搭的最简单的电路。

OrCAD的层次化设计

这边只介绍自底向上的设计过程,感觉上更常用一些。先有一些现成的模块,装进子图里做一个模块,然后把模块连接成系统。

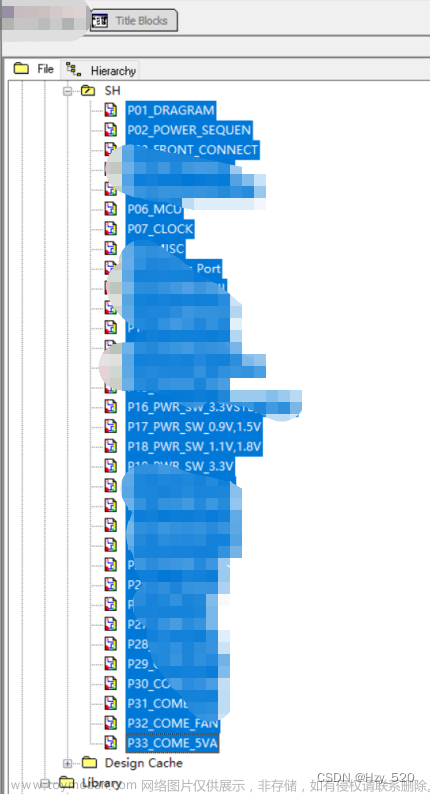

0. 处理前

系统描述:有个MCU系统(这边直接用一个连接器代替),需要接几个外设模块:2个外设1,1个外设2。 (见 Cadence OrCAD:Net Group 使用)

如果采用扁平化设计:

- MCU页面,放MCU的最小系统

- LED_I2C页面,放几个外设,复制多份,需要改网络名。

1. 制作子图

这也是之前扁平化设计中从来没用到过的功能:new schematic

- 选中设计文件.dsn-右键-new schematic,修改子图和里面页面的名称。注意子图中也可以有多页,类似于一个文件夹中的多个文件,可以用跨页符连接。

这可能也是schematic一级的图标是文件夹的原因?

修改以后:

a. MCU放置最小系统

b. LED放置外设1

d. SPI放置外设2

c. TOP是顶层,调用1份MCU、2份LED、1份SPI

- 放置端口:place-hierarchical port,放置模块的输入输出端口,严格的话需要在port的properties中确定端口是输入、输出、还是电源等,这边偷懒,全部passive。

这里port也可以用到之前的NetGroup,见 Cadence OrCAD:Net Group 使用。

3. 复制现有的电路模块,完成子图设计

2. 调用子图

- place-hierarchical block(reference为位号,可自行定义,implementation name需要选择与之前建立的原理图名相同)

-

选中模块-右键-sync-up,自动同步输入输出端口。

(而sync down用于自顶向下的设计,即定义有这个模块和端口,然后sync down,子图中会有同样的port)

-

调节端口位置。

-

(再复制一个模块用于简单测试)。

3. 最终效果

- 顶层:可以看到两个LED模块和一个SPI模块,对比SPI的端口和LED的端口,可以看到NetGroup的确有助于减少走线。

相对于平坦原理图,从顶层看,的确结构更清晰。

- LED模块

- MCU模块

- SPI模块

一些问题

- 直接做DRC会报错:主要原因是,目前两个子图的元件位号是相同的,导致位号重复的错误。

需要先选中被复用的原理图,初始化位号,再重新annotate - Navigation:双击模块,进入下一级;右键-ascend,回到上一级

- make root:右键-make root,把某一个原理图设置为顶层,参考 ORCAD层次化设计遇到Cannot descend from …_songisgood的博客-CSDN博客

文章来源:https://www.toymoban.com/news/detail-787693.html

文章来源:https://www.toymoban.com/news/detail-787693.html

本文使用的原理图放在:orcad层次化设计和NetGroup的参考原理图-嵌入式文档类资源-CSDN文库文章来源地址https://www.toymoban.com/news/detail-787693.html

到了这里,关于Cadence OrCAD: 层次化设计 Hierarchical Design的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!

![[架构之路-211]- 需求- 软架构前的需求理解:ADMEMS标准化、有序化、结构化、层次化需求矩阵 =》需求框架](https://imgs.yssmx.com/Uploads/2024/02/722948-1.jpeg)