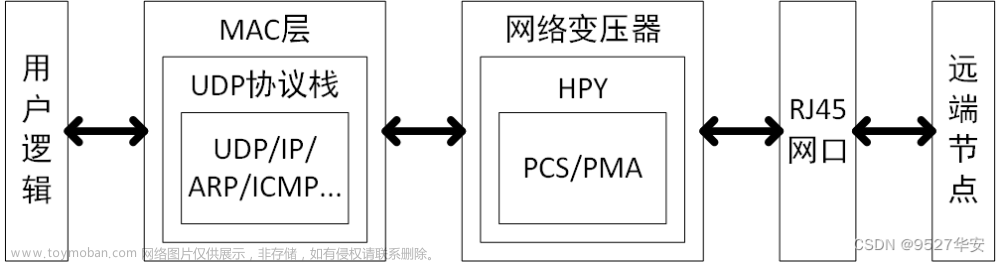

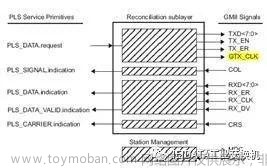

不管是SGMII还是RGMII,PHY和MAC之间的传输信息不仅包含网口数据,而且包含端口速率、半双工或全双工等指示信息,RX_DV/TX_EN/RX_ERR/TX_ERR等流控信息,还有COL和CRS。

SGMII

1、数据以1.25G(单lane)运行,时钟以625M运行(可以不用,采用自恢复功能),这是基于千兆带宽,8b/10b编码,DDR的需求而要求的参数。

2、不管是PHY侧还是MAC侧,都有发送PCS和接收PCS,接收PCS的前端会有个同步模块,推测是用于恢复时钟,这个同步模块和发送接收PCS都与自协商模块有交互,自协商模块部分后续再研究。

3、除了以上大模块外,PHY的接收模块跟往外发的TX_EN和TX_ER之间会有一个小block,用于TX_ER的抑制,基本功能应该是在TX_EN不为true时,哪怕TX_ER置位了也不往外报true,免得引发丢帧(此功能仅在全双工下用,不知道为什么)。MAC侧在PCS的后级,从RX_DV中解析出CRS,从RX_DV和TX_EN中解析出COL。

4、控制信息,包含link状态、双工配置、速率,从PHY传输到MAC,通过两侧的TX_CONFIG_REG[15:0]来实现,MAC会通过将bit14置1来答复其收到了控制信息。

5、SGMII的1.25Gbaud传输速率对于以10或100Mbps运行的接口来说是过高的。当这些情况发生时,接口通过将每个帧字节复制10次(对于100 Mbps)和100次(对于10 Mbps)来“延长”帧。起始帧定界符(SPD)每帧仅出现一次。

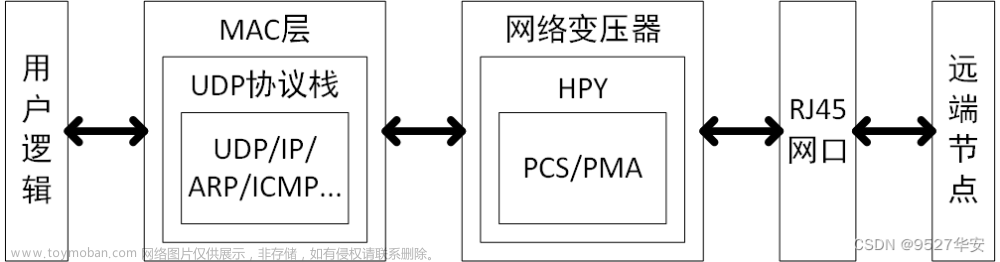

RGMII

1、对于千兆操作,时钟将在 125MHz 下运行,而对于 10/100 操作,时钟将分别在 2.5MHz 或 25MHz 下运行。

2、接口信号含:TXC TD0~TD3 TX_CTL RXC RD0~RD3 RX_CTL MDIO MDC,其中TXC和RXC分别是发送和接收的时钟信号,TD和RD分别是4bit的发送和接收信号,TX_CTL和RX_CTL是复用来传输控制信号的,MDIO和MDC是phy的配置接口。

3、数据和控制信息的复用是通过利用参考时钟的两个边沿并在上升沿发送低 4 位和在下降沿发送高 4 位来完成的。可以使用相同的技术将控制信号多路复用到单个时钟周期中。

4、TX_ERR和TX_EN编码在TX_CTL上,TX_EN在时钟上升沿采样,TX_ERR在时钟下降沿采样,RX_ERR和RX_DV也是一样。

5、为了便于检测 PHY 的链路状态、速度和双工模式,帧间信号将放置在 RXD[3:0] 信号上。

6、CRS和COL放置在 RXD[3:0]信号上。

7、用于实现 10/100 Mbps时,方法是将 100Mbps 操作的时钟速率降低到 25MHz和2.5MHz。TXC由 MAC 生成,RXC由 PHY 生成。 在数据包接收期间,RXC 可以在正脉冲或负脉冲上拉伸,以适应从自由运行时钟到数据同步时钟域的转换。 当 PHY 的速度发生变化时,允许对正脉冲或负脉冲进行类似的拉伸。 在速度转换期间不允许出现时钟故障。以 10M和 100Mbps 的速度运行时,与千兆速度的运行方式完全相同,只是数据可能在适当时钟的上升沿上复制。

8、关于RX_CTL和TX_CTL

RGMII为了节约引脚,把GMII里的RX_DV和RX_ER编码到RX_CTL上,把TX_EN和TX_ER编码到TX_CTL上。两种情况基本一致,以下仅表述RX_CTL的情况。

在RX_CLK的上升沿,采到的RX_CTL为RX_DV;而RX_CLK的下降沿,采到的信号为RX_DV(XOR)RX_ER,协议里为了描述方便,新引入了一个信号叫RX_ERR来描述这个异或表达式的结果。而关于RX_DV和RX_ER的真值表表述的几种状态:有效传输、帧间空闲、传输有误、载波扩展、载波有误与GMII一样,与RX_ERR完全无关。文章来源:https://www.toymoban.com/news/detail-787963.html

9、关于MDC和MDIO

在GMII协议里描述了MDC最高支持2.5M,但在网上RGMII资料里,写着MDC最高支持12M,不知道以哪个为准。另外网上的材料描述MDIO需要一个1.5k~10k的上拉,但GMII协议里只有在MDIO可插拔的场景里,需要在PHY侧加上拉,STA侧加上拉,用于做在位检测。文章来源地址https://www.toymoban.com/news/detail-787963.html

到了这里,关于SGMII和RGMII入门学习的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!