目录

1.算法仿真效果

2.算法涉及理论知识概要

2.1、64QAM调制解调系统的设计

2.1 信号生成

2.2 信号调制

2.3 信号解调

3.Verilog核心程序

4.完整算法代码文件

1.算法仿真效果

本系统进行了两个平台的开发,分别是:

Vivado2019.2

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition

其中Vivado2019.2仿真结果如下:

仿真结果导入matlab可以看星座图:

仿真结果导入matlab可以看星座图:

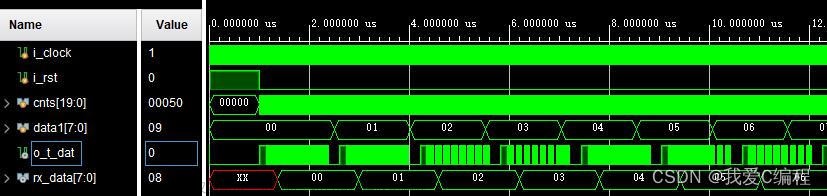

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition的测试结果如下:

2.算法涉及理论知识概要

基于FPGA的64QAM调制解调通信系统的设计和实现。首先,介绍了通信系统的基本原理和调制解调过程中需要用到的数学知识,包括正交幅度调制(QAM)和数字信号处理(DSP)算法。其次,详细介绍了64QAM调制解调系统的设计和实现步骤,包括信号生成、信号调制、信号解调和误码率测试等环节。最后,通过仿真实验和硬件实现测试,验证了系统的可行性和性能。

随着无线通信技术的不断发展,越来越多的应用需要高速、高可靠性的通信系统来传输数据。调制解调是一种常用的数字通信技术,它可以将数字信号转换成模拟信号进行传输,同时也可以将接收到的模拟信号转换成数字信号进行处理。在数字调制解调中,QAM是一种常用的调制方式,它可以将数字信号分为实部和虚部两个部分进行编码,从而实现高效的数据传输。本文旨在介绍基于FPGA的64QAM调制解调通信系统的设计和实现,包括信号生成、信号调制、信号解调和误码率测试等环节,以验证系统的可行性和性能。

2.1、64QAM调制解调系统的设计

2.1 信号生成

在64QAM调制解调系统中,需要生成一定数量的数字信号,作为调制信号和参考信号。数字信号可以使用随机数生成器产生,也可以使用特定的算法生成。在本文中,我们采用了带噪声的随机数生成器产生数字信号,其中噪声是为了模拟实际通信中的信道噪声。

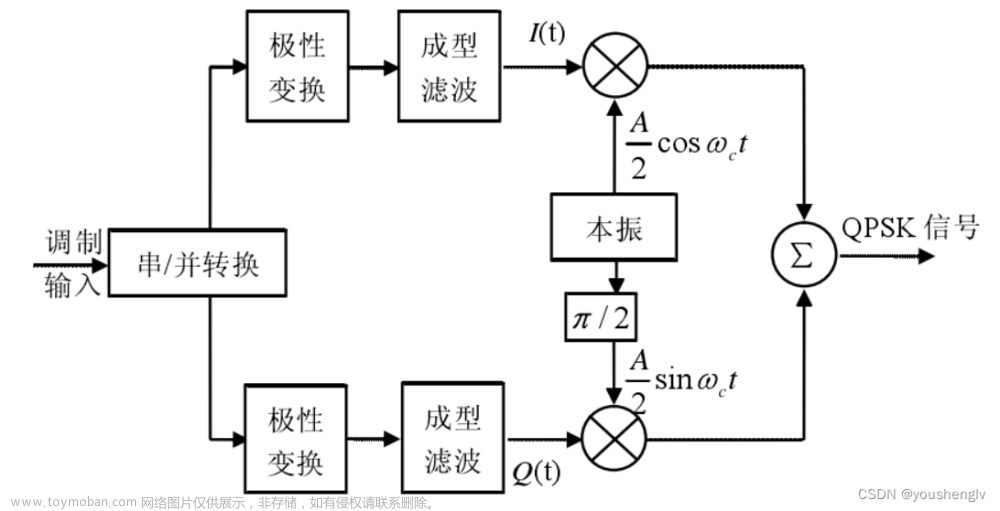

2.2 信号调制

在64QAM调制解调系统中,需要将数字信号转换成模拟信号进行传输,这个过程称为信号调制。在QAM调制中,数字信号分为实部和虚部两个部分进行编码,然后将它们分别调制到不同的载波上,最后将两个载波叠加在一起。具体来说,假设数字信号为s(n),其中n表示信号的采样点,QAM调制可以表示为:

$$

s_I(n) = A_I cos(2\pi f_c t(n))\

s_Q(n) = A_Q sin(2\pi f_c t(n))\

s(n) = s_I(n) + s_Q(n) = A_I cos(2\pi f_c t(n)) + A_Q sin(2\pi f_c t(n))

$$

其中,s_I(n)表示实部信号,s_Q(n)表示虚部信号,A_I和A_Q分别表示实部和虚部的调制系数,f_c表示载波频率,t(n)表示采样时间。在64QAM调制中,实部和虚部分别采用8QAM调制,然后叠加在一起,最终得到64QAM调制信号。

2.3 信号解调

在接收端,需要将接收到的模拟信号转换成数字信号进行处理,这个过程称为信号解调。在64QAM解调中,首先需要将接收到的信号分离成实部和虚部,然后进行8QAM解调,最后将解调后的实部和虚部重新组合成数字信号。具体来说,假设接收到的信号为$r(n)$,则可以表示为:

$$r(n) = A_I cos(2\pi f_c t(n) + \phi_I) + A_Q sin(2\pi f_c t(n) + \phi_Q)

$$

其中,A_I和A_Q分别表示实部和虚部的振幅,\phi_I和\phi_Q分别表示实部和虚部的相位。根据正交幅度调制的原理,实部和虚部信号可以通过乘以正弦和余弦信号进行解调,即:

$$

s_I(n) = r(n) cos(2\pi f_c t(n))\

s_Q(n) = r(n) sin(2\pi f_c t(n))

$$

然后,将解调后的实部和虚部信号进行8QAM解调,得到解调后的数字信号。文章来源:https://www.toymoban.com/news/detail-788724.html

3.Verilog核心程序

......................................................................

wire serial_in;

wire data_flag;

integer mixed_out;

bit_signals bit_signals_U(

.clk (clk),

.rst (rst),

.enable (start),

.serial_in (serial_in),

.data_flag (data_flag)

);

s2p s2p_U(

.clk (clk),

.rst (rst),

.start (start),

.serial_in (serial_in),

.data_flag (data_flag),

.parallel_data (parallel_data)

);

// local_oscillator local_oscillator_u(

// .clk (clk),

// .rst (rst),

// .start (start),

// .sin (sin),

// .cos (cos)

// );

wire signed[9:0]mcos;

wire signed[9:0]msin;

NCO_Trans NCO_Trans_u(

.i_clk (clk),

.i_rst (~rst),

.i_K (10'd256),

.o_cos (mcos),

.o_sin (msin)

);

assign cos={mcos,6'd0};

assign sin={msin,6'd0};

mod64QAM mod64QAM_u(

.clk(clk),

.rst(rst),

.start(start),

.parallel_data(parallel_data),

.sin(sin),

.cos(cos),

.I_com(I_com),

.Q_com(Q_com)

);

//调制输出

always @(posedge clk or negedge rst)

begin

if(~rst)

begin

I_comcos<={16{1'b0}};

Q_comsin<={16{1'b0}};

end

else begin

I_comcos<=$signed(I_com[4:0])*$signed(cos[15:5]);

Q_comsin<=$signed(Q_com[4:0])*$signed(sin[15:5]);

end

end

endmodule

00_017m4.完整算法代码文件

V文章来源地址https://www.toymoban.com/news/detail-788724.html

到了这里,关于m基于FPGA的64QAM调制解调通信系统verilog实现,包含testbench,不包含载波同步的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!