日常·唠嗑

在写这篇文章之前,对这个专栏做一个补充解释。本来按我之前的想法是,把这个专栏写成一个比较层次化,一层一层慢慢深入的系统化专栏。但是,在工作的时候,刚好在做某一件事,在这个时间段,对这个知识点比较深刻,所以就提前把这篇文章写了,导致此专栏可能没有按一步一步深入来写,会有些跳动,大家可以根据自己情况看文章。

在写零基础学FPGA(六):FPGA时钟架构(Xilinx为例,完整解读)这篇文章的时候,稍微提了一下FPGA基本结构,但是由于主题不同,所以没有深入去讲。

本篇文章,结合软硬件,讲一下FPGA基本结构。以Xilinx及Altera为例。

一、概述

可配置逻辑模块是可编程阵列的重要组成部分,是FPGA的核心部分,占据FPGA大部分的芯片面积,可编程逻辑单元是其中的基本模块。

基于查找表(Look Up Table,LUT)的可编程逻辑单元主要由以下几部分组成:两个四输入的LUT,两个进位逻辑,两个可编程触发器,还包含配置用的SRAM、信号产生模块以及控制逻辑等。

每个可编程逻辑单元中还包含一个与门资源,用来实现有效的乘法运算。LUT从本质上来说是四位地址的16×1的RAM,每个地址存放一个数值。对于任何四输入的函数,都可以写出它的真值表,然后根据它的真值表在其寄存器中对应的位置存放为“1”和“0”。这样对应不同的输入地址就得到不同的结果。(有点像卡若图那样子)可以看看这篇文章:查找表(LUT)。

其中四输入的LUT用来实现任意四输入的函数,通过两个LUT的组合可以实现任意五输入的函数,同时每个LUT还可以实现16×1的RAM和16×1的移位寄存器。进位逻辑可以实现快速的算术运算、级联函数生成器,同时也作为LUT输出函数与触发器资源之间的通道。函数生成器的输出可以直接当作模块的输出,也可以送入D触发器,然后通过D触发器输出。其中,可配置模块中的储存单元也是可以被配置的,它可以被配置成D触发器,也可以被配置成电平敏感的锁存器。可编程触发器的输入可以是函数生成器的输出也可以是其他信号直接短接函数发生器的输出。存储器还包括同步置位信号和复位信号。置位信号在配置过程中强迫存储单元回到初始化状态。复位信号使触发器变为与初始状态相反的状态,它与置位信号相反。这些控制信号也可以被配置成异步的使能信号。这些信号都是独立可以颠倒的,它们被一个可配置逻辑单元中的两个D触发器所共享。

在这里,有一篇文章,非常值得大家阅读: 你的fpga为什么不能正常工作——拆解第一款FPGA芯片分析原理。

笔者第一次看这篇文章,也大受震撼,仔细阅读,会有一种遨游在芯片海洋里的感觉,海洋里的每种生物都栩栩如生。🐟 🐳 🐋 🐬

文章部分截图:

二、基于多路选择器的逻辑单元

可编程逻辑单元是FPGA中实现各种逻辑的核心,逻辑单元的选择对FPGA的芯片面积、速度性能、CAD工具的开发都有重要影响。

J.Rosel等人在FPGA结构研究领域做了许多开创性的工作,他们引入并定义逻辑单元的功能度为逻辑单元可实现不同布尔函数的个数。随着逻辑单元功能度的增加,每个模块的引脚和面积将增加,而实现一个电路所需的模块总数相应减少,这将影响芯片中布线面积的比例。

FPGA的可编程逻辑单元主要分为三大类:基于多路选择器(MUX)或其他基本门的逻辑单元,基于PLD(Programmable Logic Device,可编程逻辑器件)结构的逻辑单元和基于LUT逻辑单元。

1、基于多路选择器的逻辑单元(早期)

FPGA较早的制造商之一Actel公司的FPGA产品主要采用基于MUX(多路选择器)的逻辑单元,时序电路也由该模块通过编程得到,采用一次编程的反熔丝(Anti.Fuse)编程技术。该公司的40MX中可编程逻辑单元结构如图所示。基于MUX的可编程逻辑单元的粒度较小、功能较弱不够灵活,但硬件面积较小,而且电路速度快。Actel公司的一些FPGA产品中(40MX/42MX等)主要采用了基于MUX的逻辑单元。

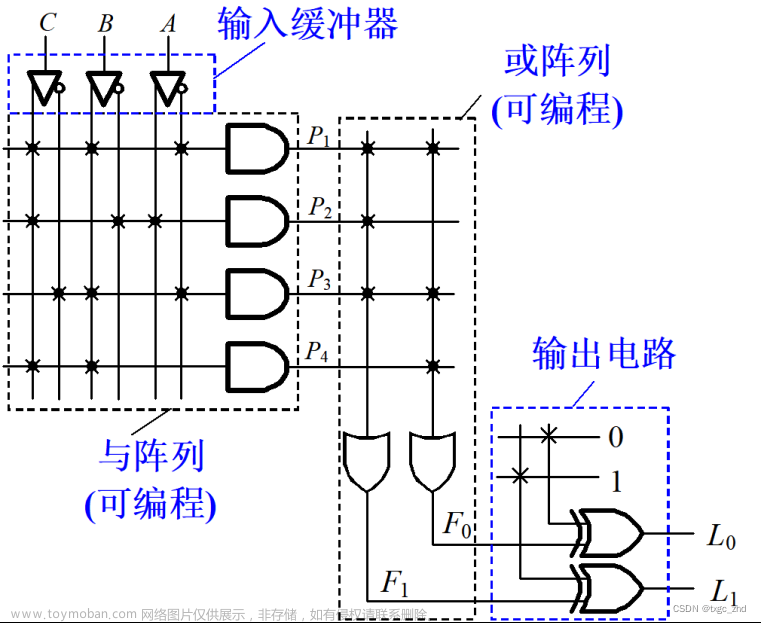

2、基于PLD结构的逻辑单元(类CPLD)

以PLD为逻辑模块的CPLD在模块结构上与简单的PLD没有本质区别,基于PLD的基本模块如图所示。当然,商用CPLD器件一般还提供一些复杂的逻辑功能,如与平面共享输入端、输出可编程反相、可编程的触发器实现时序等功能。CPLD结构中的乘积项选择模块提供乘积项分配、共享、扩展的功能,是CPLD基本模块区别于简单PLD的主要特征,提高了CPLD与或阵列的灵活性。Altera的MAX系列和XilinX公司的XC7000/9500等系列都属于这种CPLD结构。

3、基于查询表的逻辑单元(目前主流)

查找表类似于一个ROM,输入的查询表由2个SRAM单元组成,n个输入通过译码电路来决定从哪一个SRAM单元读出信息并送到唯一的输出端,而SRAM单元则按地址顺序记录函数的真值表。n输入的LUT可以实现任意n输入的逻辑函数。

对于4输入的LUT,4个输入作为地址输入,存储的内容作为布尔代数的结果。所以,4输入的LUT可以实现任意四输入的布尔函数。当前两大主流的FPGA厂商Altera和Xilinx的高性能FPGA均采用基于查找表的可编程逻辑单元的结构。

此可编程逻辑单元中还包含一个重要资源就是进位逻辑,其作用是方便加法器的实现。加法运算是FPGA设计中常用的功能,最常用且消耗资源最少的是行波加法器。这种加法器的关键路径(延时最大路径)在进位链上,因此为了提高加法器的工作频率,FPGA提供了专用的进位链。进位链贯穿了可编程逻辑阵列的每一行,以保证相互之间的连线最短,从而使加法器实现最短的关键路径,获得更高的工作频率。

关于进位链,可以参考这篇文章:影响FPGA时序的进位链(Carry Chain), 你用对了么?,做FPGA开发的人,绕不开这东西的,涉及时序约束。

在每个可编程逻辑单元中都有可编程的触发器资源,它可以根据用户需求配置成为锁存器或是上升沿触发以及下降沿触发的DFF。

与其他结构的FPGA相比,基于LUT结构具有以下的特点:

(1)逻辑分解简单。由于基于LUT结构的FPGA的可编程逻辑块都是同种类型的查找表,而k输入的查找表可以实现任意k个变量的布尔函数。因此对于电路中任意的不大于k输入并且单输出的子网络电路块均可以由一个k输入的LUT实现。在逻辑划分阶段,不必考虑特殊库单元的实现问题,只需将原始网图划分成不大于k的输入和单输出的子图就可以了。这样使得逻辑分解从一定程度上得到简化。

(2)工艺匹配简单。电路中任意的不大于k输入并且单输出的子网络电路块均可以由一个k输入的LUT实现。所以基于LUT结构的FPGA的工艺映射的工艺匹配阶段不存在选择特殊的库元素问题。

(3)通常是有输入限制的。由于k输入的LUT需要2k个单元来存贮函数的信息,当k取值增大时,LUT所需的单元数就会以指数特征上升。当k值取的较大时候,实现一个LUT所用的硅面积就会变得很大。同时较大的查找表将会影响查找时间,越大的查找表所需的查找时间也就越长。所以,通常k的取值不会超过5。在选择LUT输入数目时,要考虑面积和性能的平衡性。

三、Xilinx基本结构

Xilinx的官方文档在介绍FPGA的逻辑资源时通常是按照可配置逻辑块CLB(Configurable Logic Block)来介绍,把CLB作为FPGA里的最小逻辑单元。但是一个CLB是由2个slice构成,所以大家也常常把slice作为最小的逻辑单元。下面我们来介绍slice的组成:

V7系列FPGA的slice包含4个部分:

(1)LUT查找表,1个slice里包含4个6输入的查找表。

(2)存储单元,也就是常说的触发器,1个slice里包含8个触发器。每4个触发器为一组,可配置成D触发器或锁存器。

(3)多路复用器,也就是1位宽的数据选择器,数量非常多,足够使用。

(4)进位逻辑,它与本列的上下slice的进位逻辑相连,实现数据运算时的进位操作。

因此,许许多多的slice相结合,再加上全局时钟就能实现复杂的数字功能。另外,FPGA里的slice有2种,一种被称为sliceL,另一种被称为sliceM,有的CLB由2个sliceL构成,有的则是由1个sliceL和一个sliceM构成。SliceM除了基本功能外,可以实现RAM和移位寄存器的功能,这两种功能很有用,通过工具软件可以自动实现,不用咱们操心。

一个完整的slice:

两个slice组成一个CLB:

讲完CLB跟slice,也许有人会问,那logic cells是什么:

“logic cells” 是 Xilinx 创造提出来的一个市场说法,可以用来衡量不同内部结构甚至不同厂商的FPGA芯片的资源情况。(简单点理解,就是让你在行业里面有个统一的计量单位,让你能跟别的厂的芯片做对比)

"logic cells"代表的是一个没有其他任何功能的4输入LUT,在老一些的Xilinx的FPGA中,他们使用LUT的数目乘以1.2来计算LC的数目,因为一个LUT中还有一个进位链和MUX,这样可以使一个LC比淡出的4输入LUT实现更多功能。

在较新的FPGA中,Xilinx采用了6输入LUT,这时他们采用系数1.6。

另外请记住一个LUT对应两个FF,也就是一个查找表对应两个寄存器。

具体的换算关系,可以看一下,下面这个图。

以XC7V585T为例:

LUT总数=Slices* 4=910504=364200

Logic cells总数=LUT1.6=364200*1.6=582720

见官方文档 ug474:

7 Series FPGAs Configurable Logic BlockUser Guide

Xilinx 7系列芯片,在vivado软件上的视图:

完整芯片:

其中一个Bank:

本节,因为时间问题,没有写的特别仔细,部分细节,可以看这篇文章进行补充:

浅谈XILINX FPGA CLB单元 汇总 (CLB、LUT、存储单元、Distributed RAM、移位寄存器、多路复用器、进位逻辑(Carry Logic))。文章来源:https://www.toymoban.com/news/detail-789238.html

四、Altera 基本结构

Altera的基本结构参考这篇文章即可,写的不错:

FPGA中的基础逻辑单元–Altera。

Cyclone IV系列芯片,在Quartus ii软件上的视图:

完整芯片: 文章来源地址https://www.toymoban.com/news/detail-789238.html

文章来源地址https://www.toymoban.com/news/detail-789238.html

到了这里,关于零基础学FPGA(八):可编程逻辑单元(基本结构,Xilinx+Altera)的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!