51单片机汇编指令表–STC宏晶MCU

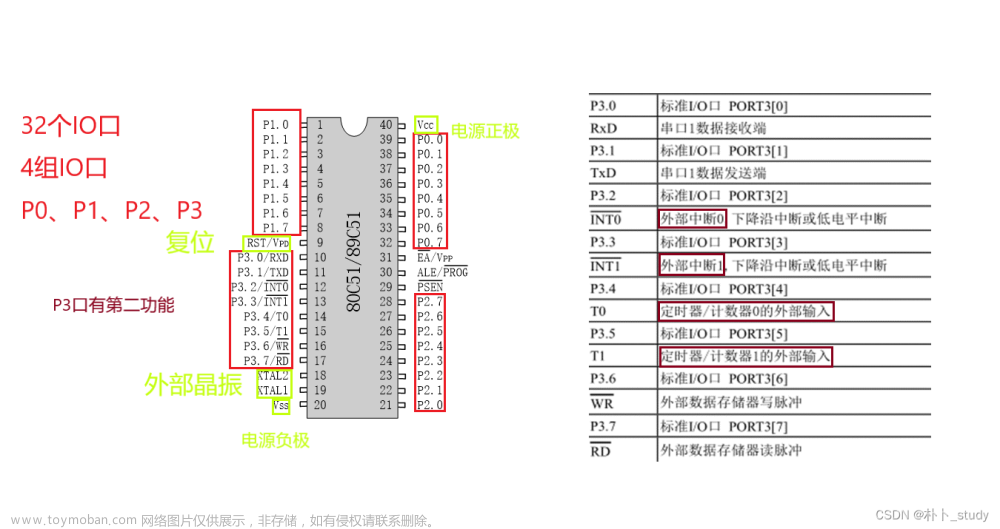

51单片机汇编指令简介

51系列单片机汇编指令表非常庞大,包含了五大类指令,以下是各类指令的一个简要概述和部分示例:

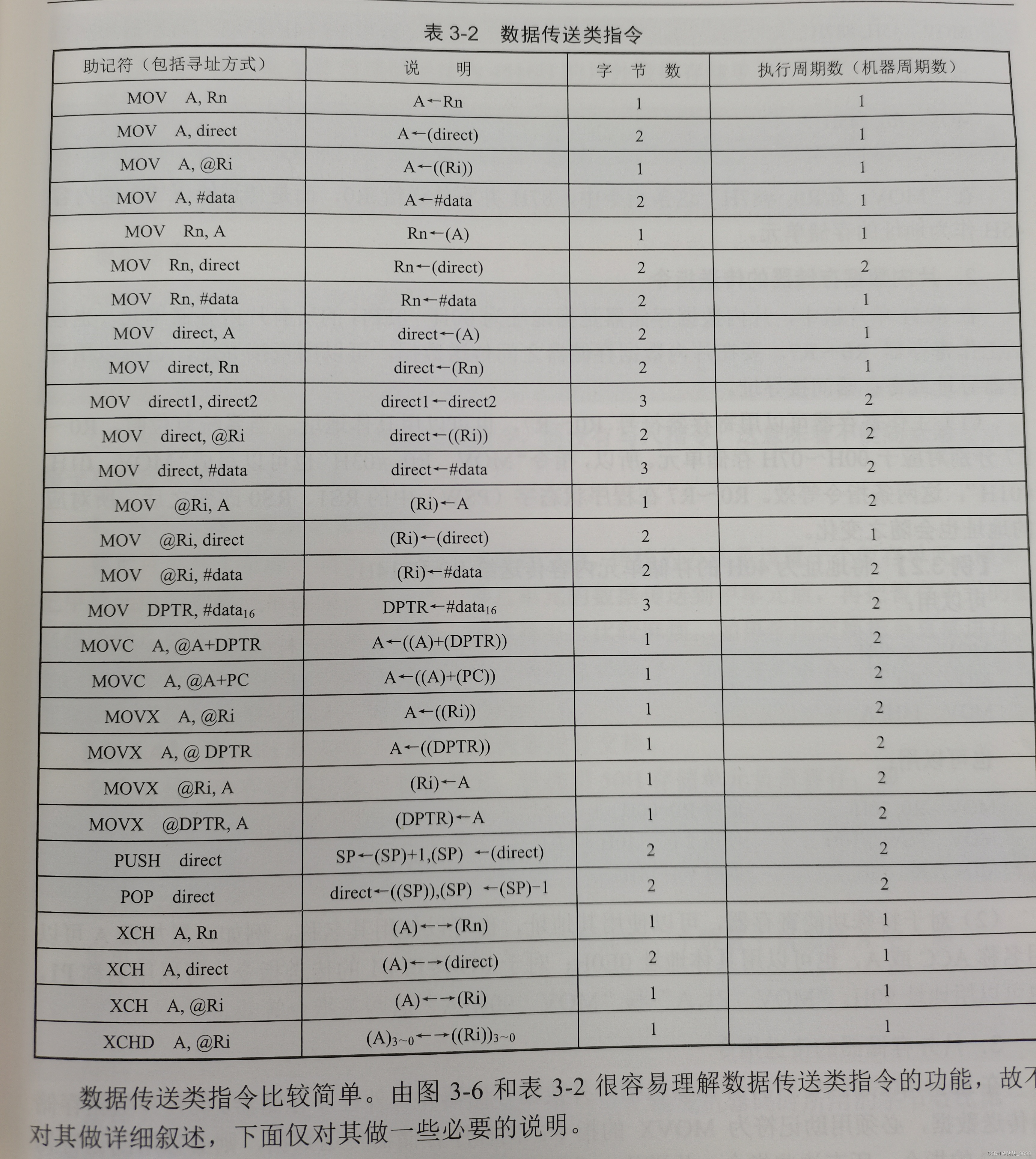

一、数据传送类指令

这些指令用于在寄存器之间、寄存器与存储单元之间以及立即数与寄存器之间的数据传输。

- MOV:通用数据传送指令

- MOV A,Rn 将工作寄存器Rn的内容传送到累加器A中。

- MOV direct,A 将累加器A的内容传送到直接地址指定的内部RAM单元。

- MOVX A,@Ri (对于访问外部RAM)通过间接寻址将外部RAM中的内容传送到累加器A(其中Ri为R0或R1)。

- MOVX @DPTR,A 向外部RAM以DPTR指向的地址写入累加器A的内容。

二、算术操作类指令

包括加法、减法、比较等操作。

- ADD、ADDC:对累加器进行加法运算。

- SUBB:带借位的减法运算。

- INC、DEC:递增或递减指定寄存器或内存单元的值。

三、逻辑运算类指令

涉及逻辑与、或、异或等操作。

- ANL(AND Logical):按位逻辑与操作。

- ORL(OR Logical):按位逻辑或操作。

- XRL(Exclusive OR Logical):按位逻辑异或操作。

四、控制转移类指令

用于程序流程控制,如条件跳转和无条件跳转。文章来源:https://www.toymoban.com/news/detail-789257.html

- JMP:无条件跳转到指定地址。

- AJMP、LJMP:短跳转和长跳转到子程序或其他地址。

- JC、JNC、JZ、JNZ 等:根据标志位状态进行条件转移。

五、位操作类指令

处理单个位的操作。文章来源地址https://www.toymoban.com/news/detail-789257.html

- SETB:设置一个位为1。

- CLR:清零一个位。

- CPL:取反一个位。

- JB(Jump if Bit Set)、JNB(Jump if Bit Not Set):依据某位的状态进行跳转。

以上只是简单的举例,并未列出所有51单片机的汇编指令。每条指令的具体格式、功能和使用情况可以参考完整的MCS-51汇编语言手册。

宏晶MCU-STC8Hxx

算术运算

| 助记符 | 指令说明 | 字节 | 时钟 |

|---|---|---|---|

| ADD A,Rn | 寄存器内容加到累加器 | 1 | 1 |

| ADD A,direct | 直接地址单元的数据加到累加器 | 2 | 1 |

| ADD A,@Ri | 间接地址单元的数据加到累加器 | 1 | 1 |

| ADD A,#data | 立即数加到累加器 | 2 | 1 |

| ADDC A,Rn | 寄存器带进位加到累加器 | 1 | 1 |

| ADDC A,direct | 直接地址单元的数据带进位加到累加器 | 2 | 1 |

| ADDC A,@Ri | 间接地址单元的数据带进位加到累加器 | 1 | 1 |

| ADDC A,#data | 立即数带进位加到累加器 | 2 | 1 |

| SUBB A,Rn | 累加器带借位减寄存器内容 | 1 | 1 |

| SUBB A,direct | 累加器带借位减直接地址单元的内容 | 2 | 1 |

| SUBB A,@Ri | 累加器带借位减间接地址单元的内容 | 1 | 1 |

| SUBB A,#data | 累加器带借位减立即数 | 2 | 1 |

| INC A | 累加器加1 | 1 | 1 |

| INC Rn | 寄存器加1 | 1 | 1 |

| INC direct | 直接地址单元加1 | 2 | 1 |

| INC @Ri | 间接地址单元加1 | 1 | 1 |

| DEC A | 累加器减1 | 1 | 1 |

| DEC Rn | 寄存器减1 | 1 | 1 |

| DEC direct | 直接地址单元减1 | 2 | 1 |

| DEC @Ri | 间接地址单元减1 | 1 | 1 |

| INC DPTR | 地址寄存器DPTR加1 | 1 | 1 |

| MUL AB | A乘以B,B存放高字节,A存放低字节 | 1 | 2 |

| DIV AB | A除以B,B存放余数,A存放商 | 1 | 6 |

| DA A | 累加器十进制调整 | 1 | 3 |

逻辑运算

| 助记符 | 指令说明 | 字节 | 时钟 |

|---|---|---|---|

| ANL A,Rn | 累加器与寄存器相与 | 1 | 1 |

| ANL A,direct | 累加器与直接地址单元相与 | 2 | 1 |

| ANL A,@Ri | 累加器与间接地址单元相与 | 1 | 1 |

| ANL A,#data | 累加器与立即数相与 | 2 | 1 |

| ANL direct,A | 直接地址单元与累加器相与 | 2 | 1 |

| ANL direct,#data | 直接地址单元与立即数相与 | 3 | 1 |

| ORL A,Rn | 累加器与寄存器相或 | 1 | 1 |

| ORL A,direct | 累加器与直接地址单元相或 | 2 | 1 |

| ORL A,@Ri | 累加器与间接地址单元相或 | 1 | 1 |

| ORL A,#data | 累加器与立即数相或 | 2 | 1 |

| ORL direct,A | 直接地址单元与累加器相或 | 2 | 1 |

| ORL direct,#data | 直接地址单元与立即数相或 | 3 | 1 |

| XRL A,Rn | 累加器与寄存器相异或 | 1 | 1 |

| XRL A,direct | 累加器与直接地址单元相异或 | 2 | 1 |

| XRL A,@Ri | 累加器与间接地址单元相异或 | 1 | 1 |

| XRL A,#data | 累加器与立即数相异或 | 2 | 1 |

| XRL direct,A | 直接地址单元与累加器相异或 | 2 | 1 |

| XRL direct,#data | 直接地址单元与立即数相异或 | 3 | 1 |

| CLR A | 累加器清0 | 1 | 1 |

| CPL A | 累加器取反 | 1 | 1 |

| RL A | 累加器循环左移 | 1 | 1 |

| RLC A | 累加器带进位循环左移 | 1 | 1 |

| RR A | 累加器循环右移 | 1 | 1 |

| RRC A | 累加器带进位循环右移 | 1 | 1 |

| SWAP A | 累加器高低半字节交换 | 1 | 1 |

数据传输

| 助记符 | 指令说明 | 字节 | 时钟 |

|---|---|---|---|

| MOV C,bit | 直接地址位送入进位位 | 2 | 1 |

| MOV bit,C | 进位位送入直接地址位 | 2 | 1 |

| MOV A,Rn | 寄存器内容送入累加器 | 1 | 1 |

| MOV A,direct | 直接地址单元中的数据送入累加器 | 2 | 1 |

| MOV A,@Ri | 间接地址中的数据送入累加器 | 1 | 1 |

| MOV A,#data | 立即数送入累加器 | 2 | 1 |

| MOV Rn,A | 累加器内容送入寄存器 | 1 | 1 |

| MOV Rn,direct | 直接地址单元中的数据送入寄存器 | 2 | 1 |

| MOV Rn,#data | 立即数送入寄存器 | 2 | 1 |

| MOV direct,A | 累加器内容送入直接地址单元 | 2 | 1 |

| MOV direct,Rn | 寄存器内容送入直接地址单元 | 2 | 1 |

| MOV direct,direct | 直接地址单元中的数据送入另一个直接地址单元 | 3 | 1 |

| MOV direct,@Ri | 间接地址中的数据送入直接地址单元 | 2 | 1 |

| MOV direct,#data | 立即数送入直接地址单元 | 3 | 1 |

| MOV @Ri,A | 累加器内容送间接地址单元 | 1 | 1 |

| MOV @Ri,direct | 直接地址单元数据送入间接地址单元 | 2 | 1 |

| MOV @Ri,#data | 立即数送入间接地址单元 | 2 | 1 |

| MOV DPTR,#data16 | 16位立即数送入数据指针 | 3 | 1 |

| MOVC A,@A+DPTR | 以DPTR为基地址变址寻址单元中的数据送入累加器 | 1 | 4 |

| MOVC A,@A+PC | 以PC为基地址变址寻址单元中的数据送入累加器 | 1 | 3 |

| MOVX A,@Ri | 扩展地址(8位地址)的内容送入累加器A中 | 1 | 3[1] |

| MOVX A,@DPTR | 扩展RAM(16位地址)的内容送入累加器A中 | 1 | 2[1] |

| MOVX @Ri,A | 将累加器A的内容送入扩展RAM(8位地址)中 | 1 | 3[1] |

| MOVX @DPTR,A | 将累加器A的内容送入扩展RAM(16位地址)中 | 1 | 2[1] |

| PUSH direct | 直接地址单元中的数据压入堆栈 | 2 | 1 |

| POP direct | 栈底数据弹出送入直接地址单元 | 2 | 1 |

| XCH A,Rn | 寄存器与累加器交换 | 1 | 1 |

| XCH A,direct | 直接地址单元与累加器交换 | 2 | 1 |

| XCH A,@Ri | 间接地址与累加器交换 | 1 | 1 |

| XCHD A,@Ri | 间接地址的低半字节与累加器交换 | 1 | 1 |

布尔操作

| 助记符 | 指令说明 | 字节 | 时钟 |

|---|---|---|---|

| CLR C | 清零进位位 | 1 | 1 |

| CLR bit | 清0直接地址位 | 2 | 1 |

| SETB C | 置1进位位 | 1 | 1 |

| SETB bit | 置1直接地址位 | 2 | 1 |

| CPL C | 进位位求反 | 1 | 1 |

| CPL bit | 直接地址位求反 | 2 | 1 |

| ANL C,bit | 进位位和直接地址位相与 | 2 | 1 |

| ANL C,/bit | 进位位和直接地址位的反码相与 | 2 | 1 |

| ORL C,bit | 进位位和直接地址位相或 | 2 | 1 |

| ORL C,/bit | 进位位和直接地址位的反码相或 | 2 | 1 |

| JC rel | 进位位为1跳转 | 2 | 1/3[2] |

| JNC rel | 进位位为0跳转 | 2 | 1/3[2] |

| JB bit,rel | 直接地址位为1则跳转 | 3 | 1/3[2] |

| JNB bit,rel | 直接地址位为0则跳转 | 3 | 1/3[2] |

| JBC bit,rel | 直接地址位为1则跳转,该位清0 | 3 | 1/3[2] |

程序分支

| 助记符 | 指令说明 | 字节 | 时钟 |

|---|---|---|---|

| ACALL addr11 | 短调用子程序 | 2 | 3 |

| LCALL addr16 | 长调用子程序 | 3 | 3 |

| RET | 子程序返回 | 1 | 3 |

| RETI | 中断返回 | 1 | 3 |

| AJMP addr11 | 短跳转 | 2 | 3 |

| LJMP addr16 | 长跳转 | 3 | 3 |

| SJMP rel | 相对跳转 | 2 | 3 |

| JMP @A+DPTR | 相对于DPTR的间接跳转 | 1 | 4 |

| JZ rel | 累加器为零跳转 | 2 | 1/3[2] |

| JNZ rel | 累加器非零跳转 | 2 | 1/3[2] |

| CJNE A,direct,rel | 累加器与直接地址单元不相等跳转 | 3 | 2/3[3] |

| CJNE A,#data,rel | 累加器与立即数不相等跳转 | 3 | 1/3[2] |

| CJNE Rn,#data,rel | 寄存器与立即数不相等跳转 | 3 | 2/3[3] |

| CJNE @Ri,#data,rel | 间接地址单元与立即数不相等跳转 | 3 | 2/3[3] |

| DJNZ Rn,rel | 寄存器减1后非零跳转 | 2 | 2/3[3] |

| DJNZ direct,rel | 直接地址单元减1后非零跳转 | 3 | 2/3[3] |

| NOP | 空操作 | 1 | 1 |

- 1、访问外部扩展 RAM 时,指令的执行周期与寄存器 BUS_SPEED 中的 SPEED[2:0]位有关

- 2、对于条件跳转语句的执行时间会依据条件是否满足而不同。当条件不满足时,不会发生跳转而继续执行下一条指令,此时条件跳转语句的执行时间为 1 个时钟;当条件满足时, 则会发生跳转,此时条件跳转语句的执行时间为 3 个时钟。

- 3、对于条件跳转语句的执行时间会依据条件是否满足而不同。当条件不满足时,不会发生跳转而继续执行下一条指令,此时条件跳转语句的执行时间为 2 个时钟;当条件满足时,则会发生跳转,此条件跳转语句的执行时间为 3 个时钟

到了这里,关于51单片机汇编指令表--STC宏晶MCU的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!