复位电路作为数字逻辑设计中一个重要电路,不管是FPGA还是ASIC设计中都会经常使用,可以说复位信号在数字电路里面的重要性仅次于时钟信号。复位的主要目的是使芯片电路进入一个已知的,确定的状态。主要是触发器进入初始状态。复位一般分为同步复位和异步复位,可以由硬件开关触发引起,也可以由复位逻辑控制引起。

一、 同步复位

同步复位:同步复位指的是当时钟上升沿检测(有效沿)到复位信号,执行复位操作,有效的时钟沿是前提。

1.1 同步复位的实现方式

//*******************同步复位模块******************//

//-----------端口定义-------------------------------

module rst_test(

input clk , //系统时钟

input rst_n , //复位信号,低电平有效

input in , //输入信号

output reg out //输出信号

);

//-----------输出模块-------------------------------

always@(posedge clk )begin

if(!rst_n)

out <= 1'b0; //复位将输出置零

else

out <= in; //其他时候将输入赋值给输出

end

endmodule

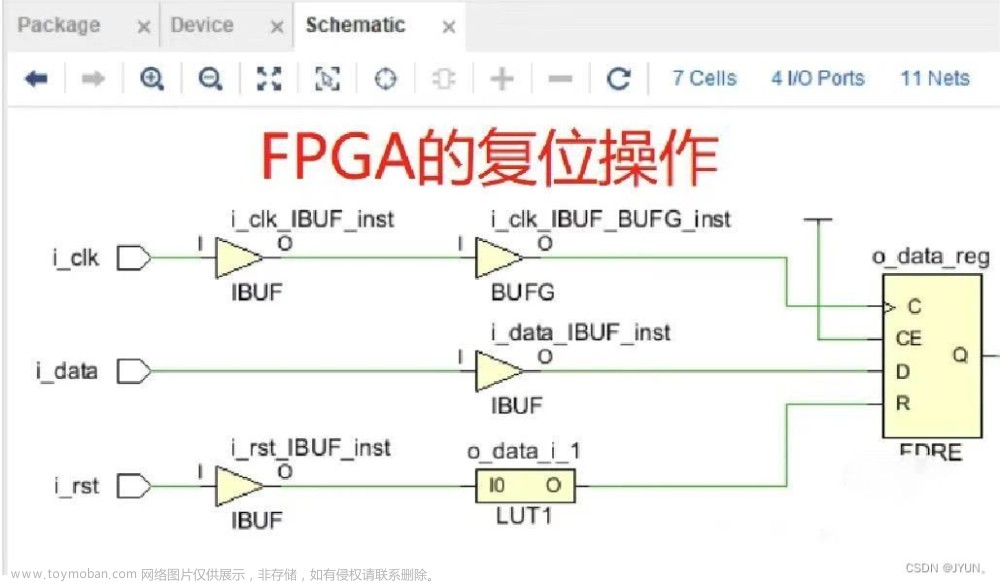

综合出的RTL如下

进行仿真测试(复位时间不足一个时钟周期、复位时间超过一个时钟周期、一个高频复位毛刺)

//------------------------------------------------

//--复位仿真

//------------------------------------------------

`timescale 1ns/1ns //时间单位/精度

//------------<模块及端口声明>----------------------------------------

module tb_rst_test();

reg clk ;

reg rst_n ;

reg in ;

wire out ;

//------------<例化被测试模块>----------------------------------------

rst_test rst_test_inst(

.clk (clk) ,

.rst_n (rst_n) ,

.in (in) ,

.out (out)

);

//------------<设置初始测试条件>----------------------------------------

initial begin

clk = 1'b0;

rst_n <= 1'b0;

in <= 1'b1;

#5

rst_n <= 1'b1;

#6

rst_n <= 1'b0;

#18

rst_n <= 1'b1;

#39

rst_n <= 1'b0;

#21

rst_n <= 1'b1;

#25

rst_n <= 1'b0;

#3

rst_n <= 1'b1;

end

//------------<设置时钟>----------------------------------------------

always #10 clk = ~clk; //系统时钟周期20ns

endmodule

1.2 同步复位的优缺点

优点:

- 有利于仿真器的仿真;

- 基本上没有亚稳态问题;

- 可以使所设计的系统成为 100%的同步时序电路,有利于时序分析;

- 由于只在时钟有效电平到来时才有效,对小的复位毛刺来说,时钟就像滤波器,所以可以滤除高于时钟频率的复位毛刺。

缺点

- 复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时由于线路上的延迟,可能需要多个时钟周期的复位脉冲宽度,且很难保证复位信号到达各个寄存器的时序;

- 大多数的FPGA的DFF(D flip-flop)都只有异步复位端口,采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样会耗费逻辑资源;

- 不是所有的库都有自带同步reset的FF, 但是可以通过把reset当作数据输入来解决;

- 如果电路中有三态总线,那么上电时必须用异步复位,如果用同步复位,reset必须能够复位三态信号的enable信号。如下所示

1.3 其他

同步复位编码方式必须是 if/else 优先级的方式,而且 reset只能放在 if条件下,其他组合逻辑放到 else逻辑下。

如果没有严格遵守这种方式,会有两个问题:

1、一些仿真器中,基于逻辑方程,逻辑可能阻止复位到达触发器。这只是一个仿真问题,不是硬件问题。但是复位的一个主要目的,就是仿真的时候将电路置于一个已知的确定状态。

2、由于复位树的高扇出,复位信号可能是一个相对于时钟周期的“延迟到达信号”,尽管复位将从复位缓冲区树中进行缓冲,但明智的做法是限制复位到达本地逻辑后必须经过的逻辑量。就是说必须对复位信号少做逻辑。

二、异步复位

异步复位:异步复位指的是无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

2.1 异步复位的实现方式

//*******************异步复位模块****************//

//-----------端口定义-------------------------------

module rst_test(

input clk , //系统时钟

input rst_n , //复位,低电平有效

input in , //输入信号

output reg out //输出信号

);

//-----------输出模块-------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

out <= 1'b0; //复位将输出置零

else

out <= in; //其他时候将输入赋值给输出

end

endmodule

综合出的RTL如下:

依然使用之前用的Testbench进行仿真,结果如下:

2.2 异步复位的优缺点

优点:

- 大多数目标器件库的dff都有异步复位端口,因此采用异步复位可以 节省资源

- 设计相对简单,异步复位信号识别方便,而且可以很方便的使用FPGA的全局复位端口GSR

- 电路reset和时钟无关,不管有没有时钟,都可以reset。 可以实时复位,也可以加在门控时钟里面。门控时钟是低功耗设计的重要方法。

缺点:

- 复位信号容易受到毛刺的影响

- 因为是异步逻辑,在复位阶段和解复位阶段(复位撤离)都是异步的。复位阶段不是问题,解复位才是问题。如果在触发器的活动时钟边缘或附近释放异步复位,则触发器的输出可能变为亚稳态,这样电路的复位状态可能会丢失,解复位失败。

三、异步复位同步释放

异步复位,同步释放就是指在复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。

3.1 实现

综合两种复位的优点,可以使用异步复位、同步释放设计,Verilog代码如下

//*******************同步复位模块**************************

//-----------端口定义-------------------------------

module rst_test(

input clk , //工作时钟

input rst_n , //复位,低电平有效

input in , //输入信号

output reg out //输出信号

);

//-----------reg定义-------------------------------

reg arst_n_r;

reg arst_n;

//-----------复位信号同步模块-------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

arst_n_r <= 1'b0 ; //复位将输出置零

arst_n <= 1'b0 ; //复位将输出置零

end

else begin

arst_n_r <= 1'b1 ; //跟接rst_n是一样的,都是逻辑1

arst_n <= arst_n_r ;

end

end

//-----------输出模块-------------------------------

always@(posedge clk or negedge arst_n)begin

if(!arst_n)

out <= 1'b0; //复位将输出置零

else

out <= in; //其他时候将输入赋值给输出

end

endmodule

综合出来的RTL视图和电路如下:

仿真结果:

可以看到:复位是异步进行的,一旦复位信号为低电平,则输出复位,而复位的撤除则被同步到了时钟域下。如此一来,既解决了同步复位的资源消耗问题,也解决了异步复位的亚稳态问题。其根本思想,也是将异步信号同步化。

3.2 优缺点

优点:

- 避免复位信号释放的时候造成亚稳态问题

- 只要复位信号一有效,电路就处于复位状态,与时钟沿无关

- 有效捕捉复位,即使是短脉冲复位也不会丢失

- 有明确的复位撤销行为,复位的撤离是同步信号,因此有良好的的撤离时序和足够的恢复时间

- 用两级触发器打两拍的方法解决亚稳态的问题

缺点:

- 由于异步复位和时钟无关,任何一个毛刺都可以引起复位。

3.3 其他

- 第一级触发器的数据端口是接电源,即高电平1’b1。

- 第一级触发器的输出,不能使用,作为过渡,因为仍存在亚稳态的危险。两级触发器做同步,是非总线信号的最常见异步处理方法。总线信号的异步处理方法,最常见的是异步fifo实现。

参考:

异步复位同步释放_异步复位,同步释放

复位电路设计(异步复位、同步释放)

RTL设计- 多时钟域按顺序复位释放文章来源:https://www.toymoban.com/news/detail-789508.html

异步复位同步释放原理文章来源地址https://www.toymoban.com/news/detail-789508.html

到了这里,关于FPGA | 深入理解复位的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!