接口总线相关

ITCM+ DTCM + Slave-AHB

“ITCM/DTCM + Slave-AHB” 描述的是一种特定的微控制器或处理器接口配置,通常用于嵌入式系统或微处理器设计。下面分别解释这些术语:

-

ITCM(Instruction Tightly Coupled Memory):指令紧密耦合存储器。这是一种专用内存,用于存储指令,其设计目的是为了提高处理器访问指令的速度。ITCM 通常位于处理器核心附近,可以提供非常低延迟的访问。

-

DTCM(Data Tightly Coupled Memory):数据紧密耦合存储器。与 ITCM 类似,DTCM 是专用于数据存储的内存,旨在加速处理器对数据的访问。它也通常位于处理器核心附近,以减少访问延迟。

-

Slave-AHB:这部分指的是一种特定的总线接口 - AHB(Advanced High-performance Bus)的从设备接口。AHB 是 ARM 架构中使用的一种高性能总线标准,用于连接不同的微处理器组件,如内存控制器、外设等。作为一个 Slave 设备,它意味着该接口能响应来自其他主设备(如处理器核心)的请求。

将这些组件结合在一起,“ITCM/DTCM + Slave-AHB” 描述的是一个配置,其中包括了专用于快速指令和数据存取的内存(ITCM 和 DTCM),以及一个作为 AHB 总线从设备的接口。这种配置通常用于需要高速数据和指令处理的嵌入式系统,特别是在对响应时间和效率有高要求的应用中,如实时系统或高性能微控制器。

Sys-AXI + 双AHB

“Sys-AXI/双AHB” 指的是一种包含两种不同类型总线架构的系统接口配置,具体为 AXI (Advanced eXtensible Interface) 和 AHB (Advanced High-performance Bus)。下面是对这两种总线架构的解释:

-

Sys-AXI(Advanced eXtensible Interface):AXI 是 ARM 架构中使用的一种高性能总线接口标准,属于 AMBA (Advanced Microcontroller Bus Architecture) 总线架构家族的一部分。AXI 设计用于高速、高性能的数据传输,支持高带宽和低延迟的通信。它通常用于连接处理器核心、内存控制器、外设等。

-

双AHB(Advanced High-performance Bus):AHB 同样是 ARM 的 AMBA 总线架构的一部分,被设计用于高性能的微控制器和嵌入式系统中。双AHB指的是系统中有两个 AHB 总线,这可能用于分离不同类型的数据流,例如一个用于处理器和内存之间的通信,另一个用于外设或其他功能模块。

在一个 “Sys-AXI/双AHB” 配置的系统中,可能会有以下特点:

- Sys-AXI 用于处理高速、大带宽的数据传输,如处理器与高速内存或高性能外设之间的通信。

- 双AHB 总线可能用于区分不同的数据流或操作,如一个 AHB 总线处理常规数据传输,另一个处理特定功能(如图形处理或加密通信)。

这种配置的目的通常是为了优化数据流,减少瓶颈,提高系统整体的性能和效率。在复杂的嵌入式系统或高性能微控制器设计中,这种多总线结构能够提供更灵活、高效的数据处理能力。

LLPP/AHB/APB

-

LLPP (Low-latency Peripheral Port):这是一种设计用来实现低延迟通信的外设端口。在嵌入式系统和微控制器应用中,LLPP 用于确保从外设(如传感器或执行器)到主处理器的数据传输具有最小的延迟。这对于实时应用和性能敏感的系统非常重要。

-

AHB (Advanced High-performance Bus):AHB 是一种高性能的系统总线,用于连接高带宽的组件,如处理器、内存控制器和一些高速外设。AHB 适用于那些需要快速、高效数据传输的应用。

-

APB (Advanced Peripheral Bus):APB 是一种用于连接低带宽和简单外设的系统总线,如定时器、接口控制器等。APB 的设计更简单,适合那些不需要高速数据传输的外设。

在“LLPP-AHB/APB”的配置中,LLPP 提供了一个专门的低延迟通道,用于连接对响应时间有严格要求的外设。与此同时,AHB 和 APB 分别处理不同类型和带宽要求的数据流和外设连接。这种配置提供了一个灵活和高效的解决方案,以满足不同类型的数据通信和外设接入需求,特别是在需要处理多种类型外设和数据流的复杂嵌入式系统或微控制器中。

中断相关

PLIC,128/256

PLIC,全称为"Platform Level Interrupt Controller",是一个平台级中断控制器,广泛用于基于 RISC-V 架构的系统中。PLIC 的主要作用是管理和处理来自各种外设的中断请求,确保正确、高效地向处理器传递这些中断。

PLIC 128/256中断的说明,

-

支持的中断数量:在这里提到的128/256中断指的是 PLIC 能够处理的中断源的数量。这意味着 PLIC 能够管理和分配来自128或256个不同源(如外设、定时器等)的中断请求。

-

中断优先级和向量:PLIC 支持为每个中断源设定优先级,这使得处理器能够根据重要性来选择处理不同的中断。在一些高级配置中,PLIC 还可能支持中断向量,允许直接跳转到特定的中断处理程序。

-

与处理器的交互:在接收到一个或多个中断请求后,PLIC 会根据设定的优先级和其他因素(如屏蔽状态)来决定哪个中断应该被送往处理器。处理器通过读取PLIC的寄存器来了解哪个中断源触发了中断,然后执行相应的中断服务程序。

-

配置和管理:PLIC 的配置通常通过写入其控制寄存器来完成,这包括设置优先级、启用/禁用中断等。这种配置可以在系统初始化时完成,也可以在运行时动态调整。

在基于 RISC-V 的系统中,具有高数量中断源的 PLIC 对于处理多样化和复杂的外部事件至关重要,尤其是在需要处理大量外设或在多任务环境下运行的应用中。通过有效管理中断,PLIC 有助于提高系统的响应性和可靠性。

定制中断延迟优化(自动保存恢复,咬尾)

定制中断延迟优化,特别是涉及到“自动保存恢复”和“咬尾”(tail-chaining)的技术,是嵌入式系统和微控制器中断管理中的高级特性。这些技术旨在减少中断处理的开销,提高系统的效率和响应速度。下面分别解释这些概念:

-

自动保存和恢复:在许多高级微控制器和处理器中,当中断发生时,系统会自动保存当前的状态,包括寄存器和程序计数器等。这样做的目的是保护当前执行环境,使得处理器可以切换到中断服务例程。完成中断处理后,系统会自动恢复这些状态,继续执行中断前的操作。这种自动化减少了编程的复杂性,并提高了中断处理的速度。

-

咬尾 (Tail-Chaining):咬尾是 ARM Cortex-M 系列微控制器中断处理的一个特性。当一个中断服务例程执行完毕,且在此期间发生了另一个中断请求时,处理器不会返回到原先的程序执行流程,而是直接跳转到下一个中断服务例程。这种机制减少了中断处理之间的空闲时间,提高了处理效率,特别是在多中断频繁发生的场景中非常有用。

-

定制中断延迟优化:这通常指的是根据特定应用和硬件配置对中断处理机制进行优化。例如,通过调整中断优先级,修改中断服务例程的处理逻辑,或使用先进的硬件特性(如上述的自动保存恢复和咬尾),以减少中断处理的延迟和开销。

这些优化技术对于实时操作系统(RTOS)和需要快速响应外部事件的应用来说至关重要。通过减少中断处理的延迟,系统可以更快地响应外部事件,提高整体性能和可靠性。

中断嵌套

中断嵌套是指在一个中断服务例程(ISR)执行期间,允许更高优先级的中断请求打断当前正在执行的中断服务。这种特性对于实现实时响应和高效的中断管理在嵌入式系统和微控制器中非常重要。以下是关于中断嵌套的一些关键点:

-

中断优先级:中断嵌套通常依赖于中断优先级的概念。在支持中断嵌套的系统中,每个中断源都被分配了一个优先级。当一个低优先级的中断正在被处理时,如果发生了一个更高优先级的中断,系统将暂停当前中断的处理,转而处理高优先级的中断。

-

上下文切换:当一个中断被另一个更高优先级的中断打断时,处理器会保存当前中断的上下文(包括寄存器等状态信息),然后开始执行更高优先级中断的服务程序。完成后,系统会恢复被中断的中断服务例程的上下文,继续执行。

-

减少响应时间:中断嵌套可以显著减少对高优先级事件的响应时间。在不支持中断嵌套的系统中,高优先级的中断可能需要等待当前中断处理完毕才能开始处理,这可能导致不必要的延迟。

-

复杂性管理:虽然中断嵌套提供了更灵活和高效的中断管理,但它也增加了系统的复杂性。开发者需要仔细管理和设计中断服务程序,以确保正确地处理多个中断和避免潜在的问题,如资源竞争或优先级反转。

-

实时操作系统(RTOS)的利用:在实时操作系统中,中断嵌套是一种常见的特性,用于提高系统的响应能力。RTOS 通常提供了用于管理中断嵌套和优先级的机制。

中断嵌套是高性能嵌入式系统设计中的一个关键特性,尤其是在需要快速响应多种外部事件的应用中,如工业控制、通信系统和高端消费电子产品。

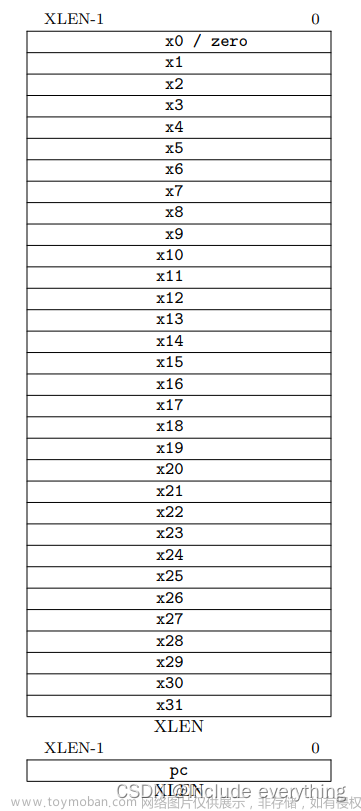

RISC-V MODE User/Machine

在 RISC-V 架构中,“User” 和 “Machine” 模式是两种不同的特权级别,它们定义了处理器在执行指令时的权限和能力。这些模式是 RISC-V 特权级架构的一部分,用于确保系统的安全性和稳定性。下面是对这两种模式的详细说明:

-

Machine Mode (M-Mode):这是 RISC-V 中最高的特权级别。Machine Mode 通常用于运行操作系统的内核,具有对处理器和系统资源的完全控制。它能够访问所有的硬件资源,并能执行任何指令。Machine Mode 主要负责系统的引导、硬件初始化、处理器异常处理和中断处理。由于它具有对硬件的完全访问权限,因此通常用于实现底层的安全和虚拟化功能。

-

User Mode (U-Mode):这是特权级别较低的模式,用于运行普通用户程序或应用。在 User Mode 下,应用程序的能力受到限制,无法直接访问关键的硬件资源。例如,它们不能直接操作内存管理单元(MMU)或处理中断。User Mode 的设计旨在保护系统免受恶意软件或程序错误的影响,并确保应用程序不能干扰其他程序或操作系统的正常运行。

RISC-V 架构中还可能包括其他模式,如 Supervisor Mode (S-Mode) 和 Hypervisor Mode (H-Mode),它们提供了不同级别的特权来支持操作系统和虚拟化功能。每种模式都被设计用来在系统的安全性、灵活性和性能之间达到平衡。例如,Supervisor Mode 用于运行操作系统的大部分组件,而 Hypervisor Mode 用于支持虚拟化。通过这种分层的特权级别设计,RISC-V 能够支持各种现代计算需求,从简单的嵌入式系统到复杂的多操作系统环境。

RISC-V Debug JTAG/cJTAG

在 RISC-V 架构中,两线调试接口是指提供了一种简化的调试方式,通常用于在硬件设计中实现高效且成本效率的调试方案。这里提到的“JTAG+两线cJTAG”指的是两种调试接口:

-

JTAG (Joint Test Action Group):JTAG 是一种常用的调试和测试接口标准,广泛应用于微控制器和其他集成电路的测试和调试。JTAG 接口通常包括四根或更多的线(TCK, TMS, TDI, TDO,以及可选的 TRST),允许进行设备编程、调试、和系统级测试。

-

cJTAG (Compact JTAG):cJTAG 是 JTAG 的一个简化版本,只需要两根线(通常是 TCK 和 TMSC)。cJTAG 旨在减少所需的物理连接数,以简化硬件设计和降低成本,同时保持与 JTAG 相似的功能。这对于小型化或成本敏感的设备特别有用。

在“两线Debug接口”的 RISC-V 系统中,开发者可以选择使用标准的 JTAG 接口或更简化的 cJTAG 接口进行调试。这种灵活性允许开发者根据他们的具体需求(如可用的物理空间、成本限制、调试需求的复杂性)来选择最合适的调试方法。

JTAG 和 cJTAG 提供的功能可能包括但不限于:

- 程序下载:将程序代码下载到目标设备。

- 断点设置:在程序执行中设置断点以便调试。

- 寄存器和内存访问:读写寄存器和内存内容。

- 执行控制:控制程序的执行,如开始、暂停和单步执行。

这些调试接口是嵌入式系统和微控制器设计中的关键组件,特别是在开发和维护复杂系统时。

四根或更多的线(TCK, TMS, TDI, TDO,以及可选的 TRST

JTAG (Joint Test Action Group) 接口通常包括四根或更多的线,这些线分别具有特定的功能,用于实现对目标设备的调试和测试。这些线包括:

-

TCK (Test Clock):测试时钟线。用于同步 JTAG 接口的操作。所有的 JTAG 指令和数据都是在 TCK 的边沿上进行传输的。

-

TMS (Test Mode Select):测试模式选择线。用于控制 JTAG 状态机的状态转换,以选择不同的操作模式,如数据传输、指令加载等。

-

TDI (Test Data In):测试数据输入线。用于向目标设备发送数据和指令。

-

TDO (Test Data Out):测试数据输出线。用于从目标设备接收数据。

-

TRST (Test Reset) [可选]:测试复位线。这是一个可选的线路,用于异步地将 JTAG 状态机复位到其初始状态。并非所有的 JTAG 实现都包括 TRST 线。

这些线路允许开发者对目标设备进行广泛的测试和调试,包括但不限于:

- 编程和配置:对设备进行编程或重新配置(例如,在 FPGA 上加载配置)。

- 调试:执行常规的调试操作,如设置断点、单步执行、检查和修改寄存器或内存值。

- 边界扫描测试:用于测试板级互连和芯片引脚。

JTAG 是一种非常强大的工具,广泛应用于电子系统设计、测试和调试领域。由于其标准化和灵活性,JTAG 成为了许多微控制器、数字信号处理器和其他集成电路设计的标准调试接口。

JTAG 如何实现

JTAG(Joint Test Action Group)是一种用于测试、验证和调试电子系统(尤其是集成电路)的标准接口。JTAG 接口主要基于一个名为 IEEE 1149.1 的标准,它定义了一种用于测试电路板和芯片的通信协议。以下是 JTAG 如何实现的关键方面:

硬件组成

-

JTAG 端口:包括至少四根线 - TCK(Test Clock),TMS(Test Mode Select),TDI(Test Data In),和 TDO(Test Data Out)。有时还包括第五根线 TRST(Test Reset)。

-

测试访问端口(TAP)控制器:这是 JTAG 设备内的一个小型状态机,用于解析通过 TMS 线收到的命令,并控制数据在 TDI 和 TDO 之间的流动。

-

边界扫描寄存器:用于访问芯片的引脚,允许测试芯片与外部世界的连接。

工作原理

-

状态机:TAP 控制器包含一个有限状态机,用于控制测试操作。TMS 线用于根据提供的时钟信号(TCK)改变状态机的状态。

-

数据传输:数据通过 TDI 线输入,经过各种寄存器(如指令寄存器或边界扫描寄存器),最后通过 TDO 线输出。

-

指令和数据传输:通过 TAP 控制器,可以将指令加载到指令寄存器中,同时可以将数据传输到和从设备的内部寄存器中。

使用场景

-

边界扫描测试:通过操作边界扫描寄存器,JTAG 可以测试芯片引脚之间的物理连接,这对于诊断焊接缺陷和电路板级问题非常有用。

-

设备编程和配置:JTAG 用于编程和配置可编程逻辑设备,如 FPGA 和 CPLD。

-

系统调试:在软件调试中,JTAG 允许访问处理器的内部寄存器,实现断点设置和单步执行等功能。

实现步骤

-

集成 TAP 控制器:在芯片设计中集成 TAP 控制器和必要的 JTAG 逻辑。

-

布线:在电路板设计中布置 JTAG 连接线,并确保所有需要测试的芯片都连接到 JTAG 链。

-

开发软件:使用或开发软件工具来与 JTAG 接口通信,执行测试和调试任务。

JTAG 的实现需要硬件设计师和软件工程师的紧密合作,以确保接口正确集成,并能与开发和调试工具兼容。

RISC-V JTAG

RISC-V 架构中的 JTAG 实现遵循通用的 JTAG 标准(IEEE 1149.1),但也引入了一些特定于 RISC-V 的功能,以支持更高效的调试。这些特性包括对处理器内核的直接访问、对寄存器的操作以及执行控制。以下是 RISC-V JTAG 实现的关键方面:

RISC-V JTAG 特性

-

处理器控制:允许对 RISC-V 处理器核心进行控制,包括暂停执行、单步执行以及访问和修改寄存器值。

-

系统级访问:提供对整个系统的访问,包括非处理器元件,如内存和外设。

-

断点和观察点:支持设置断点和观察点,用于调试软件。

-

自定义扩展:RISC-V 的开放架构允许在 JTAG 实现中加入自定义扩展,以支持特定的硬件或软件调试需求。

JTAG 接口

RISC-V 的 JTAG 接口包含了标准的 JTAG 引脚:TCK, TMS, TDI, TDO,以及可选的 TRST。此外,RISC-V JTAG 可能包括其他引脚,用于实现特定的调试功能。

调试模块

RISC-V 架构可能包括一个专用的调试模块,该模块通过 JTAG 接口与外部调试器通信。这个模块负责处理调试命令,如读取或写入寄存器、控制处理器执行等。

软件工具

为了使用 RISC-V 的 JTAG 功能,需要相应的软件工具,例如开源的 GDB(GNU调试器)与 RISC-V 相关的扩展,以及支持 RISC-V 的商业调试器。

实现步骤

-

硬件集成:在 RISC-V 处理器设计中集成 JTAG 接口和调试模块。

-

测试与验证:确保 JTAG 接口能够正确地与处理器和系统级资源进行通信。

-

软件支持:使用或开发软件工具以支持 RISC-V JTAG 调试功能。

RISC-V 的 JTAG 实现强调了灵活性和可扩展性,这与 RISC-V 架构的开放和模块化特性相一致。这种设计允许开发者根据他们的具体应用需求进行定制和优化。

RISC-V trace

RISC-V trace 是指在 RISC-V 架构中实现的追踪功能,用于记录处理器的执行过程,包括指令执行、数据访问、异常和其他重要的系统事件。这种追踪机制对于软件开发、调试、性能分析和系统验证至关重要。下面是关于 RISC-V trace 的一些关键点:

1. 追踪的目的

- 调试辅助:帮助开发者理解程序执行的具体情况,特别是在复杂的错误或不期望的行为出现时。

- 性能分析:通过收集执行数据,分析程序性能,识别瓶颈。

- 系统验证:在硬件设计和验证阶段,确保硬件行为符合预期。

2. 追踪的类型

- 指令追踪:记录执行的指令序列,包括分支、跳转等。

- 数据追踪:记录对内存的读写操作。

- 异常和中断追踪:记录异常和中断的发生和处理。

3. 追踪实现方式

- 专用追踪硬件:集成在处理器或系统中的专用硬件,用于捕捉和记录追踪数据。

- 软件追踪:通过软件工具和技术实现追踪,如插装代码。

4. RISC-V 追踪标准

- RISC-V 社区正在开发追踪标准,旨在定义一个通用的追踪接口和协议,以支持各种工具和环境。

5. 使用场景

- 开发和调试:帮助软件开发者和系统工程师调试和优化代码。

- 硬件设计验证:在硬件设计阶段验证处理器行为。

6. 工具和支持

- 通常需要专门的调试和分析工具来捕获、解析和显示追踪数据。

- 可能需要特定的硬件支持,如追踪端口或追踪缓冲区。

7. 面临的挑战

- 数据量:追踪可能会生成大量数据,需要有效的数据管理和分析技术。

- 性能影响:尤其是在软件追踪中,可能会对系统性能产生影响。

RISC-V trace开源相关

RISC-V trace 是一个不断发展的领域,随着 RISC-V 架构的日益普及,追踪技术的标准化和改进将对整个生态系统的发展产生重要影响。

RISC-V 架构的追踪功能(trace)还处于发展和标准化的阶段。尽管存在一些早期的实验性和开源实现,但一个统一和广泛认可的追踪标准尚未完全确立。以下是一些可能的开源实现和相关资源:文章来源:https://www.toymoban.com/news/detail-790194.html

1. RISC-V Trace Specification

- RISC-V International 正在努力制定一个追踪标准。这个标准旨在提供一个通用的框架来支持各种追踪需求。

- 官方文档和草案可能提供一些指导和实现参考。

2. 开源工具和实现

- Spike 模拟器:RISC-V 的官方指令集模拟器 Spike 可能包含一些基本的追踪功能,尽管它主要用于模拟和测试,而不是专门用于追踪。

- OpenOCD (Open On-Chip Debugger):OpenOCD 支持 JTAG 接口,可能包括一些用于 RISC-V 的追踪功能。

- 其他工具:一些其他开源项目可能包括对 RISC-V 追踪的实验性支持,但这些通常是社区驱动的,并且可能不完全符合未来的官方标准。

3. 社区和贡献

- RISC-V 社区是获取最新信息和资源的最佳场所。加入相关的邮件列表、论坛或贡献于开源项目都是深入了解和参与 RISC-V 追踪实现的好方法。

4. 自定义实现

- 一些组织或个人可能已经在自己的 RISC-V 实现中开发了定制的追踪解决方案,这些通常可以在其项目的源代码仓库中找到。

5. 学术和研究项目

- 学术界对 RISC-V 架构的研究可能包括追踪功能的开发,这些研究成果有时会以论文或开源代码的形式发布。

6. 文档和资源

- 查阅 RISC-V 相关的技术文档、规范和白皮书,这些通常是了解追踪实现的重要资源。

由于 RISC-V 是一个活跃发展的开源架构,相关的追踪实现和工具可能会不断更新和改进。因此,关注最新的社区动态和技术发展对于了解当前的最佳实践和工具是很有帮助的。文章来源地址https://www.toymoban.com/news/detail-790194.html

到了这里,关于RISC-V IP 相关概念的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!