深入浅出了解静态时钟分析和时钟约束

时序分析是什么?

我们提出一些特定的时序要求(或者说是添加特定的时序约束),使用特定的时序模型,针对特定的电路进行分析。分析的最终结果是要求系统时序满足我们提出的要求。

这么说可能还不是很清晰

我们进行一个对比 上次实验做的CORDIC算法

未添加时序约束时的频率利用率与功耗如下

我们可以看出这是一个非常大的占用率 甚至是 一个很恐怖的功耗(怎么不把板子烧了)

现在我们添加简单的时序约束

再次点击report Power 我们会发现 整体的 功耗瞬间降低了

我们通过这样的例子,可以很直观的通过时序约束找到优解

再举一个简单的例子

下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在 FPGA 内部经过一些逻辑延时和路径延时。我们的系统要求这个信号在 FPGA 内部的延时不能超过 13ns,而开发工具在执行过程中找到了下图所示的一些可能的布局布线方式。图中区域 1 的延迟是 5ns,区域 2 的延迟是 7ns,区域 3 的延迟是 5ns,区域 4 的延迟是 11ns。那么,怎样的布局布线能够达到我们的要求呢?仔细分析一番,发现所有路径的延时可能为 12ns(走路径 1)、16ns(走路径 3)、21ns(走路径 2 到路径 5)、17ns(走路径 2 到路径 4),只有 1 条路径能够满足要求,布局布线工具就会选择满足要求的路径 1。

下面介绍

什么是时钟抖动?

理想的时钟信号是非常完美的正弦波,但是实际晶振产生的正弦波是存在一些时钟抖动的。那么什么是时钟抖动呢?时钟抖动,英文名叫做 Clock Jitter,是相对于理想时钟沿实际时钟存在不随时间积累的、时而超前、时而滞后的偏移称为时钟抖动(时钟脉冲宽度发生暂时变化,也就是 T cycle【时钟周期】或大或小)。

什么是时钟偏差?

时钟偏差,Clock Skew,是指同一个时钟域内的时钟信号到达数字电路各个部分(一般是指寄存器)所用时间的差异。

时序分析的起点一般是源寄存器(reg1),终点一般是目标寄存器(reg2)。时钟和其它信号的传输一样会有延时的。下图中,时钟信号从时钟源传输到源寄存器的延时我们定义为 Tc2s,传输到目标寄存器的延时我们定义为 Tc2d。

时钟网络延时 Tskew 就是 Tc2d 与 Tc2s 之差,即 Tskew=Tc2d-Tc2s。

第一个方波是时钟源,第二个方波为时钟到达 REG1 时的波形,第三个方波为时钟到达 REG2 时的波形,从图上可以看出 Tskew 是时钟到达两个寄存器时的相位偏差。时钟偏差分为两类:正偏差和负偏差。当信号传输的目标寄存器在接收寄存器之前捕获正确的时钟信号,电路发生正偏差(也就是时钟布线方向与数据流水方向一致);反之,当信号传输的目标寄存器在接收寄存器之后捕获正确的时钟信号,电路发生负偏差(也就是时钟布线方向与数据流水方向相反)。

时钟约束 分析

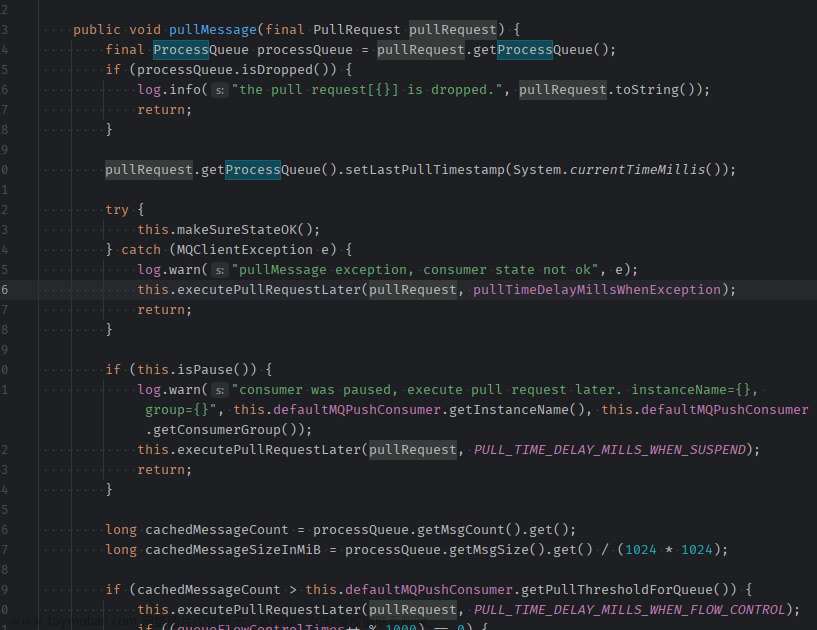

首先看懂时钟约束的代码

这两段代码是用于在数字电路设计的时候进行时钟约束的,通常用于 FPGA(可编程逻辑器件)的设计。这是基于Verilog/SystemVerilog语言的时钟约束代码。

1.第一段代码:

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} -add [get_ports sys_clk]

这段代码表示创建了一个时钟约束,指定了一个名为 sys_clk 的时钟信号。具体的含义如下:

- -period 20.000

- -name sys_clk

sys_clk

- -waveform {0.000 10.000}

- -add [get_ports sys_clk]

sys_clk

2.第二段代码:

create_clock -period 8.000 -name eth_rxc -waveform {0.000 4.000} -add [get_ports eth_rxc]

这段代码表示创建了另一个时钟约束,指定了一个名为 eth_rxc 的时钟信号。具体的含义如下:

- -period 8.000

- -name eth_rxc

eth_rxc

- -waveform {0.000 4.000}

- -add [get_ports eth_rxc]

eth_rxc

这些时钟约束对于数字电路设计至关重要,因为它们帮助工具确保设计在时钟频率范围内正常工作,并且在实现时满足时序要求。

接下来点击Design Timing Summary

第一个是 Setup 的最差情况(WNS),第二个是 Hold 的最差情况(WHS),第三个是 Pulse Width最差情况(WPWS)。蓝色字体下面的一行是总的 Setup 不满足总的分数(TNS),第二个是总的 Hold 不满足总的分数(THS),第三个是总的 Pulse Width 不满足总的分数(TPWS)。一般我们只关注 Setup 总的分数,分数是 0,说明时序是满足的,分数是负的,说明时序是不满足的,负分越大,说明时序越差,时序负分过大会导致功能可能出问题,所以我们的时序优化的效果可以参考负分的变化。

对于负值不满足要求的我们可以点击进入查看是哪一条路径不满足 查看是否可以优化

点击shematic 可以显示的更加直观

含有PLL模块的时钟其实在我们没看到的地方系统自动帮助我们生成了时钟约束了文章来源:https://www.toymoban.com/news/detail-790486.html

这是含有内部PLL模块的HDMI始终约束

因为在PLL端设定了HDMI传输模块时钟74M 内部编译是5倍频 文章来源地址https://www.toymoban.com/news/detail-790486.html

文章来源地址https://www.toymoban.com/news/detail-790486.html

到了这里,关于【【深入浅出了解静态时钟分析和时钟约束】】的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!