一、课程设计要求

1、学会应用数字系统设计方法进行电路设计;

2、进一步提高quartus II软件的开发应用能力;

3、提高VHDL进行综合设计的能力;

4、培养学生书写综合实验报告的能力。

二、课程设计要求与题目

2.1 课程设计要求

1、设计平台:quartus II+HH-SOPC-EP1C12 EDA/SOPC实验开发平台

2、设计方法:利用VHDL代码和/或原理图方法,采用层次化的方法进行设计(至少二层结构)。(功能分解)

3、结果验证:在实验开发平台上下载,验证设计的正确性,模块也需要仿真验证,给出仿真波形。

4、设计报告: A4纸打印,统一封面,封面格式见附件,简单装订。

2.2 课程设计题目

题目:多功能数字钟的设计与实现

1.能进行正常的时、分、秒计时,分别用6个七段数码管动态扫描显示时、分、秒。时时-分分-秒秒

2.利用按键开关快速调整时间(校准):时、分

3.通过按键开关设定闹铃时间,到了设定时间发出闹铃提示音,提示音长度为1分钟

4.通过按键开关设定倒计时的时间,通过开关启动/暂停倒计时,倒计时为0时发出提示音,提示音长度为1分钟

5.整点报时:

在59分50、52、54、56、58秒时按500Hz频率报时

在59分60秒时用1KHz的频率作最后一声整点报时

三、实验方案分析与设计

3.1 用户使用分析

多功能数字钟需要两个输出模块,一个是动态扫描数字显示,一个是蜂鸣器。

在使用体验上而言,多功能数字钟的输入模块主要有功能选择、置入时间等。

具有基础功能的数字钟是多功能数字钟的“枢纽”。除了倒计时功能,其余功能都与基础数字钟是离不开的。

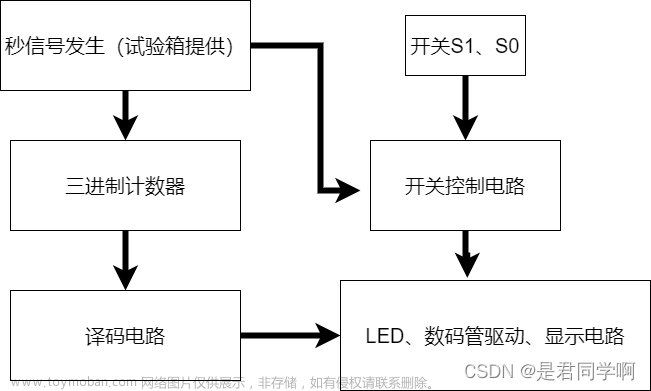

3.2 各功能所需模块分析

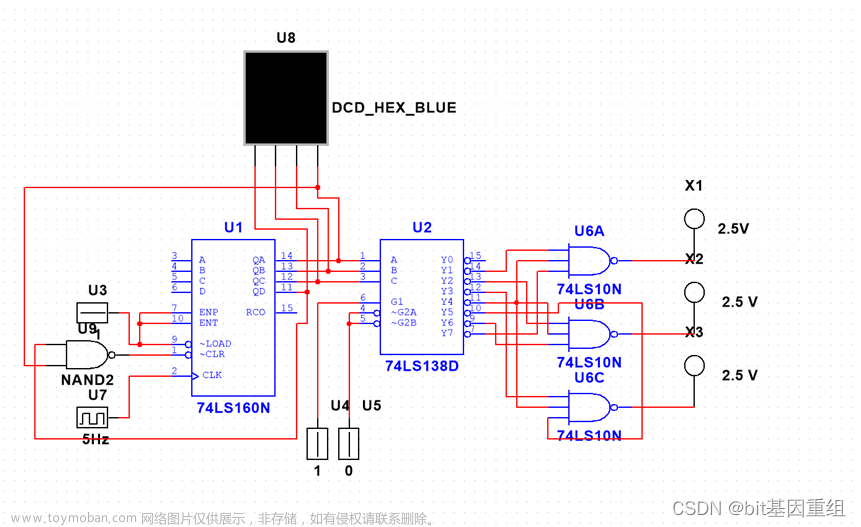

对于最基础的、能显示时间的数字钟功能,需要分频器、计数器、显示器模块。利用这三个模块,可以构成一个独立的、功能单一的数字钟。带调整时间功能的数字钟比起基础数字钟,引入了置数等输入。为了整点报时,我们引入了蜂鸣器模块,在计数器内部的相应状态下会有启动蜂鸣器的信号传给蜂鸣器。一个闹钟需要有调整时间、定时发出声响等功能,也需要一个比较器来比较当前时间是否和闹钟时间相等。倒计时模块相对独立,不需要基础数字钟的相关模块与功能。

3.3 完整电路图

将以上功能、模块集成整合后,我们便可以在quartus平台上做出完成的电路图。其中,有很大一部分模块、功能可以被有效地复用、集成。如各个功能下的动态扫描、蜂鸣器、置数等。所以,我们在设置输入端时,需要有几个输入端实现选择功能的作用。

3.4 管脚锁定

对于动态扫描显示模块,我们只需要正确地锁定位码和段码。管脚锁定图如下所示。sel是位码,seg是段码。

对于置数模块,我们需要4个输入作为8421BCD码输入,一个输入选择/退出置数模式,一个输入控制置入的是小时还是分钟,一个输入控制置入的是个位还是十位。

对于蜂鸣器模块,我们需要将蜂鸣器本身的输出引脚接到N6上。为了分清蜂鸣器准点报时、闹铃、倒计时的功能,我们设置了十二位LED灯显示模块上的输出。当报时、闹铃、倒计时使得蜂鸣器被触发时,相应的LED灯也会亮。A9的灯会在每个小时59分的50/52/54/56/58秒亮,同时蜂鸣器按500hz响。B9的灯会在每个小时0分0秒亮,同时蜂鸣器按1khz响。A10的灯会在倒计时结束时亮,亮一分钟,同时蜂鸣器响一分钟。B10的灯会在闹钟触发时点亮。

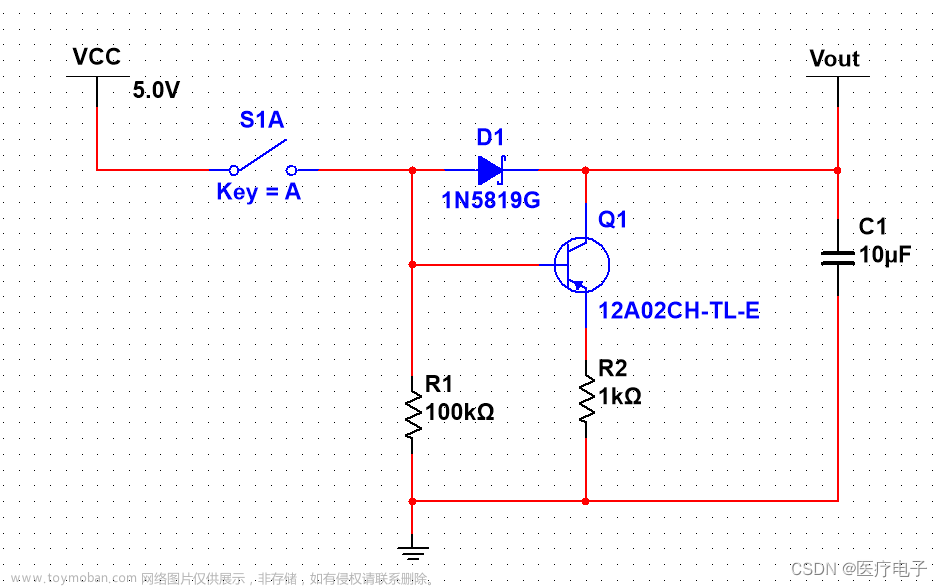

倒计时的使能、重置、置数可以独立设计,如图所示。

闹钟的置数功能的开关也需要单独设置

剩余的管脚锁定,从上到下依次为:蜂鸣器开关、1khz时钟信号、时钟的使能端、时钟的复位端。

以下是完整的引脚锁定图。

四、具体实现过程描述

4.1 分频器

分频器输入1khz的时钟信号,并输出成1hz的时钟信号和一个500hz的时钟信号。所以,我们设置两个内部信号,一个内部信号是值为0~999的整数,另一个内部信号的值只能是0和1。

每一个1khz时钟信号到来时,第一个内部信号的计数器+1,第二个内部信号的值翻转。

当第一个内部信号值在0-499之间时,对外输出0。当第一个内部信号值在500-999之间时,对外输出1。这个输出端输出的也是时钟信号,频率就是1hz。

第二个内部信号值为1时,对外输出1。第二个内部信号值为0时,对外输出0。这个输出端输出的也是时钟信号,频率是500hz。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity dev is

port(clk_1khz:in std_logic;--输入为1khz的时钟信号

clk_1hz:out std_logic;--输出为1hz的时钟信号,用于计数

clk_500hz:out std_logic);--输出为500hz的时钟信号,用于报时

end dev;

architecture beha of dev is

signal q1:integer range 0 to 999;--内部信号

signal q2:std_logic;--内部信号

begin

process(clk_1khz) begin

if clk_1khz'event and clk_1khz='1' then

if q1<500 then q1<=q1+1;clk_1hz<='0';--接收到1khz信号后计数,在0-499内输出0

elsif q1<999 then q1<=q1+1;clk_1hz<='1';

else q1<=0;

end if;

if q2='0' then q2<='1';clk_500hz<='0';--接收到1khz信号后翻转并输出

elsif q2='1' then q2<='0'; clk_500hz<='1';

else q2<='0';

end if;

end if;

end process;

end;

4.2 秒计数器

秒计数器与纯粹的60进制计数器略有区别。为了在每个小时的59分的50、52、54、56、58秒能报时,触发蜂鸣器的响声,所以在检测到相应的秒的值时需要给出一个输出信号alarm。其余信号如1hz的时钟信号、reset、使能端、数据输出、进位与60进制计数器相同。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity count_min is

port(

clk,rst,en:in std_logic;

cc:buffer std_logic_vector(7 downto 0);

co:out std_logic;

alarm:out std_logic--让蜂鸣器输出

);

end count_min;

architecture one of count_min is

begin

process(clk,rst)

variable mc1,mc0:std_logic_vector(3 downto 0);

begin

if rst='1' then --将秒的十位和各位都置成0

mc1:=(others=>'0');

mc0:=(others=>'0');

elsif clk'event and clk='1' then

if en='1' then--使能端为1,正常计数。否则,保持

mc0:=mc0+1;

co<='0';

alarm<='0';

if mc0="1010" then--个位是10,则十位进位

mc1:=mc1+1;

mc0:="0000";

end if;

if mc1="0101" and mc0="0000" then alarm<='1'; end if;--50秒

if mc1="0101" and mc0="0010" then alarm<='1'; end if;--52秒

if mc1="0101" and mc0="0100" then alarm<='1'; end if;--54秒

if mc1="0101" and mc0="0110" then alarm<='1'; end if;--56秒

if mc1="0101" and mc0="1000" then alarm<='1'; end if;--58秒

if mc1="0101" and mc0="1001" then--到59秒,给分钟计数器发一个使能信号

co<='1';

end if;

if mc1="0110" and mc0="0000" then--到60秒,则重置成0秒

alarm<='0';

mc1:="0000";

mc0:="0000";

end if;

else co<='0';

end if;

end if;

cc<=mc1&mc0;

end process;

end one;

4.3 分计数器

分计数器与纯粹的60进制计数器也略有区别。为了在每个小时的59分的相应秒数按500hz报时,在分钟的十位数为5且个位数为9时输出一个alarm信号。在每个小时的59分59秒,输出一个进位信号。这个进位信号不仅能触发小时计数器,而且能触发蜂鸣器的1khz报时。

置数时,有一个输入信号控制我们置的是十位还是个位。置数时,还有一个输入信号是4位的8421BCD码。置数功能自带对输入的有效性作检测。在个位,若检测到BCD码值为“1010”“1111”的无效值,则视为置入了9.在十位,若检测到BCD码值为“0110”“1111”的无效值,则视为置入了5,因为秒的十位数不能是6只能是5。

其余信号如reset信号、使能信号、时钟信号、数据输出,都与60进制计数器相同。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity count_h is

port(

clk,rst,en,ld:in std_logic;

alarmhigh:out std_logic;--报时输出

cc:buffer std_logic_vector(7 downto 0);

co:out std_logic;

ledagnum:in std_logic_vector(3 downto 0);--置入的8421BCD码

ledagpos:in std_logic--置数选择置十位还是置个位

);

end count_h;

architecture one of count_h is

begin

process(clk,rst,ld)

variable mc1,mc0:std_logic_vector(3 downto 0);

begin

if rst='1' then --复位信号,将分钟重置成0

mc1:=(others=>'0');

mc0:=(others=>'0');

elsif clk'event and clk='1' then

if ld='1' then--置数

if(ledagpos='1') then

if(ledagnum>="0110") then--置十位时,若置入大于6的数,则置5

mc1:="0101";

else

mc1:=ledagnum;--置入0~5的数,则正常置入

end if;

elsif(ledagpos='0') then

if(ledagnum>="1010") then--置个位时,若置入大于9的数,则置9

mc0:="1001";

else

mc0:=ledagnum;--正常置入

end if;

end if;

elsif en='1' then

mc0:=mc0+1;

co<='0';

alarmhigh<='0';

if mc0="1010" then--个位发生进位

mc1:=mc1+1;

mc0:="0000";

end if;

if mc1="0101" and mc0="1001" then

alarmhigh<='1';--到59分,则放出整点报时信号

end if;

if mc1="0110" and mc0="0000" then--到60分,则置为0分,进位,使小时计数

mc1:="0000";

mc0:="0000";

alarmhigh<='0';

co<='1';

end if;

else co<='0';

end if;

end if;

cc<=mc1&mc0;

end process;

end one;

4.4 小时计数器

小时计数器与纯粹的24进制计数器也略有区别。区别主要在置数上。置数时,有一个输入信号控制置的是十位还是个位。若置十位,则不能置入大于2的数。若置个位数,则不能大于9的数。在十位是2的情况下,也不能置入大于3的数,因为24以上的小时的值是不被允许的。

其余信号如reset信号、使能信号、时钟信号、数据输出,都与24进制计数器相同。

library ieee;

use ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.ALL;

entity count_24 is

port(clk,en,rst:in std_logic;

cc:out std_logic_vector(7 downto 0);

ledagnum:in std_logic_vector(3 downto 0);

ledagpos:in std_logic;

ld:in std_logic;

co:out std_logic);

end count_24;

architecture one of count_24 is

begin

process(clk,rst,ld)

variable mc1,mc0:std_logic_vector(3 downto 0):="0000";

begin

if rst='1' then --复位,将小时和分钟都置为0

mc1:=(others=>'0');

mc0:=(others=>'0');

elsif clk'event and clk='1'then

if ld='1' then

if(ledagpos='1') then

if(ledagnum>"0010") then--置数,小时的十位数大于2时视为置入2

mc1:="0010";

else

mc1:=ledagnum;

end if;

elsif(ledagpos='0') then

if(mc1="0010" and mc0>"0011") then--在20多小时,小时的个位数大于3时视为23时,个位置入3

mc0:="0011";

elsif(mc0>="1010") then

mc0:="1001";--bcd码值大于十时视为置入9

else

mc0:=ledagnum;

end if;

end if;

elsif en='1' then

mc0:=mc0+1;

if mc0="1010"then--在10小时、20小时

mc1:=mc1+1;

mc0:="0000";

end if;

if (mc1="0010")and(mc0="0100")then--在23小时,下一次就进位

mc0:="0000";

mc1:="0000";

co<='1';

else co<='0';

end if;

end if;

end if;

cc<=mc1&mc0;

end process;

end one;

4.5 闹钟设置器

闹钟设置器有时钟端clk,使能端en,置数端ld。输出端是两位8421BCD码。当使能端为0时,整个闹钟模块关闭。当使能端开启时,闹钟模块开启。当置数端为1时,闹钟会根据ledagpos信号选择置入十位还是个位。ledagnum为一位8421BCD码,为置入的数,输入无效时视为置入9。小时和分钟的值都需要一个闹钟设置器。闹钟设置器寄存了闹钟设定的时间。

library ieee;

use ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.ALL;

entity alarmsetter_m is

port(clk,en:in std_logic;

cc:out std_logic_vector(7 downto 0);

ledagnum:in std_logic_vector(3 downto 0);

ledagpos:in std_logic;

ld:in std_logic);

end alarmsetter_m;

architecture one of alarmsetter_m is

begin

process(clk,ld)

variable mc1,mc0:std_logic_vector(3 downto 0):="0000";

begin

if clk'event and clk='1'then

if en='0' then

if ld='1' then--置数

if(ledagpos='1') then

if(ledagnum>"0101") then--分钟的十位,最多只能置5

mc1:="0101";

else

mc1:=ledagnum;

end if;

elsif(ledagpos='0') then

if(mc0>="1010") then--个位,只能置0~9

mc0:="1001";

else

mc0:=ledagnum;

end if;

end if;

end if;

end if;

end if;

cc<=mc1&mc0;

end process;

end one;

4.6闹钟判断器

输入端为当前的小时数和当前的分钟数、闹钟设定的小时数和闹钟设定的分钟数。若它们对应相等,则对蜂鸣器输入信号。

library ieee;

use ieee.std_logic_1164.all;

USE ieee.std_logic_unsigned.ALL;

entity alarmjudger is

port(clk:in std_logic;

htime:in std_logic_vector(7 downto 0);--当前小时

halarm:in std_logic_vector(7 downto 0);--闹钟小时

mtime:in std_logic_vector(7 downto 0);--当前分钟

malarm:in std_logic_vector(7 downto 0);--闹钟分钟

alarmon:out std_logic);--输出

end alarmjudger;

architecture one of alarmjudger is

begin

process(clk)

begin

if clk'event and clk='1'then

if htime=halarm and mtime=malarm then--判断两两相等

alarmon<='1';

else alarmon<='0';

end if;

end if;

end process;

end one;

4.7 倒计时器

输入端有时钟、复位、使能、置数等,输出有两个8421BCD码表示的秒数、蜂鸣器开启信号。在最后的01秒,输出蜂鸣器开启的信号,以便在下一个时钟信号到来时蜂鸣器发出声音。设置了内部变量,使得倒计时计到0时开始计数,能从0计到60,能够控制蜂鸣器响的时间:60秒。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity countdown is

port(

clk,rst,en,ld:in std_logic;--时钟、复位、使能、置数

alarmout:out std_logic;--蜂鸣器开启

ledagnum:in std_logic_vector(3 downto 0);--设置置入的数

ledagpos:in std_logic;--设置置入十位还是个位

sout:out std_logic_vector(7 downto 0)--输出当前倒计时

);

end countdown;

architecture one of countdown is

begin

process(clk,rst,ld)

variable mc10,mc1:std_logic_vector(3 downto 0);

variable q1:integer range 0 to 100;--内部变量,

begin

if rst='1' then --复位,复位成99秒

mc10:="1001";

mc1:="1001";

q1:=0;

alarmout<='0';

elsif clk'event and clk='1' then

if ld='1' then

if ledagpos='1' then--置十位

mc10:=ledagnum;

end if;

if ledagpos='0' then--置个位

mc1:=ledagnum;

end if;

end if;

if ld='0' then

if en='1' then

if (mc1=1 and mc10=0) then--在最后01秒

alarmout<='1';

mc1:=mc1-1;

q1:=0;

elsif mc1=0 then

if mc10=0 then--在0秒,倒计时完成时

q1:=q1+1;--计数器,每秒+1,在计了60秒前输出蜂鸣器信号

if q1<59 then

alarmout<='1';

else

q1:=61;

alarmout<='0';

end if;

else mc10:=mc10-1;

mc1:="1001";--在十的倍数秒

end if;

else

mc1:=mc1-1;-在十的倍数秒

alarmout<='0';

end if;

end if;

else alarmout<='0';

end if;

end if;

sout<=mc10&mc1;

end process;

end one;

4.8蜂鸣控制器

蜂鸣控制器的输出端直接连接着蜂鸣器,输出一个频率信号使得蜂鸣器按这个频率发出声响。在每个小时的59分50/52/54/56/58秒,按500hz发出声响。在每个小时的0分0秒,按1khz发出声响。在闹钟设定的时间,按1khz发出声响。在倒计时结束时,按500hz发出声响。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xiang is

port(clk_500:in std_logic;

clk:in std_logic;

en:in std_logic;

alarmlow,alarmhigh,alarmco:in std_logic;

alarmbyalarm:in std_logic;

alarmbycountdown:in std_logic;

speaker:out std_logic);

end xiang;

architecture sss_arc of xiang is

begin

process(clk)

begin

if en='1' then

if (alarmlow='1' and alarmhigh='1' and alarmco='0') then

speaker<=clk_500;

end if;

if alarmco='1' then

speaker<=clk;

end if;

if alarmbyalarm='1' then

speaker<=clk;

end if;

if alarmbycountdown='1' then

speaker<=clk_500;

end if;

end if;

end process;

end;

4.9动态扫描显示器

动态扫描显示器有多个输入,包括时钟信号、小时值、分钟值、秒值。是否正在置数、正在置哪一位数、是否正在置闹钟、是否想显示闹钟、是否在倒计时、显示倒计时等判断都被集成到了动态扫描显示器中。输出有位码和段码,在1khz的时钟信号下,能够正确的输出对应数字。

若当前正在置数,我们则可以设置一个计数器范围为01000,当该变量值为0500时,对应位置的段码数值为无效值。当该变量值为500~999时,该对应位置的值为当前置入的数值。利用这种做法,我们可以做到:当前正在设置的设置的位置的数在闪烁。

正常情况下,动态扫描显示模块会显示当前时间。当我们调整闹钟时,拨动开关,动态扫描模块显示闹钟时间。当我们调整倒计时时,拨动开关,动态扫描模块显示倒计时时间。闹钟的显示优先级高于倒计时,倒计时显示优先级高于正常时间。

将8位8421BCD码传送至7段显示译码器,然后动态地显示在相应的显示器上。显示器显示的内容受段码和位码的控制,这就是动态扫描显示的原理。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity seltime is

port(clk:in std_logic;

h,m,s:in std_logic_vector(7 downto 0);

sel:out std_logic_vector(2 downto 0);

seg:out std_logic_vector(6 downto 0);

isledagging:in std_logic;

ledagpos:in std_logic_vector(2 downto 0);

isledaggingalarm:in std_logic;

alarmh,alarmm:in std_logic_vector(7 downto 0);

iscountingdown:in std_logic;

countdowns:in std_logic_vector(7 downto 0))

;

end seltime;

architecture beha of seltime is

signal scan_count:std_logic_vector(2 downto 0);

signal dat:std_logic_vector(3 downto 0);

signal q1:integer range 0 to 999;

begin

scan:process(clk)

begin

if clk'event and clk='1' then

scan_count<=scan_count+1;

q1<=q1+1;

end if;

sel<=scan_count;

if isledaggingalarm='1' then

case scan_count is

when "101"=>dat<=alarmm(3 downto 0);

when "100"=>dat<=alarmm(7 downto 4);

when "011"=>dat<=alarmh(3 downto 0);

when "010"=>dat<=alarmh(7 downto 4);

when others=>dat<="1100";

end case;

elsif iscountingdown='1' and isledagging='0' then

case scan_count is

when "111"=>dat<=countdowns(3 downto 0);

when "110"=>dat<=countdowns(7 downto 4);

when others=>dat<="1100";

end case;

else

case scan_count is

when "111"=>dat<=s(3 downto 0);

when "110"=>dat<=s(7 downto 4);

when "101"=>dat<=m(3 downto 0);

when "100"=>dat<=m(7 downto 4);

when "011"=>dat<=h(3 downto 0);

when "010"=>dat<=h(7 downto 4);

when others=>dat<="1100";

end case;

end if;

end process scan;

decode:process(scan_count) begin

if (isledagging='1' and scan_count=ledagpos and q1<500) then

seg<="0000000";

else

case dat is

when"0000"=>seg<="0111111";

when"0001"=>seg<="0000110";

when"0010"=>seg<="1011011";

when"0011"=>seg<="1001111";

when"0100"=>seg<="1100110";

when"0101"=>seg<="1101101";

when"0110"=>seg<="1111101";

when"0111"=>seg<="0000111";

when"1000"=>seg<="1111111";

when"1001"=>seg<="1101111";

when others=>seg<="0000000";

end case;

end if;

end process decode;

end beha;

4.10 其他辅助模块

地址位码解释模块。我们在输入时,选择位置是按如下办法:一个开关选择调整小时还是分钟,一个开关选择调整十位还是个位。利用这一位码解释模块,我们便能将我们置数的位置解析成位码传给动态扫描显示模块。

library ieee;

use ieee.std_logic_1164.all;

entity flasher is

port(inh,intt:in std_logic;

dataout:out std_logic_vector(2 downto 0));

end flasher;

architecture one of flasher is

begin

process(inh,intt)

begin

if(inh='1' and intt='1') then--小时的十位

dataout<="010";

end if;

if(inh='1' and intt='0') then--小时的个位

dataout<="011";

end if;

if(inh='0' and intt='1') then--分钟的十位

dataout<="100";

end if;

if(inh='0' and intt='0') then--分钟的个位

dataout<="101";

end if;

end process;

end;

输入合成模块,将4个二进制输入合成为一个8421BCD码

library ieee;

use ieee.std_logic_1164.all;

entity connector is

port(in3,in2,in1,in0:in std_logic;

dataout:out std_logic_vector(3 downto 0));

end connector;

architecture one of connector is

begin

dataout<=in3&in2&in1&in0;--将4位二进制数合成BCD码

end;

分配器,选择当前是在调整小时还是在调整分钟。

library ieee;

use ieee.std_logic_1164.all;

entity ledagger is

port(data:in std_logic_vector(3 downto 0);

posi:in std_logic;

ison:in std_logic;

datah:out std_logic_vector(3 downto 0);

datam:out std_logic_vector(3 downto 0));

end ledagger;

architecture one of ledagger is

begin

process(ison,posi)

begin

if (ison='1' and posi='1') then--调整小时

datah<=data;

datam<="0000";

elsif (ison='1' and posi='0') then--调整分钟

datam<=data;

datah<="0000";

else

datam<="0000";

datah<="0000";

end if;

end process;

end one;

五、结论实现效果

5.1 各模块仿真波形效果

对分频器模块进行波形仿真,我们可以看到:1khz的频率被分成了500hz的频率和1hz的频率。

对秒计数器模块进行波形仿真,我们可以看到:每分钟50/52/54/56/58秒输出报时信号,每分钟59秒给分计数器输出进位信号。

对分计数器进行波形仿真,我们可以看到:每小时59分输出报时信号,以与秒计数器的50/52/54/56/58秒输出500hz的蜂鸣声。每小时60分输出进位信号,以让小时计数器计数,并对蜂鸣器给出报时信号。

对小时计数器进行波形仿真。每记到23,便复位为0,并进位输出,表示一天已经过去了。

对闹钟判断器进行波形仿真。当闹钟设定时间与当前时间的小时与分都对应着相等时,输出信号1.

对倒计时器进行波形仿真。在秒数不为0时,正常往下递减秒数。在秒数为0时,对输出信号1,持续60秒。该信号连接蜂鸣器。如图,首先将倒计时置为11.在11秒后,输出信号1持续了60秒。这对应了倒计时结束时蜂鸣器响一分钟的功能。

对蜂鸣器进行波形仿真。可以看到蜂鸣器频率与其输入频率之间的关系。 文章来源:https://www.toymoban.com/news/detail-790702.html

文章来源:https://www.toymoban.com/news/detail-790702.html

5.2整体效果

在将编译完成的QuartusII工程文件下载到机箱后,多功能数字钟便开启运行。

将K1开关拨动到1,就可以看到电子钟开始正常的计时运行。点击S1按钮,便可以将时间重置成从0分0秒开始。

将K2开关拨动到1,就可以开启蜂鸣器。

在每个小时的59分的50/52/54/56/58秒,蜂鸣器按500hz响。在每个小时的0分0秒,蜂鸣器按1khz响。这就是整点报时功能。

将K3开关拨动到1,就开始了调整时间模式。K4开关可以控制用户调整的是小时还是分钟,K5开关可以控制用户调整的是个位数还是十位数。在调整时,相应位置的数字闪烁。K6/K7/K8/K9是从高到低的8421BCD码,通过K6~K9所表示的十进制数可以调节对应位置的时间。

K10开关可以显示闹钟。默认的闹钟时间是22:00。但是,将K3开关拨动到1时K10开关也拨动到1,就可以调整闹钟。调整闹钟的值的办法与上一段调整时间值的办法是一致的。当闹钟设置的时间就是当前时间时,响铃一分钟。

K11开关可以显示倒计时。默认从99秒开始倒计时。将K12开关拨动到1,就可以调整倒计时的时间,调整办法与上文一致。按S2按钮可以重置倒计时。当倒计时为0时,响铃一分钟。文章来源地址https://www.toymoban.com/news/detail-790702.html

到了这里,关于数字逻辑电路设计课程设计的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!