名称:基于EDA的电烤箱控制器设计Verilog代码Quartus 新起点FPGA开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

基于EDA的电烤箱控制器设计

主要研究内容

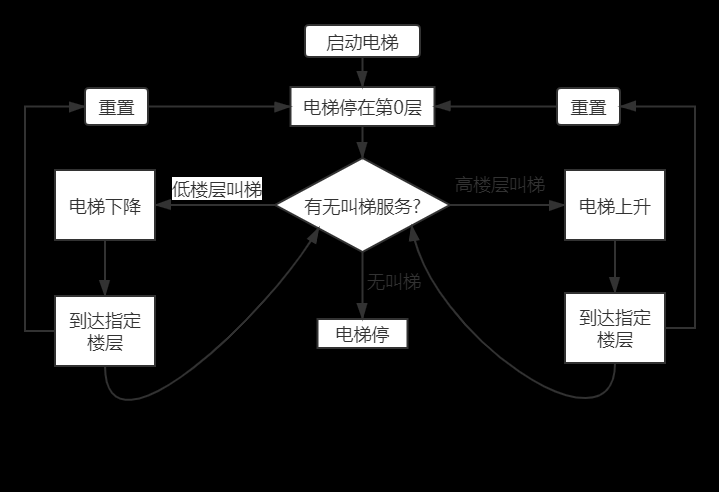

设计一个电烤箱控制器电路,要求具有三档加热功能,分别表示烧烤加热为低火、中火、高火。具有复位开关、启动开关;能够进行烧烤加热的时间设置,同时显示烧烤加热时间;当烧烤加热计时到时间为0则断开烧烤加热器,给出声音提示。具有计时、温度控制、音效提示等等、显示模块涉及到显示译码和指示灯的闪烁。

主要技术指标

本设计要求

(1)三档烧烤加热功能,具有复位开关、启动开关。

(2)能够进行烧烤加热的时间设置、显示,加热计时到时间为0则断开加热器,给出声音提示。

(3)硬件电路设计必须自选合适芯片和元件,绘制硬件电路原理图和

PCB版图。

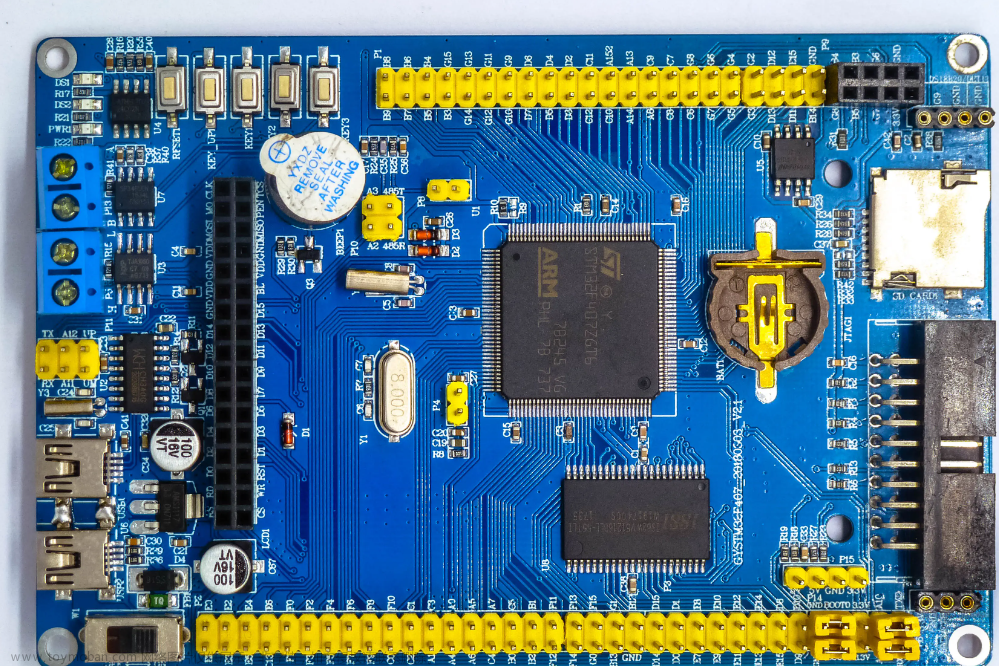

本代码已在新起点FPGA开发板验证,新起点FPGA开发板如下,其他开发板可以修改管脚适配:

1. 工程文件

2. 程序文件

3. 程序编译

4. 仿真文件(VWF文件)

5. 仿真图

部分代码展示:文章来源:https://www.toymoban.com/news/detail-791128.html

module LED_DISP( input clk,//50MHz output clk_out, input [3:0] minute_ten_display,//分钟 input [3:0] minute_one_display,//分钟 input [3:0] second_ten_display,//秒钟 input [3:0] second_one_display,//秒钟 output [5:0] LED_BIT, output [7:0] LED_SEG ); reg [31:0] count=32'd0; //分频到400Hz,计数125000,用于数码管刷新频率 always@(posedge clk) begin if(count>=32'd125000)//仿真减小为125,本应125000 count<=32'd0; else count<=count+32'd1; end assign clk_400Hz=(count>=32'd62000)?1:0; assign clk_out=clk_400Hz; reg [5:0] bit_select;//数码管位选 reg [7:0] seg_select;//数码管段选 reg [3:0] display; reg [2:0] geshu = 3'd0; 位选 always @(posedge clk_400Hz ) begin if(geshu == 3'd5)//6个数码管 begin geshu <= 3'd0; end else begin geshu <= geshu + 1'd1; //扫描那个管子的指示位 end end always @(posedge clk) //位选切换 begin case (geshu) 3'd0: begin bit_select<=6'b011111; display<= second_one_display; end 3'd1: begin bit_select<=6'b101111; display<= second_ten_display; end 3'd2: begin bit_select<=6'b110111; display<= minute_one_display; end 3'd3: begin bit_select<=6'b111011; display<= minute_ten_display; end 3'd4: begin bit_select<=6'b111111; display<= 4'd0; end 3'd5: begin display<= 4'd0; bit_select<=6'b111111; end default:; endcase end

源代码

扫描文章末尾的公众号二维码文章来源地址https://www.toymoban.com/news/detail-791128.html

到了这里,关于基于EDA的电烤箱控制器设计Verilog代码Quartus 新起点FPGA开发板的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!