Matlab 生成二进制、十六进制数据

在使用Vivado软件进行Verilog程序仿真时可能需要对模块输入仿真的数据,因此我们需要一个产生数据的方法(二进制或者十六进制的数据),Matlab软件是一个很好的工具,当然你也可以使用VS等工具。

以下分别给出了使用Matlab模拟产生二进制和十六进制数据的例子,例子仅供参考。

生成二进制数据

Fs=100; %采样率1ns一个点

%t=0:1/Fs:63/Fs; %数据时长:64个采样周期

N = 128;

n = 1:N;

t = n/Fs;

%% 生成测试信号

f1 = 10;

f2 = 30;

s1 = cos(2*pi*f1*t);

s2 = cos(2*pi*f2*t);

signalN = 2 + s1 + s2 ;

data_before_fft = 10*signalN; %系数放大100倍

%% 把数据写到txt里面,让fpga调用

fp = fopen('data_before_fft.txt','w');

for i = 1:N

if(data_before_fft(i)>=0)

temp= dec2bin(data_before_fft(i),16);

else

temp= dec2bin(data_before_fft(i)+2^16+1, 16);

end

for j=1:16

fprintf(fp,'%s',temp(j));

end

fprintf(fp,'\r\n');

end

fclose(fp);

%% 绘制fft信号

plot(data_before_fft);

y = fft(data_before_fft,N);

y = abs(y);

f = n*Fs/N;

plot(f,y);

生成十六进制数据

clc;clear;close all;

format long g

Fs = 1000; % Sampling frequency

T = 1/Fs; % Sampling period

L = 1000; % Length of signal

t = (0:L-1)*T; % Time vector

x1 = cos(2*pi*50*t)*(2^13); % First row wave

%output time domain data

x1_fix = round(x1,0); %convert to fixed signed(3.13)

x1_fix(find(x1_fix<0)) = x1_fix(find(x1_fix<0))+(2^16);

fid0 = fopen('time_domain_cos.txt', 'wt');

fprintf(fid0, '%16x\n', x1_fix);

fid0 = fclose(fid0);

Vivado 读取二进制、十六进制数据

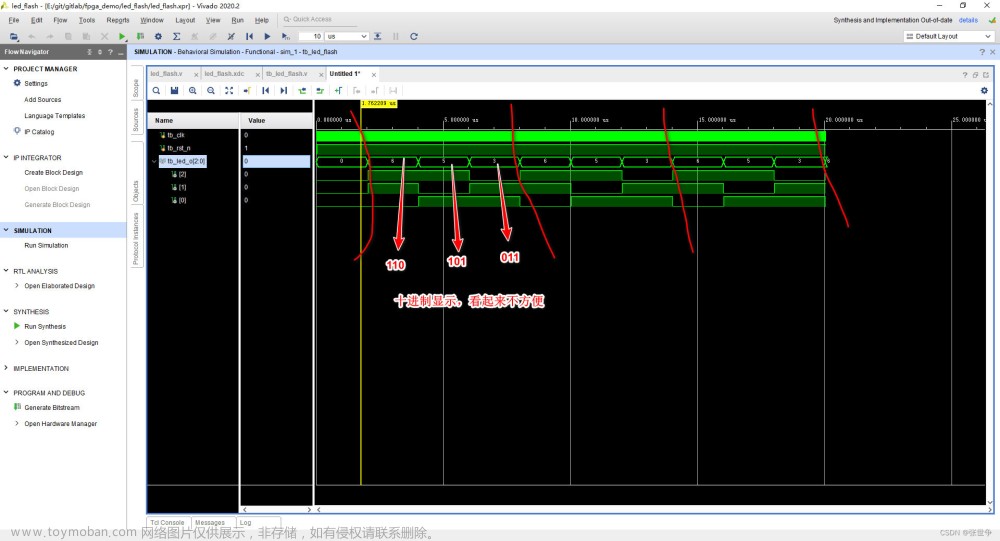

Vivado小白(俺本人)可能不会读取txt文本数据,以下为Verilog语言实现的txt数据读取,二进制使用的程序指令为readmemb, 而读取十六进制的程序质量为readmemh,b, h 就是代表二进制和十六进制。

$readmemb("E:/LiangWF22/FPGA_Project/FFT3/data_before_fft.txt",Time_data_I);//二进制

$readmemh("E:/LiangWF22/FPGA_Project/FFT_IFFT1/time_domain_cos.txt", data_mem);//十六进制

Vivado保存仿真结果数据

小白刚开始时不知道如何将Vivado仿真出来的结果保存下来,而且发现网上关于FPGA的教程很少,特写下此记事,方便以后自己重新使用这些代码片。

将程序里的路径改一下和fft_abs换成你自己需要保存的变量就可以了,应该。

//保存数据

integer dout_file;

reg dout_valid;

initial begin

//dout_file = $fopen("E:/FPGA/FFT/data.txt");

dout_file = $fopen("E:/LiangWF22/FPGA_Project/FFT3/data.txt");

if(dout_file==0)begin

$display ("can not open the file!");

$stop;

end

end

always @(posedge clk) begin

$fdisplay(dout_file,"%d",$signed(fft_abs));

end

另外还可这样子保存, 网上的大佬就是厉害,向各位大佬学习。文章来源:https://www.toymoban.com/news/detail-791166.html

always #10 clk = ~clk;

integer w1_file,w2_file;

initial w1_file = $fopen("E:/LiangWF22/FPGA_Project/FFT_IFFT1/fft_result_real.txt","w");

initial w2_file = $fopen("E:/LiangWF22/FPGA_Project/FFT_IFFT1/fft_result_image.txt","w");

always @(posedge clk)

begin

if(m_axis_data_tvalid)

begin

$fwrite(w1_file, "%x\n", m_axis_data_tdata_real);

$fwrite(w2_file, "%x\n", m_axis_data_tdata_img);

$display("%x , %x",m_axis_data_tdata_real,m_axis_data_tdata_img);

end

end

Forever young,always tearful.文章来源地址https://www.toymoban.com/news/detail-791166.html

到了这里,关于【FPGA仿真】Matlab生成二进制、十六进制的txt数据以及Vivado读取二进制、十六进制数据并将结果以txt格式保存的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!