XILINX

- PACKAGE

一般在doc nav搜索,同样也可以在官网;检索关键字“*pkg-pinout.”

比如vu9p:

ug575-ultrascale-pkg-pinout.pdf

- 原理库文件

Package Files Portal

举例:

先选封装; 再选器件

再选器件

二维交叉检索后,在右击另存即可。《xczu48drffvg1517pkg.txt》。

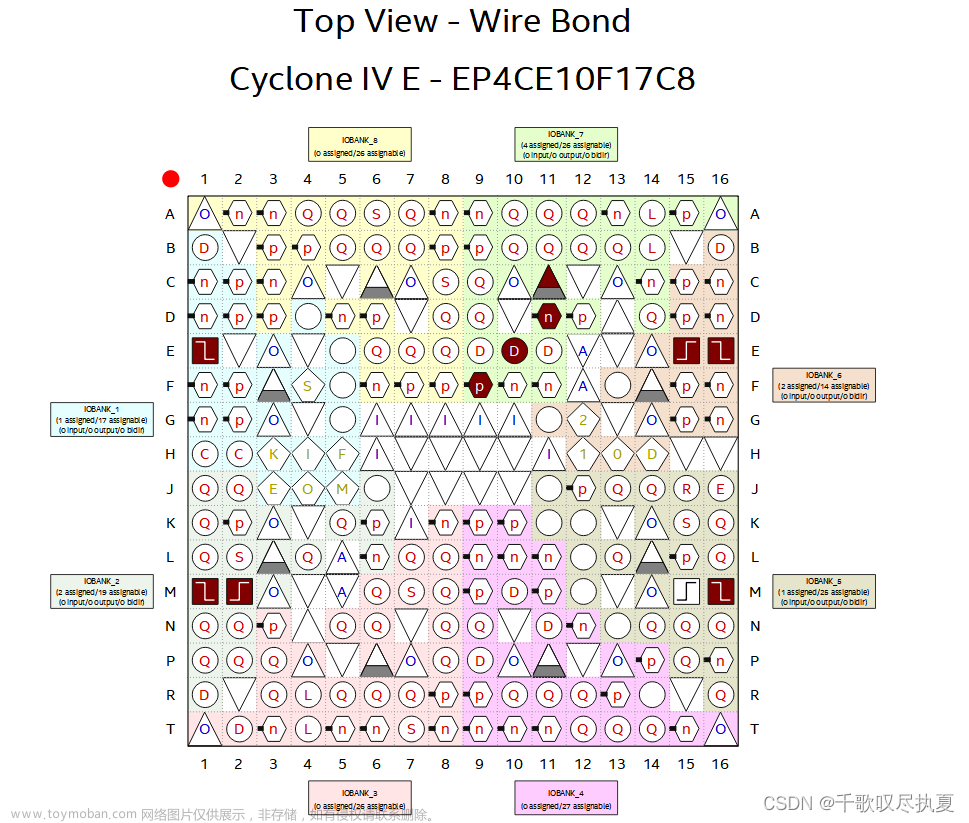

ALTERA

-

PACKAGE

蓝厂、Altrea package 下载地址 -

库文件

Mentor Graphics -

其他硬件设计资料

电路板开发人员中心文章来源:https://www.toymoban.com/news/detail-791903.html -

举例

点击右上角的【下载】就得到了需要的OLB文件;

文章来源地址https://www.toymoban.com/news/detail-791903.html

文章来源地址https://www.toymoban.com/news/detail-791903.html

到了这里,关于【 FPGA 封装设计资源 】 Xilinx vs Altera的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!