1 问题背景

最近在开发的过程中遇到了一个关于RGMII通信非常少见的问题,通过与硬件同事将近一个月的排查,终于定位到了问题,现在对问题的排查过程大致做一个复盘记录。我们的产品采用了NXP的SJA1105Q系列交换机,与交换机相连的PHY芯片采用了MARVELL的88Q2120千兆车载PHY。这个网络方案在我们其他产品开发中已经算得上应用的比较成熟的方案了,但是在这次的开发中出现了交换机到phy能够ping通,一旦将产品接上思博伦打流测试仪进行打流测试,思博伦与88Q2120相连的port就会出现反复 link down 然后link up的现象,并且此时双向速率只有不到1.5G,88Q2120的RX方向出现了大量丢包。

2 问题排查

通过打流测试判定目前异常通路为:千兆PHY----SJA1105----88Q2120

此时通过与硬件工程师讨论,大致得出了以下几个判断:

- phy是一个被动芯片,是内核对交换机配置存在问题,导致交换机MAC端发出的125M时钟或TX信号不稳定导致phy出现了速率不稳定以及link down

- phy 周围的包括25M晶振和其他硬件信号出现异常,导致PHY的工作状态异常

针对第一个判断:

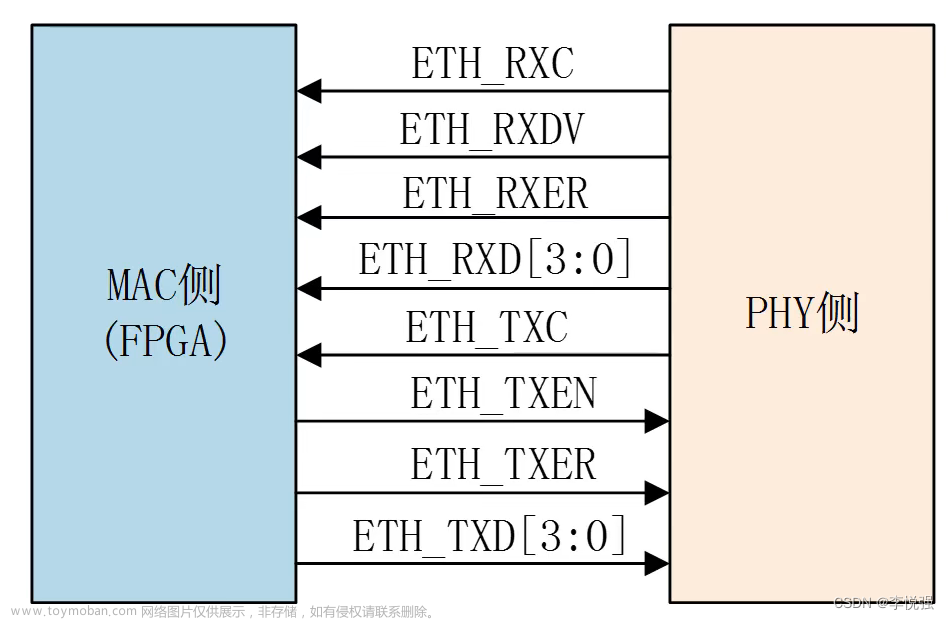

我又重新检查了内核关于交换机端口的配置,并且确保交换机配置已经写进去,spi信号正常。接下来在硬件的协助下又对MAC到phy的时钟以及tx 信号进行了排查,均未发现异常。

针对第二个判断:

硬件同事将phy周围的晶振信号以及电流逐一进行了排查,可能异常的都更换了,但是仍然没有任何效果。

此时,针对上面两个判断基本都pass了。

后面通过和硬件再次沟通,从交换机MAC到PHY的RGMII是采用了等长走线,并且,PHY端的RXC=1,TX和RX均配置了延时,同样的配置在其他板子上都是正常的。后来找到了一块其他产品正常的板子,硬件量取PHY周围的信号进行对比,也并未发现问题。此时我便开始有点怀疑是否是这批板子在RGMII走线部分打板质量有问题?但并没有直接的证据证明,因此继续排查。

后来硬件将SJA1105Q系列换成了SJA1105T交换机,此时发现,通信竟然正常了,但这个现象也更加让我疑惑了,为什么更换了交换机就可以呢?难道RGMII走线没有问题?难道真实交换机MAC配置存在问题?针对这一连串突入起来的问号开始查阅手册资料,再次检查代码。

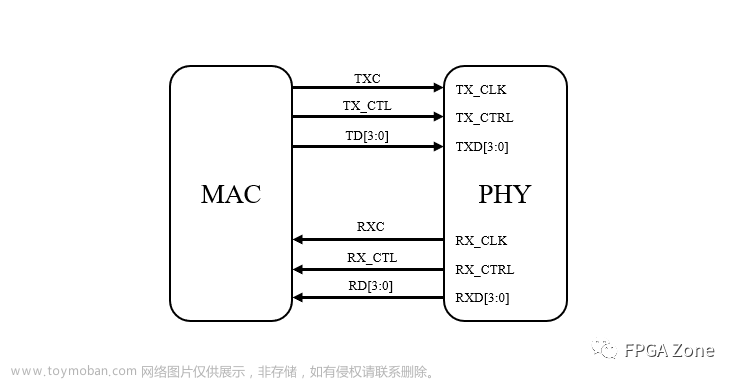

通过对比SJA1105手册发现,SJA1105Q为SJA1105T的升级版本,增强功能之一就是SJA1105Q遵循RGMII V2.0规范时序,而SJA1105T遵循RGMII V1.3时序。

通过对比SJA1105手册发现,SJA1105Q为SJA1105T的升级版本,增强功能之一就是SJA1105Q遵循RGMII V2.0规范时序,而SJA1105T遵循RGMII V1.3时序。

RGMII V1.3规范需要外部延时,通过PCB走线实现或对端设备支持配置延时实现;

RGMII V2.0规范较V1.3增加了内部配置时钟延时的功能。

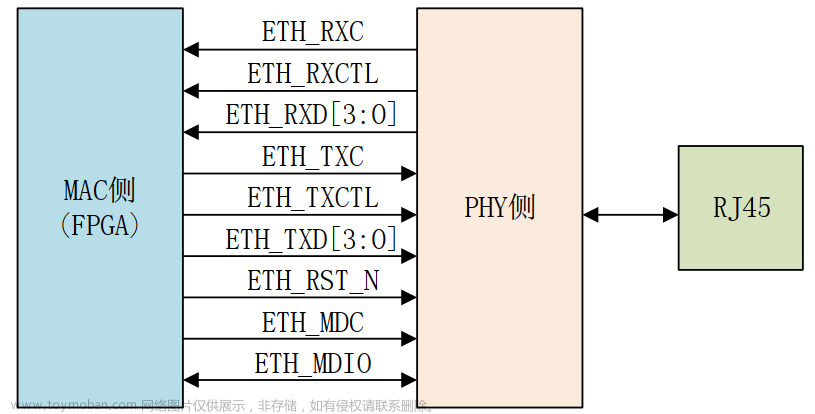

为了验证上面的疑惑,硬件将Phy端的RXC下拉改为上拉,此时phy端tx延时=0,rx延时仍然保留。软件通过操作交换机寄存器对MAC端配置tx延时,经过多个不断的调试,发现tx延时2.2ns左右时,通过硬件量取波形发现基本为最佳延时。

但此时通过iperf 测试速率发现,从交换机到phy的上行平均速率虽然从之前的几十Mbits/s提升到了600-700Mbits/s,但仍然不正常,并且伴随着采样速率起伏过大,不稳定的现象。

保持在2.2ns延时情况下,随后我又对交换机打流的两个port进行了流量统计,读取了交换机关于port丢帧以及crc error的寄存器,发现打流的两个port都tx 和rx 方向都没有出现大量丢包的现象,状态寄存器也没有报错。因此基本排除交换机端口转发丢包CRC报错导致RGMII速率不稳定。

排除了以上mac配置的问题,再次对板子进行打流测试,发现此时速率已经可以提升到1.8G左右,但是仍然会伴随link down以及rx方向丢包的问题。此时读取phy的寄存器,发现phy仍然报rx线上错误以及link down。

后来,硬件同事又将这块异常的板子与另外一块正常的板子进行交叉飞线,即将问题板子的phy飞到正常板子的交换机上,将正常板子的phy飞到问题板子的交换机上,并且为了彻底排除内核注册phy device时对phy寄存器操作导致的异常,将SOC到phy的mdio也断掉了,最终通过打流测试两种情况均正常。

到目前为止已经基本验证,驱动方面对交换机配置是没有问题的。后来硬件尝试在同一块板子上将原来在port4的88q2120飞线到port2,发现link down 以及速率异常的问题也没有了。至此,可以确定问题根源在于交换机port4至88q2120这段RGMII上。后续还原单板,更换RGMII线上串阻测试。

硬件去除飞线后,还原板上33Ω串阻,打流复现link down问题,速率1.8G-1.9G。将12个串阻由33Ω更换为0Ω,link down问题依旧存在,且速率降为1.4G。再将阻值更换为22Ω,link down问题依旧存在,但速率由1.4G升至1.6G。考虑是否阻值较大,信号质量较好?于是将阻值更换100Ω,打流10秒钟发现思博伦不再闪红灯,速率达到2G,且不丢包。

3 问题总结

阻抗匹配是为了防止信号反射的。将终端反射回来的信号吸收,防止在源端再次发生发射。

具体可以参考:高速数字信号线上添加33欧电阻的作用_ArthurBruin的博客-CSDN博客_串联33欧姆电阻作用文章来源:https://www.toymoban.com/news/detail-792291.html

大致总结一下问题排查的过程,从一开始怀疑phy的状态异常,对phy进行排查,到后来对mac进行排查,一直都很少怀疑真的是中间的RGMII通路某些部分出了问题,并且从飞线发现通信正常的时候,就应该怀疑大概率就是阻抗的问题了,飞线线阻要大于PCB走线线阻。通过分享这次记录,希望能给各位开发者在解决此问题时能有所帮助。文章来源地址https://www.toymoban.com/news/detail-792291.html

到了这里,关于硬件阻抗不匹配导致的RGMII通信异常问题的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!